-

Постов

21 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о skkap

-

Звание

Участник

- День рождения 01.08.1989

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

-

Кондер от просадки U

skkap опубликовал тема в В помощь начинающему

Есть устройство USB(самодел). Переподключается само, очевидно от просадки напряжения (в моменты пиковой нагрузки). Надо поставить кондер , но незнаю какой. 2200uF 10V, подойдет? Как расчитывать? спасибо -

Собираю устройство - USB джойстик на ATmega8 с программным USB от (Obdev V-USB). С самой схемой вопросов не возникло, но вот в качестве датчиков нажатий служат пьезоэлементы (На самом деле барабаны ФОРМАНТА, но по сути пьезоэлемент с выходом на TRS коннектор). Соответственно обычным аудиокабелем (моно) соединяю этот барабан с контроллером по следующей схеме: Инвертор потому что контроллер запрограммирован понимать обратную логику (перекомпилировать лень.) и для улучшения качества сигнала перед контроллером. Резистор уменьшает время импульса (эксперементально). Теперь о проблеме: Ударяю по барабану, проходит импульс и дальше начинается дребезжание постоянное в канале (кнопка постоянно нажата), пока не дернешь питание устройства. Удивительным образом, когда подключаю щуп осциллографа - все начинает работать как надо, один удар один импульс! Убираю щуп - опять все не работает. Подскажите в чем может быть дело?

-

Спасибо всем за ответы! Нашел решение своей проблемы, хоть и кривое. При первом билде (когда полностью билдится syslib) всегда вылазят ошибки, причем сааамые разные. После этого повторный билд проходит в основном без ошибок (то есть то нету ошибок - чудеса). Ну жаловаться не на что, совместимость не заявлено - потому работаем как можем. Радует факт, что это похоже все таки из-за ОС, а значит Win7 XP mode все гарантированно исправит, проверю позже. А сейчас пользуясь вашим вниманием, задам несколько вопросов. 1. Собрал систему с UART приемопередатчиком. Запись в stdout происходит отлично посредством функции printf, но чтение никак не пойму.Везде в доках altera говорят о полной совместимости по потокам с ANSI C. Что же на деле? Не знает такой функции, как и fopen, fclose, ... Как читать из порта? Подскажите пожалуйста :) 2. Вопрос про время компиляции. Как его сократить? что делаю я: правлю код, компилирую проект (бегающий огонек около минуты), компилирую проект quartus (минута), прошваю. Это нормально? Совсем не привык к таким задержкам, программирую много и давно, но такого не видел :/ 3. Где вообще почитать про программирование в этой IDE с этими библиотеками и компилятором. Т.к. множество привычных функций нет, а куча всяких неизвестных мне IOWR_ALTERA_AVALON_PIO_DATA присутствует. Находил много кода по форумам, функции из них компилятор не признает. Буду благодарен за куски полезного кода и примеры. Спасибо :)

-

NIOSII IDE - ошибки компиляции

skkap опубликовал тема в Работаем с ПЛИС, области применения, выбор

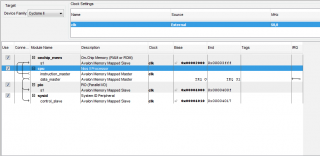

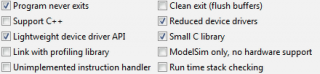

Опишу ситуацию и свою последовательность действий. Необходим проект на NIOS II, включающий работу с PIO и внешним UART. Все это собирается на циклоне2 на стартер ките "Alter Cyclone II FPGA Starter Board". Для начала решил просто помигать светодиодами. 1. Создаю проект в квартус 9.0, указываю конкретную модель второго циклона (неоднократно создавал проекты под этот девайс и прошивал, все всегда было отлично). 2. Вызываю SOPC билдер и добавляю: - on-chip память 8192 bytes - cpu NIOS II / e, назначив ему созданную память во всех опциях. - PIO 8bit - output - sysid 3. Вызываю функцию System - Auto-Assign Base Addresses 4. Генерирую ядро (долго) 5. Создаю схемный файл и прикрепляю выводы к процессору. А затем ассоциирую с реальными пинами ИС (компилируя проект между шагами). 6. Сохраняю все и запускаю NIOS II IDE (От админа, об этом еще будет) Создаю проект, темплейт Blanck. 7. Создаю сурс файл и пишу код: #include "alt_types.h" #include "altera_avalon_pio_regs.h" #include "system.h" #include <stdio.h> #include <unistd.h> static int count; int main(void) { count = 0; while( 1 ) { usleep(500000); IOWR_ALTERA_AVALON_PIO_DATA( PIO_BASE, count ); count++; /* Continue 0-ff counting loop. */ } return 0; } 8. Выставляю настройки оптимизации в свойствах проекта [syslib] 9. Правый клик на мой проект (не syslib - билд). 10. Куча строчек бегут в консоли - и ОП самое интересное: Creating libnios_proj_test3_syslib.a... Creating generated.sh... 3 [main] ? (4968) d:\altera\90\quartus\bin\cygwin\bin\sh.exe: *** fatal error - couldn't allocate heap, Win32 error 487, base 0x680000, top 0x690000, reserve_size 61440, allocsize 65536, page_const 4096 2 [main] sh 1044 fork: child -1 - died waiting for longjmp before initialization, retry 0, exit code 0x100, errno 11 /cygdrive/d/altera/90/nios2eds/bin/gtf-generate: fork: Resource temporarily unavailable make[1]: *** [system_description/../obj/generated.sh-t] Error 128 make: *** [system_project] Error 2 Build completed in 20.538 seconds Что интересно ошибки вылазят различные. Все с sh.exe или main.exe. В процессе выполнения еще такие вылазят: Compiling alt_remap_cached.c... 4 [main] ? (5776) d:\altera\90\nios2eds\bin\nios2-gnutools\H-i686-pc-cygwin\bin\nios2-elf-gcc.exe: *** fatal error - couldn't allocate heap, Win32 error 487, base 0x6C0000, top 0x6E0000, reserve_size 126976, allocsize 131072, page_const 4096 2 [main] nios2-elf-gcc 5616 fork: child -1 - died waiting for longjmp before initialization, retry 0, exit code 0x100, errno 11 Compiling alt_remap_uncached.c... Доп информация: ОС Windows 7, Quartus 9. Установлено все в D:\Altera\90\ Что я пробывал: 1. Переставил все связанное с квартусом и НИОС на несистемный диск. 2. Пробовал Web версию квартуса и крякнутую 9.0 3. Отрубил UAC полностью 4. Назначил все приложения указанные в ошибках запускаться от админа Вопрос: Что делать? -

ЛУТ и Алтиум

skkap ответил Murzik_6011 тема в Altium Designer, DXP, Protel

Спасибо! Нашел ответ на свой вопрос :) -

ЛУТ и Алтиум

skkap ответил Murzik_6011 тема в Altium Designer, DXP, Protel

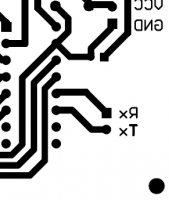

Не смог найти, помогите в следующем вопросе: Раньше пользовался SprintLayout - отправлял на печать напрямую из приложения черные рисунки дорожек и контактов с вырезанными отвестиями. Теперь перешел на AD и столкнулся с проблемой - как выдать на печать подобный рисунок? Множество экспериментов помогли прийти к некоторому алгоритму (для получения ЧЕРНЫХ дорожек без лишних слоев, типа подписей, контуров элементов и т.д.). Я в меню Файл в пункте Fabrication Outputs конвертирую в Gerber формат. Затем не выходя из AD подаю на печать ТОЛЬКО слой на котором все дорожки (он у меня один). Получается что-то вроде этого: Помогите достичь привычного вида :) -

CPLD Clock

skkap ответил skkap тема в Работаем с ПЛИС, области применения, выбор

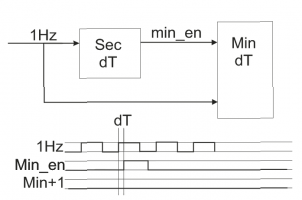

Очень понятно пояснили, спасибо! Значит триггер тактируется Gated Clock, если его тактовый вход подключен к пину, отличному от одного из глобальных тактовых сигналов, верно? Значит необходимо каждый блок, содержащий триггеры тактировать исходным тактовым сигналом. Остались непонятны две вещи: 1. Зачем оно надо вообще? Чем плохо gated clock? 2. Как описанная вами ситуация будет работать? Вот рисунок: Ведь схема счета секунд дает задержку, из-за которой я так понимаю не сработает счет минут? что я не так понял? : / -

CPLD Clock

skkap ответил skkap тема в Работаем с ПЛИС, области применения, выбор

Т.е. будет лучше, если счетчик минут будет считать секунды и счетчик часов будет считать секунды (3600)? Это я так понимаю сожрет еще макроячеек, а какой будет выигрыш? я так и не понял:) И какое отношение к этому имеет триггер на alarm? -

CPLD Clock

skkap ответил skkap тема в Работаем с ПЛИС, области применения, выбор

Спасибо!:) Хм.. Поясните плз, я похоже совсем в клоках не соображаю. Как это асинхронные клоки? Асинхронные от чего? Как изменить cnt5bit и cnt6bit? Они ведь затактированны от предыдущих элементов (минуты от секунд, часы от минут)? Это сама логика часов, или я чего-то не понимаю? Поясните пожалуйста! -

CPLD Clock

skkap ответил skkap тема в Работаем с ПЛИС, области применения, выбор

У меня фронты такта около 100 нс, имеет смысл ставить триггер Шмитта? -

CPLD Clock

skkap ответил skkap тема в Работаем с ПЛИС, области применения, выбор

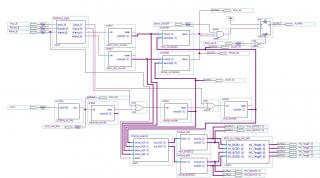

Вроде сделал прошивку для CPLD! :) Прошу указать на ошибки или неоптимальности (особенно в коде VHDL), т.к. это мой первый проект для ПЛИС. Итак проект (Quartus II): clock.rar Главная схема (скрин): Все блоки кроме логики кнопок реализованы на VHDL, CLK_1HZ_SIM сделан для удобства симуляции, вообще такт должен идти от блока 32768Hz_to_1Hz. В основном выкладываю из-за наличия кучи варнингов и боязни что в самой схеме или в коде VHDL есть грубые ошибки, надеюсь кто-нить из знающих посмотрит :) -

CPLD Clock

skkap ответил skkap тема в Работаем с ПЛИС, области применения, выбор

Почти час искал) Спасибо! -

CPLD Clock

skkap ответил skkap тема в Работаем с ПЛИС, области применения, выбор

Всем снова привет! Появилась новая "проблема", на этот раз с QuartusII. На самом деле не совсем проблема, а просто некоторая непонятка, итак ситуация: Создал проект, в нем схемный файл для общей блок схемы, назначил его Сущностью верхнего уровня (Top-level Entity). В нем создаю основные функциональные блоки часов и реализовываю на VHDL. Это делаю таким методом: Создаю новый VHDL файл, затем пишу логику работы, потом правый клик на файл в дереве проекта и создаю файлы символа (Create Symbol files for Current File). После этого данный символ появляется в списке символов для добавления в схемный файл. Таким образом все отлично работает, но один блок захотелось реализовать также схемой, а не на VHDL. Создал схемный файл, добавил инпуты/аутпуты, добавил реализацию логикой, сохранил. А пункта Create Symbol files for Current File в контекстном меню схемного файла нет! Каким образом создать символ (такой же как при реализации на VHDL) для этого файла? Я это раньше делал в MAX PLUS, поэтому я думаю это должно быть возможно, я просто что-то упускаю. Знаю один способ сделать то что я описал с помощью Block Tool, но этот метод мне совсем не нравится. В этом случае блок получается огромный с таблицей входов-выходов + еще каждый вход-выход приходится выводить в отдельный прямоугольник (Port Mapping), что сжирает пол экрана места (мне критично, т.к. потом буду оформлять отчет с этой блок-схемой) Подскажите!:) -

CPLD Clock

skkap ответил skkap тема в Работаем с ПЛИС, области применения, выбор

А про него просто написать забыл :) При его уменьшении как бы это сказать.. фронты задние болтаются туда-сюда, а это я так понимаю значит что частота немного колеблется, что есть плохо. Тем более время запуска около секунды - нормально, учитывая что в часах питание должно будет присутствовать постоянно, иначе в них нет смысла) Спасибо еще зраз за советы и доки! Уверен что еще появятя вопросы, озвучу в этой теме -

CPLD Clock

skkap ответил skkap тема в Работаем с ПЛИС, области применения, выбор

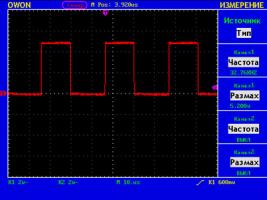

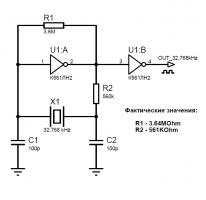

Попробовал, при 1МОм и закоротка частота не устанавливается вообще, скочит от 20 до 40 КГц. Поставил 3.6МОм, работает хорошо, впрочем как и при 10. За доки огромное спасибо!! То что я искал, с пояснениями и графиками! По расчетам мне надо C1 и C2 около 60пФ, самое близкое что нашлось - 100пФ, поставил - запускается за секунду(к томуже возможно это цифровой осцил тормозит), частота стабильна! Пропустил через два инвертора и получил сигнал красивей некуда (скрин прилогается) :) Всем спасибо, вроде первая проблема решена) Да, и чуть не забыл, итоговая схема (может быть не идеал, но работает :) )