Gennadiy_

Свой-

Постов

80 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Gennadiy_

-

Звание

Частый гость

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

1 105 просмотров профиля

-

Поддельные FT232R

Gennadiy_ ответил Gennadiy_ тема в Микросхемы

>> Не понятно зачем вы это опубликовали, это уже старый баян, и на форуме давно обсуждался. Потому, что не нашел этих обсуждений, что надо сказать меня удивило, а грабли ... Про баян с PL2xxx лет 8 назад уже было, про FT не слышал, хотя логично таким путем репутацию портить.. >> Я бы по-другому сказал, на Ali скорее вообще не встречаются настоящие FTDI. А я вот думал играть третий раз в рулетку... -

Поддельные FT232R

Gennadiy_ опубликовал тема в Микросхемы

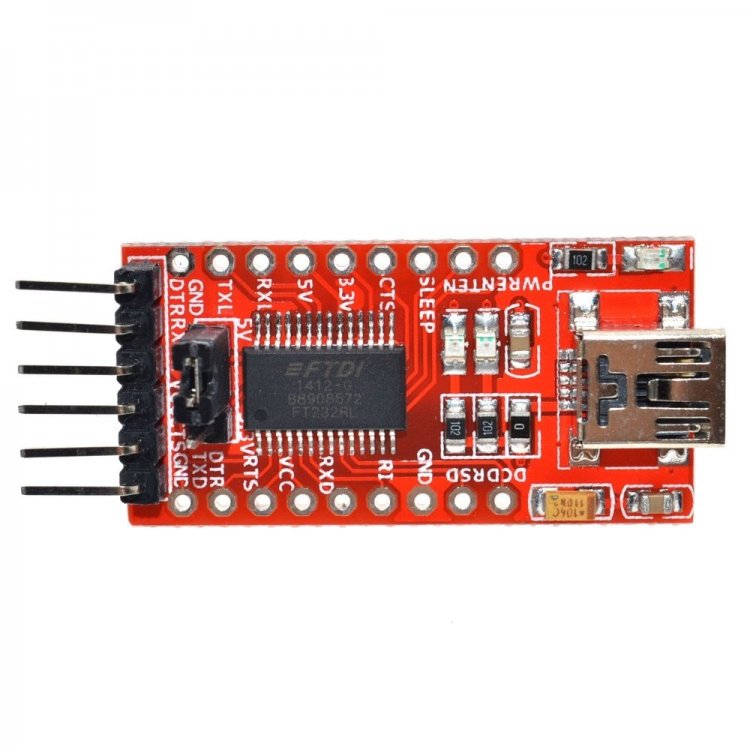

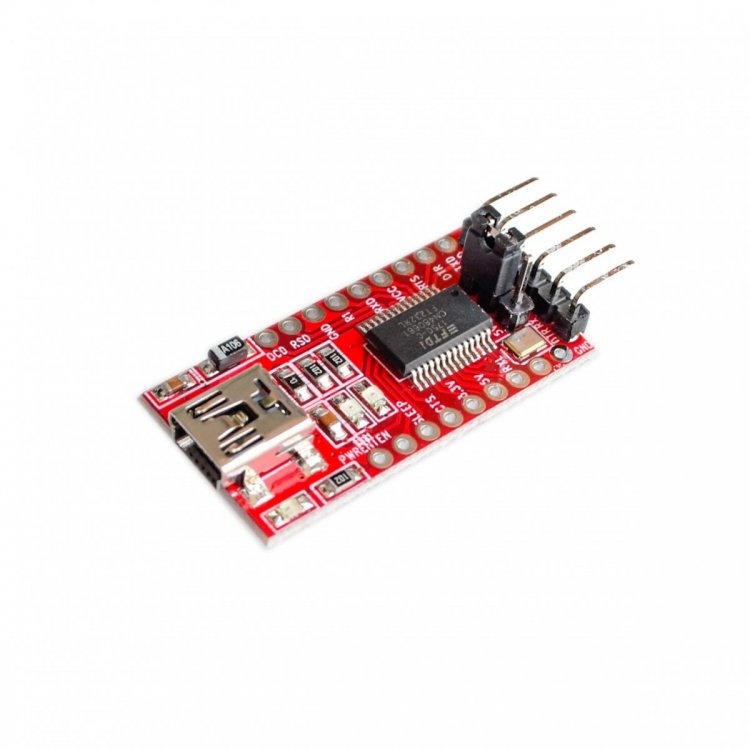

Эта тема не вопрос, просто делюсь информацией, пост адресован скорее начинающим или (начинающие, подозреваю, так глубоко копать не будут) продвинутым ардуинщикам и Приобрел уже вторую плату на ALi c якобы FT232R, по факту там стоит подделка, которая имитирует ее работу, но похоже не содержит EPROM, в силу этого эта плата работает только в конфигурации по умолчанию, и не позволяет сменить режим работы CBUS . Причем первую купил более года назад, и она отличалась от аналогичной, но с правильной МС, взятой у коллеги, просто блеклой маркировкой чипа, выглядят они как фото сделанном "сверху". Проверяется утилитой FT_prog, доступной на сайте FTDI. Для проверки попробуйте сменить, например, строку описание устройства, на плате коллеги это проходит без проблем, на моих нет, а он тоже приобретал у китайцев. Остальные две фотографии это то, что мне прислали сейчас, все фото взяты с Али, тут появился резонатор возле выходного разъема, очевидно теперь без резонатора уже не работает... хотя фирменный FT232 обязан. И далее, ту что приехала год назад, я пробовал использовать в режиме когда DBUS используется как IO, но для этого достаточно переключить режим через драйвер, и это работает на этой подделке. Вторую еще не тестировал так, но вероятно и не буду. Перед покупкой у китайца спросил оригинальный ли там чип, и получил утвердительный ответ... По возможности не берите это барахло, как UART они разумеется работают, но тогда зачем брать такой FT если есть еще более китайские CH340 ? Надеюсь, сэкономил кому-то время. Успехов! -

Немного добавлю про BF, есть версии с флеш на борту, но это просто два кристалла в одном корпусе соединенные по SPI доступном снаружи, скорее для экономии места на плате. А вот технология аутентификации кода позволяет привязать ПЗУ к конкретной мс. Можно защитить как код, так и само устройство от запуска стороннего кода. Память для хранения ключей, реализована по технологии исключающей считывание ее состояния под микроскопом. Однако, как уже сказали тут оцените возможности конкурентов, и свои, чтобы чего лишнего не зашифровать, например таблицу для CRC.

-

Гравировальные машины

Gennadiy_ ответил Юрий-Самара тема в в домашних условиях

Где вы там точность нашли? Я только дискретность перемещения видел, а это не одно и тоже. Элементы станка выполнены штамповкой\изгибом, что не есть хорошо в принципе. Подозреваю, что жесткости рамы даст гораздо худшие результаты, чем указанный дискрет перемещения. Пробовать надо. -

Как создать топологию и констрейны для дифф. пар ?

Gennadiy_ опубликовал тема в Работаем с трассировкой

Собственно вопрос тут: http://electronix.ru/forum/index.php?showtopic=43885 Очевидно, я его не в той ветке задал. -

Добрый день всем. Есть дифференциальная пара CLK, есть структура цепи с длинами участков которую надо повторить, цепь содержит терминирующие резисторы и конденсаторы, Cadence 15.1 В концепте сделана схема, и экспортрована в Алегро, и все констрейны задаются уже в нем. Источникам и приемникам соспоставлены дифференциальные модели. Создана Диф пара в таблице констрейнов, и заданы минимум ее параметров. Открываю топологию пары в sigX, и только часть! цепи оказывается соединена диф линиями. Редактирую топологию так как надо, новые линии получаю копированием, не диф линии удаляю, при этом слежу чтобы соединения соответствовали электрической схеме. Сохраняю, делаю "файл\апдате констрейн", сохраняю новое правило в таблице констрейнов. В sigX вызываю меню создания констрейнов. Выбираю вкадку Prop Delay. Выбираю любой выход источника, и ближайшую к нему "Т" точку, для задания длинны участка и получаю собщение "The following pin pair is not in the same Xnet" с указанием их позиций. Прикрепил картинки, на 1 автоматом, на второй после редактирования. Если вместо "Т" точки выбрать, например, приемник сигнала, то все ОК, другие "т" точки, тоже неработают. Если удалить часть связей, допустим оторвать любую линию с емкостью от всей цепи, ошибки при добавления констрейна с теме же точками не возникает, можно добавить этот констрейн, а потом добавить связи и попытаться сохранить, и вновь получить ошибку при сохранении. Попробовал открыть проект на других версиях софта, под линуксом 15.5 и винде 15.7, в обоих случаях получил список элементов из включенных в цепь, которым сопоставлены ДИФ модели, и самих диф линий, и сообщение, что такие элементы не поддерживаются имеющейся лицензией. С не диф сигналами таких проблемм не испытываю. Спектра при попытке развести эту цепь вываливается с ошибкой, остальные цепи разводит. Куда смотреть, что делать? 1.bmp 2.bmp

-

BAG in FTCJTAG.DLL ver 1.8 !

Gennadiy_ ответил Gennadiy_ тема в Форумы по интерфейсам

Еще новость: минимальное количество бит для вывода функцией JTAG_WriteRead равно 2ум, на это стоит соответствующее условие, зачем....? Решение аналогичное... -

Асинхронная логика

Gennadiy_ ответил Gennadiy_ тема в Языки проектирования на ПЛИС (FPGA)

нет, нет для этого надо получить хоть какойто законченный кусок, а вопросы уже есть... -

Асинхронная логика

Gennadiy_ ответил Gennadiy_ тема в Языки проектирования на ПЛИС (FPGA)

- поправил кракозябры -

Асинхронная логика

Gennadiy_ ответил Gennadiy_ тема в Языки проектирования на ПЛИС (FPGA)

- крокозябры после копирования появились. reg_en_clear - task которая сбрасывает все сигналы выбора целевых регистров в не активное состояние "reg_en_clear" был введен чтобы не повторять описание в каждом случае всех цепей, если if- else заменяет такое описание то хорошо, учту. Я хочу получить счетчик (тут он "размазан" по коду), который будет устанавливаться в случае st_command_processing асинхронно, по мере вычисления логической функции реализованной в case (command_reg), затем по переходу в другое состояние автомата (любое) его значение фиксируется, т.е. это latch. В состоянии st_data_processing должен производиться счет числа входов в это состояние, по достижении 0, вырабатывается сигнал, assign will_be_data = (data_count==0)? 0:1; который, влияет на выбор следующего состояния. -

Асинхронная логика

Gennadiy_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Описываю автомат состояний, описание из трех основных разделов, переход по клоку, выбор следующего состояния, и управление выходом, привожу только последний. В виду моего мышления, видимо, пытаюсь применять подобные конструкции, которые по моему разумению, должны выглядеть как latch или асинхронная логика, но есть сомнения... Хотя прямых противоречий не вижу... Ранее с программирумой логикой и языками описания не работал, мелочевка тоже мимо прошла, в основном ASM. Среда Квартус, чип EPM570. Как вообще обстоят дела с асиннхронной логикой при синтезе ? при реализации ? //управляем выходом always @(pres_state ) // or will_be_data or command_reg ? begin : out_control_FSM case (pres_state) .............................................. st_command_processing: begin //обработка кода команды reg_en_clear; //фиксируем latch для регистра команд, закрываем выход FT case (command_reg) //надо загрузить счетчик байт в зависимости от кода команды COLD_RESET: begin data_count <= 0; end; RESET: begin data_count <= 0; end; GET_VER: data_count <= 0; SET_CLOCK: data_count <= 1; GET_CLOCK: data_count <= 0; SET_MODE_DEV0: data_count <= 1; GET_MODE_DEV0: data_count <= 0; SET_DEV0: data_count <= 3; GET_DEV0: data_count <= 0; SET_MODE_DEV1: data_count <= 1; GET_MODE_DEV1: data_count <= 0; SET_DEV1: data_count <= 3; GET_DEV1: data_count <= 0; SET_MODE_DEV2: data_count <= 1; GET_MODE_DEV2: data_count <= 0; SET_DEV2: data_count <= 3; GET_DEV2: data_count <= 0; default : data_count <= 0; endcase //data_reg end; //обработка кода команды ................................................................ st_data_processing: begin //обработка данных reg_en_clear; // закрываем выход FT и фиксируем данные в регистрах //********************************************* if (will_be_data) data_count <= data_count-1; //********************************************* end; //обработка данных .................................................. default : endcase //pres_state end; //out_control_FSM -

В соседней ветке "работа" ~ пол года, год назад мелькало предложение по снятию информации, и ссылки на статьи по этому поводу... Наблюдал как содрали прибор, содрали топологию ВЧ, а нч сделали заново, маркировка была содрана, но от анализа логики работы это не защищает, естественно, при таком способе, пару фич в софте содрать не смогли, потому как не знали про них, что несколько ухудшило параметры, но никто не гарантирует, что тот кто будет это разрабатывать заново не добавит туда своих...

-

BAG in FTCJTAG.DLL ver 1.8 !

Gennadiy_ опубликовал тема в Форумы по интерфейсам

Это заинтересует тех кто сам взялся прикручивать эту библиотеку с этой микросхемой к своему проекту. Функция JTAG_WriteRead (см FTCJTAGPG13.pdf) реализована с ошибкой: при выводе любой последовательности битов, выровненной на границу байта, т.е. число бит кратное 8, последний передаваемый по каналу связи бит, старший, всегда записывается как равным "0". Это происходит следующим образом, см AN2232C-01_MPSSE_Cmnd.pdf "Clock Data to TMS/CS Pin (no Read)", поскольку запись последнего бита и выход из шифт регистра происходит по одному клоку, последний бит должен быть скопирован в качестве первого выводимого в команду "Clock Data to TMS/CS Pin (no Read)", однако этого не происходит, см рисунок выводится 0х80. Решение может быть такое, приписать впереди к последовательности лишний бит, тогда все ОК. Глазго проинформировал об этом, но на сайте библиотеку пока не обновили. http://nukeuploads.com/download/1186150632...TCJTAG.zip.html crop80.bmp -

Вроде при создании библиотечного символа есть выбор префикса. И при создании лог схемы он элементы автоматом номерует, а вот когда схему для разработки PCB платы рисую нет? Имеется ввиду схема из элементов с изначально присвоенными типами корпуса, без вариантов по перераспределению вентилей.