Voloshchenko

Свой-

Постов

347 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Voloshchenko

-

Звание

Местный

Контакты

-

Сайт

Array

Информация

-

Город

Array

Посетители профиля

1 667 просмотров профиля

-

В 2006 году решил подобную задачу, но на другом наборе микросхем, посмотрите в http://electronix.ru/forum/index.php?showt...16146&st=30 И там же вторая разработка http://electronix.ru/forum/index.php?showt...16146&st=60 где качестве контроллера Ethernet-10/100 использован чип от Micrel KSZ8842-16 MQL. В состав платы входят C8051F123 и XC9572XL

-

Изначально хотели найти аналитическое выражение для ошибки азимута, где аргументами были бы смещение (эксцентриситет) и угол между плоскостями, но так и не нашли. Но это уже не актуально, хотя и интересно… В итоге остались на использовании инкрементального экодера. Ошибку компенсировали путем долгого статистического накопления отклонений азимута по известным дальним целям и на их основе вводом динамических поправок. Решение основано на компромиссе, то есть не идеальное… к A.W.P. Вам лучше создать новую тему, иначе Ваши вопросы могут затеряться...

-

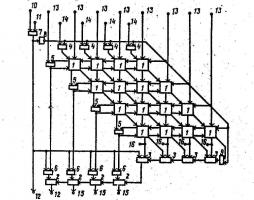

Одним делением вычислить два

Voloshchenko ответил alexPec тема в Математика и Физика

Делимое/делитель дают частное и остаток от деления. Возможно, Вам нужны и частное, и остаток вместе.... Аппаратная реализация для этого - это матрица элементов, например в а.с. 1462297 G 06 F 7/52 от 05.08.87 Матричное устройство для деления (деление в доп.кодах). Подробней смотрите в http://electronix.ru/forum/index.php?showtopic=46469&hl= Еще книга М.А.Карцев, В.А.Брик "Вычислительные системы и синхронная арифметика", 1981г.... см.рис.5.1.2, 5.4.1. -

Как вариант, посмотрите в http://electronix.ru/forum/index.php?showtopic=46469&hl= 4. а.с. 1260951 G 06 F 7/552 от 18.04.85 Матричное вычислительное устройство для извлечения квадратного корня

-

up не помню о таких предупреждениях, читаю что у меня 0%, там где "Предупреждения". но письмо все же поступило... не понятно все это...

-

В приложении принципиальная схема, там CS8900, C8051F127 и XC9572LX. Все это модуль для передачи Ethernet-10 через каналы E1 или SHDSL, реализованный мною в 2006 г. Кстати, его фото в посте номер 31 этой темы. Этот модуль подключается к соответствующему линейному модему. Был еще аналогичный проект для подобных задач, но на KSZ8842. Его фото чуть выше. Высылаю эту схему, как пример использования CS8900. Открыть можно в PCAD или в P-CAD 2006 Schjematiс Viewer. Удачи. Shdsl_Eth.sch

-

Аппаратный подсчет обязательно дает выигрыш, хотя, согласен, можно и без него и контрольной суммы. Время 0.30мс - это многовато. Хотя, для LwIP, это может и хороший результат. В приложении осциллограммы по оценке времени, там это время 0.19мс с аппаратной контрольной суммой. Но это не предел, еще не задействован DMA и др. History.rar

-

Думаю, Вашей системе хватило бы и UDP-пакетов, а это даст существенное увеличение скорости в сравнении с TCP-пакетами, где на каждый пакет ожидается подтверждение о его получении. Да и аппаратное вычисление контрольной суммы здесь само напрашивается. Моя система чем-то сходна, тоже видеосигнал, оцифровка, и тоже реальный масштаб времени. В пике получается до 70 Мбит/с, а реально после сжатия хватает и 30 Мбит/с. Правда, без DMA, так как NiosII/f достаточно для этих задач LAN. В основном идет выдача, а во встречном направлении, время от времени, поступают команды управления, которые сразу обрабатываются и квитируются. Обошелся набором: UDP, ARP. RARP, ICMP (для ping). По поводу LwIP – хорошо, что она освоена Вами и работает, может когда-то и нам пригодится. Ее я просматривал пока только в качестве примера для некоторых функций в LAN91C111.

-

Как подсчитана скорость? Расскажите немного о Вашей системе, тогда можно говорить об оптимизации вычислительных процессов. Может, хватит и UDP-пакетов. У меня Nios/f на 100МГц, с аппаратным вычислением контрольной суммы для UDP. Причем, в нем два поочередно переключаемых блока памяти, пока из одного выдается пакет в LAN через NiosII, второй заполняется аппаратно и для него вычисляется контрольная сумма, т.е. здесь распараллеливание. Потом, работа идет 32-разрядными кодами, а как в LwIP? Может, поможет это «Nios II Ethernet Acceleration Design Example» в http://www.altera.com/support/examples/nio...celeration.html и здесь "Nios II CRC Acceleration Design Example "http://www.altera.com/support/examples/nio...celeration.html

-

Что-то в этом топике стало попахивать порохом: просьба не стрелять в прохожих. :) Для меня тема PCI на Cyclone III сейчас актуальна, т.к. собираюсь заменить две FPGA типа FLEX10K30A и FLEX10K100A на две более мощные EP3C16 и EP3C25. Старая плата работает в промышленном компьютере с PCI на +5В. В ней я использую ядро PCI-mt32 и обеспечиваю прямой доступ к памяти, в новой плате будет аналогично. Кстати, FLEX10KA подключаются напрямую к PCI на +5В, хотя ее выводы питаются от +3.3В. Как я понял, Cyclone III имеют защитные диоды по выводам, остается добавить последовательный резистор около 100 Ом для защиты от более высокого +5В со стороны PCI. В то же время, здесь была предложена схема на Cyclone II, а в ней согласующие буфера на полевиках. То есть хотел бы понять, какой способ электрического согласования с PCI наилучший именно для Cyclone III. Может уже кто-то испытал Cyclone III на шине PCI c +5В? Топик лучше перенести в раздел FPGA или по интерфейсам. Здесь его могут не заметить...

-

Спасибо! Согласен, здесь я не додумал. Приоритет за Вами. Это же, как закон Ома (Ньютона): пропорционален и обратно пропорционален. Что называется, за лесом дров не видно… :) А я искал формулу, в которой при заданной точности определения азимута на корабль, находится допустимый эксцентриситет, при котором эта точность еще гарантируется. Понятно, что чем больше радиус измерительного кольца энкодера, тем лучше…. Согласен, что абсолютный энкодер лучший среди лучших. Например, наша эволюция шла так: сначала СКВТ, сейчас инкрементальный энкодер, а теперь вот задумываемся об абсолютном. И похоже, что мы к нему придем, уже есть на примете 16-разрядный абсолютный энкодер…. Но там свои проблемы, например, помехо-защищенный высокоскоростной канал связи от антенны до обработчика, который хорошо бы сделать на оптоволокне… Потом передача в него импульса, совпадающего по времени с зондирующим, для фиксации угла, затем временные апертуры и т.д…Но проблема с допуском на эксцентриситет остается... Ваше мнение и соображения мне интересны и я их учту.

-

Спасибо за советы и статью. Статья однозначно интересная. Я сразу отметил, что эта РЛС гражданская, где требуя высокую точность, почему-то отдают предпочтение дешевым решениям… 1. Энкодер установлен на вращающемся СВЧ-переходе и через него проходит волновод. Муфт здесь нет и прецизионных подшипников тоже. Если посмотреть на рис.2 из L-9517-9205.pdf, то это больше походит на вариант справа Предположим, что мы купили очень хороший инкрементальный энкодер. Вопрос стоит так, какой допустим эксцентриситет, что бы получить наперед заданную точность измерения угла? Здесь эксцентриситет это смещение между осью вращающегося перехода и осью энкодера. Хотелось бы найти геометрическими анализ по этой проблематике, с итоговыми формулами… Может я много хочу.. :) 2. «Инкрементальный энкодер на РЛС ставить опасно, возможно из-за пропусков получение неоднозначности .» Здесь согласен, редко, но бывают пропуски, обычно раз в час. Можно иногда смириться. «Существуют же (даже с приемкой военных) 12 разрядные датчики угла с кодом Грея по выходу.» Тоже задумываемся об абсолютном энкодере, но тогда нужен высокоскоростной интерфейс длиной до 10 метров, может даже оптический, что бы не ловить помехи. «В последних модификациях Российских РЛС планировалось ставить специализированный СКВТ, внушительных размеров, совмещенный с поворотной платформой ФАР.» СКВТ для нас запасной вариант. Как я понимаю, для ФАР он лучше всего подходит, там же нет непрерывного вращения. Хотя там с кодом Грея, возможно тоже подошел бы. Думаю, проблема эксцентриситета для СКВТ остается тоже...

-

Энкодер на валу.

Voloshchenko опубликовал тема в Метрология, датчики, измерительная техника

Всем привет! Разыскиваются публикации о точности инкрементального энкодера посаженного на вал. В частности: 1. Как влияет на точность, смещение (эксцентриситет) между осью вала и геометрической осью энкодера? 2. Как влияет на точность, угол между плоскостью вращения вала и плоскостью вращения измерительного диска энкодера? Ведь ясно, что абсолютного совмещения осей и плоскостей добиться не возможно, и, как следствие, возможны ошибки измерения угла. Это нужно для совершенствования гражданской береговой РЛС. В ней на вал антенны жестко посажен инкрементальный энкодер с 4096 отсчетами на оборот, а оборот совершается за 3 секунды. -

Если подходит матричное (однотактное) устройство для извлечения корня, то посмотрите на варианты в http://electronix.ru/forum/index.php?showtopic=46469&hl= Там, например, в AC1260951 устройство по алгоритму извлечения кв.корня без восстановления остатка, с примерами... Табличный способ тоже считается хорошим, но его применять не приходилось... к Asb "А Вы случайно не задачу расчета порога обнаружения решаете", Вопрос не ко мне, но интересен. У меня порог, но применительно к гражданским береговым РЛС. Но здесь к использованию корня еще не подошел... Если область сходная, то поделитесь соображениями по поводу порогов и их расчетов... Тема жутко актуальна...

-

Как все же купить и получить эту книгу тем, кто в Украине? Работал в P-CAD-ах, потом Protel-99 SE, Protel-DXP теперь вот в AD09. Без хорошего учебника тяжко. Неужели почтой переслать никак нельзя?