-

Постов

3 414 -

Зарегистрирован

-

Посещение

-

Ага, спасибо! Как то не подумал обратиться к любимой Вике...

-

Как вычислить фазу импульса ЛЧМ?

_sda опубликовал тема в Вопросы системного уровня проектирования

Коллеги, известны следующие параметры: частота дискретизации, начальная частота, конечная частота, длительность импульса. Как зная начальную фазу в начале импульса вычислить фазу ЛЧМ в конце импульса? -

Отладка проекта с DDR3

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Спасибо всем участникам обсуждения! Все платы заработали, калибровка проходит. От себя добавлю - внимательность и ещё раз внимательность. Больше ничего не потребовалось. -

Отладка проекта с DDR3

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Никакая не глупость, мне самому, например, попадались FPGA с маркировкой несуществующей в природе. Да, скорее всего рискну перепаять, пока других мыслей нет. Паяли сами, рентген-контроля нет. -

Отладка проекта с DDR3

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Стрёмно как-то, могу и рабочей платы лишиться... Частота уж больно высокая, нет соответствующего оборудования. У осциллографа полоса 200 МГц. И ещё сложилось впечатление что корка затыкается на нерабочих платах (если не проходит калибровка). При попытке записать данные шина не оживляется. -

Отладка проекта с DDR3

_sda опубликовал тема в Работаем с ПЛИС, области применения, выбор

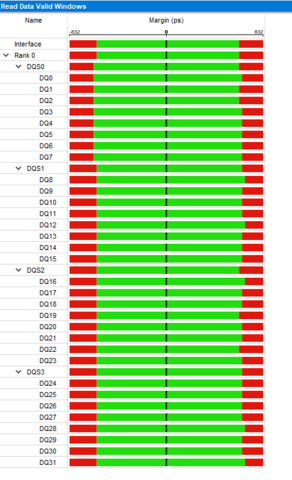

Коллеги, у меня спаяно 6 новых плат, три из них работают, три - нет. Работаю с FPGA Intel. Картинка результата тестирования рабочей платы: На мой взгляд очень неплохо. А на нерабочих тест вообще не проходит. Вроде всё уже проверил: номиналы резисторов, целостность связи FPGA - DDR3, напряжения питания... В прошлом году сделал десяток таких плат, но слава Богу такого затыка не было. Возможно кто-то поделится опытом как выходили из такой ситуации. На что ещё обратить внимание? -

Вопрос по TopJTAG

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Я вроде уже разобрался, отремонтировал. Спасибо за желание помочь. -

Вопрос по TopJTAG

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

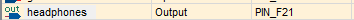

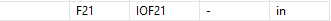

Хех... Перегенерил BSDL-файл с признаком post. В самом файле эта ножка описывается как выход: --BSC group 185 for Family-specific output pin F21 "555 (BC_4, *, internal, X)," & "556 (BC_1, *, control, 1)," & "557 (BC_1, IOF21, output3, X, 556, 1, Z)," & А в TopJTAG всё равно описывается как вход: Ничего не понимаю. Что ему ещё нужно? -

Вопрос по TopJTAG

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Вроде разобрался, опять подвела память. Буду устранять дефект. -

Вопрос по TopJTAG

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Спасибо! Вы хотите сказать что нужно ручками править BSDL-файл? Если мне не изменят память, у хилых ISE мог сам генерировать нужный BSDL-файл, похоже что Квартус так не умеет? -

Вопрос по TopJTAG

_sda опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, почему наблюдается разнобой в направлении порта в проекте Квартуса и в TopJTAG? Вот что показывает Квартус Вот что показывает TopJTAG Соответственно управлять им нет возможности. Как это устранить? -

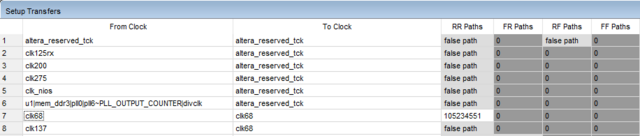

Setup Transfers

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Скриншот сверху - это из TimeQuest. В отчётах Квартуса такое число поиском не находится. Попробовал на всякий случай задать миллион сигналов для анализа такой строкой, уже час молотит и конца не видно. Надоело ждать, выключил. report_timing -from_clock { clk68 } -to_clock { clk68 } -from [get_keepers {*}] -to [get_keepers {*}] -setup -npaths 1000000 -detail full_path -panel_name {Report Timing} -multi_corner -

Setup Transfers

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Эх, компиляцию уже запустил... Это надолго. -

Setup Transfers

_sda опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, а как понять число в строчке №7? Это что за число такое большое 105234551? Не может же в реальной плисине такого быть? -

Проверил, увы, ничего не изменилось. А я так надеялся на этот синхронный ресет. Хотя это странно: перед этим проектом я применял режим dynamic phase shift в пятом циклоне, так этот вопрос и близко не стоял, всё работало замечательно без установки флажка Enable physical output clock parameters и с асинхронным ресетом. Изделие уже пол-года насилуют у заказчика, нареканий нет. Особенность семейства?