-

Постов

240 -

Зарегистрирован

-

Посещение

-

Да, я так когда то и делал, двигал фазу выходного клока. Но там была опытная разработка и нужно было проверить на стенде работу алгоритма. Потому обмен с SDRAM делал на скорую руку. И мне тогда такое решение со сдвигом клока не очень понравилось. Подумал, может быть есть какие то более элегантные варианты. Почему мне еще не хочется сам клок двигать: например, при чтении из памяти, ответные данные тоже будут сдвинуты относительно моего внутреннего клока. Как то это всё к усложнению на приеме на ПЛИС приведет. Хотелось бы уйти от этих усложнений, если такое возможно.

-

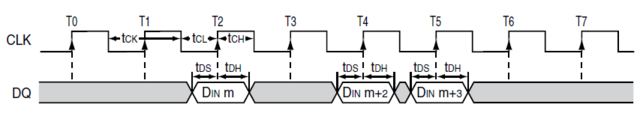

Добрый день, коллеги! Давно я не работал с синхронной памятью, и немного стал подзабывать тонкости. Непосредственно сам вопрос в заголовке. Но если рассмотреть более подробно, то пусть имеется вот такая упрощенная диаграмма, ее нужно реализовать на выходе ПЛИС: Имеется выходной клок CLK и выходные данные DQ (на самом деле это двунаправленная шина, но сейчас не важно). Есть ограничения на 'data setup' и 'data hold', пусть для примера Tds = 1.5 ns, Tdh = 0.8 1. Как правильно написать констрейт? Например так будет корректно? set_output_delay -max -clock clk -1.5 [get_ports {DQ}] set_output_delay -min -clock clk +0.8 [get_ports DQ}] 2. Как правильно вывести выходной клок CLK относительно внутреннего. Будет ли достаточно сформировать его на PLL без смещения фазы? Или здесь тоже нужны констрейты? 3. Нужно ли для сигнала DQ устанавливать выходной триггер в ножке? Или в данном случае это неправильно и синтезатор не сможет так обеспечить требуемые Tds и Tdh 4. Ну и последний вопрос. Следует ли учитывать в контрейтах задержки при распространении сигналов на плате? Где то в примерах видел, что добавляют погрешность +/- 100 ps Получается, что Tds = 1.5+0.1 = 1.6 ns; Tdh = 0.8+0.1 = 0.9 ns

-

Мне кажется, что человеку еще рано за языки браться пока нет понимания цифровой схемотехники. Ему нужно начать с самых базовых вещей. Понять что такое комбинационная логика, триггеры (RS, D); мультиплексоры, счетчики, памяти. Зачем нужен тактовый сигнал. Без этой базы вряд ли что то дельное получится. Пока видно, что человек плавает в самых простых вещах. Найти какой-нибудь хороший институтский курс по цифровой схемотехнике.

-

Сдох Cyclone IV

gin ответил Alexey-K27 тема в Работаем с ПЛИС, области применения, выбор

Можно. Прошивка хранится в памяти EPCS. Если она не пострадала, то меняйте только FPGA -

FPGA Pango PGL22G

gin ответил 1113 тема в Предлагаю работу

Именно TCP реализовывать на FPGA - это довольно трудоемко и следовательно затратно по времени. На мой взгляд. Если ограничиться UDP, тогда гораздо проще и быстрее. У меня есть готовые решения для 100 Мбит и 1 Гбит IP/UDP. Проверено в железе на Kintex7 -

Да, память лучше ставить. А то вдруг окажется, что на входе чересстрочное видео. Значит часть кадра придется буферизировать

-

вот пример ошибки, которую я понять не могу Net 'gen_tx_fast_udp_buf[0].tx_fast_udp_buf/bufring128_main_inst/n1' has multiple drivers (..\libs\bufring\test_tdpr.vhd:19) Ок, смотрю на файл и 19 строку, на которую ругается Efinity library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity test_tdpr is generic ( DATA_WIDTH : natural := 1; ADDR_DEPTH : natural := 1024 ); port ( clk_a : in std_logic; clk_b : in std_logic; addr_a : in natural range 0 to ADDR_DEPTH - 1; addr_b : in natural range 0 to ADDR_DEPTH - 1; data_a : in std_logic_vector((DATA_WIDTH-1) downto 0); data_b : in std_logic_vector((DATA_WIDTH-1) downto 0); we_a : in std_logic := '1'; we_b : in std_logic := '1'; q_a : out std_logic_vector((DATA_WIDTH -1) downto 0); q_b : out std_logic_vector((DATA_WIDTH -1) downto 0) ); end test_tdpr; 19 строка - это data_b : in std_logic_vector((DATA_WIDTH-1) downto 0); Далее смотрю, где и как этот модуль подключается test_tdpr_ctrl_bit : entity work.test_tdpr generic map ( DATA_WIDTH => 1, ADDR_DEPTH => FIFO_WORD_DEPTH ) port map ( clk_a => clk_wr, clk_b => clk_rd, addr_a => tdpr_a_addr, addr_b => tdpr_b_addr, data_a => mem_bit_ctrl_wr, data_b => (others => '0'), we_a => tdpr_a_we, we_b => tdpr_b_we, q_a => open, q_b => bit_ctrl_rd ); data_b => (others => '0'), Какой может быть мультипл драйверс, когда там порт тупо посажен на ноль! И самое забавное, в другом проекте эта же часть кода нормально собирается. Вот как то так 😢 А какая там последняя версия, и как к ftp доступ получить?

-

Коллеги, добрый вечер! Подскажите пожалуйста, какая версия Efinity более-менее стабильная? У меня щас стоит 2021.2 (с патчем), и мне кажется, она меня скоро доканает)

-

ПЛИС наши (Россия)

gin ответил White тема в Работаем с ПЛИС, области применения, выбор

Спасибо! Ну я и имел ввиду, что доп софт для ПЛИС Воронежа) Как понимаю, для получения этого софта нужно связываться непосредственно с самим Воронежем? -

ПЛИС наши (Россия)

gin ответил White тема в Работаем с ПЛИС, области применения, выбор

А для аналога Cyclone3 какую версию Квартуса нужно использовать? Как я понимаю самая последняя - это 13.1, в который была поддержка Циклонов? И нужен ли еще какой дополнительный софт? -

ПЛИС наши (Россия)

gin ответил White тема в Работаем с ПЛИС, области применения, выбор

да, спасибо, тоже этот каталог скачал. Но в любом случае, очень скудная инфа у них :( -

ПЛИС наши (Россия)

gin ответил White тема в Работаем с ПЛИС, области применения, выбор

Коллеги, добрый день! Подскажите, где и как посмотреть хоть какую-нить инфу по воронежским ПЛИС? При попытке посмотреть на официальном сайте, он перенаправляет на форму регистрации. При попытке регистрации ничего не происходит, никаких писем не приходит. Как хоть узнать, что у них за микросхемы и что они умеют? Интересен аналог Cyclone3 -

Проверьте, нет ли непропая на каких-либо пинах. В своё время была проблема с нестабильной работай трансиверов у Ксайлинкса. Оказалось, что один их клоков (который отвечает за работу внутренней FSM) болтался в воздухе

-

Скачалось. Спасибо большое!

-

Спам смотрел - нету. Пытался регистрировать на gmail, потом на yandex. Может и вправду Интелу они не нравятся - хочет корпоративный адрес. Хотя раньше Альтеру я на gmail регистрировал. Ваши ссылки работаю, всё качается. Спасибо! И если не очень трудно, не могли бы вы скинуть ссылку на StratixV GX для Quartus 14.0 ? https://fpgasoftware.intel.com/14.0/?edition=subscription&platform=windows У меня при попытке качать от туда требует регистрацию...