t0nloon

Участник-

Постов

12 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о t0nloon

- День рождения 30.08.1981

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

609 просмотров профиля

-

Спасибо за советы. Попробую STEMLab 125-14 задействовать. Если не получится, попробую найти ML605 и подобрать подходящий мезонин.

-

Здравствуйте. Для проверки опытного образца нужна отладочная плата. Основные требования к такой плате: - уложиться бы в 30-40т. руб; - ЦАП (разрядность 14 бит или выше, частота 80 МГц или выше); - ПЛИС (лучше Xilinx хотя можно и Altera, желательно с возможностью реализации MicroBlaze); - внешний Eth - разъем; - не менее 50 выводов (идущих от ПЛИС) на внешний разъем. Честно говоря, удивился, когда не обнаружил более-менее приемлемых плат с комбинацией ПЛИС+ЦАП. Пришлось даже рассматривать варианты с мезонинной платой FMC. Прошу помогите с поиском.

-

Вопрос по отладке: Семейство FLEX10KE (получается и наш родимый 5576ХС4Т) логический анализатор SignalTap II не поддерживает. В чем отлаживали ПЛИСину? (я имею ввиду аналог ChipScope как для Xilinx)

-

Подскажите с каким программатором работали? Слышал, что в руководстве рекомендуется только ByteBlaster (или это только при PS конфигурировании?). USB-Blaster кто-нибудь применял?

-

PCI на ПЛИС FLEX10K

t0nloon ответил t0nloon тема в Интерфейсы

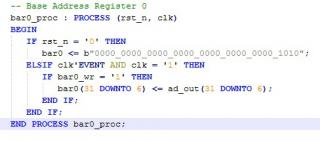

Адресация делается по 32-разрядным регистрам (пространство памяти состоящее из 60 штук 32-разрядных регистров). PCI Mega Wizard пока не затрагиваем. Описание конфигурационного регистра (BAR0) делаю своими руками. Возможно в коде vhdl будет понятнее: (здесь bar0_wr - сигнал записи в конфигурационный регистр) -

PCI на ПЛИС FLEX10K

t0nloon ответил t0nloon тема в Интерфейсы

Не буду открывать новую тему. Попробую спросить здесь. Вопрос по BAR (спецификацию читал, темы просматривал, но некоторые вопросы остались): Нужно реализовать BAR0 описывающий адресное пространство памяти размером 0х3С Правильно ли я рассуждаю? - размер 0х3С это 60 в десятеричной - ближайшее большее число (формата 2^n) является 2^6 = 64 - значит BAR должен состоять из: 26 бит на чтение/запись (это биты 31...6) 6 бит только на чтение (это биты 5...0) - причем младшие 6 бит имеют постоянное значение: 0 бит = '0' (т.к. описываем пространство памяти) 2 и 1 биты = "01" (т.к. описываем область памяти с адресацией меньше 1МБ) 3 бит = '1' (BAR не вызывает "побочных" явлений при считывании) 5 и 4 биты = "00" (зануляем оставшиеся биты) -

PCI на ПЛИС FLEX10K

t0nloon ответил t0nloon тема в Интерфейсы

Не компилируется AHDL-файл pci_mt32.tdf Не могу понять в чем проблема. Выдает следующие ошибки. Скрин ошибки -

PCI на ПЛИС FLEX10K

t0nloon ответил t0nloon тема в Интерфейсы

-

PCI на ПЛИС FLEX10K

t0nloon ответил t0nloon тема в Интерфейсы

electro-ryb пока не отвечает. Возможно, почту проверяет нечасто. Serhiy_UA, могли бы вы скинуть проект для Quartus или MAX+Plus? Почта: [email protected] -

PCI на ПЛИС FLEX10K

t0nloon ответил t0nloon тема в Интерфейсы

Description This is a very simple PCI-target to Wishbone-master bridge. Нужен master/slave. -

PCI на ПЛИС FLEX10K

t0nloon ответил t0nloon тема в Интерфейсы

Спасибо за предложенные варианты. Но, PCI устройство нужно реализовать на EPF10K200S. Тут без вариантов. Времени на реализацию интерфейса вручную, к сожалению, не дают. Пожалуйста, помогите достать PCI MegaCore Function pci_mt32. Уверен в закромах ftp такое добро присутствует. -

PCI на ПЛИС FLEX10K

t0nloon опубликовал тема в Интерфейсы

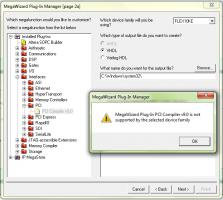

Доброго всем дня. Есть задача, организовать на EPF10K200S (FLEX10K фирмы Altera) PCI-устройство с возможностями master/target (32-bit). Quartus поставил версии 9.0, более высокие версии уже не поддерживают FLEX. С альтеровскими плис и софтом только начал знакомство. Почитав форум, нашел, что можно воспользоваться PCI MegaCore Function. Исходя из документации на эту корку, если я правильно понимаю, нужно дополнительно устанавливать PCI Compiler. Может кто помочь с дистрибутивом на него? :ph34r: Возможно есть более эффективные способы организовать PCI-устройство?