Alexander_92

Участник-

Постов

27 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Alexander_92

-

Звание

Участник

-

Не важно, а вы не знаете, как в FPGA можно делать преобразования частот ?

-

Ну я тоже интуитивно так думаю, но это как-то связано с физикой процессов ...

-

А как это можно аргументировать ? )) Пожалуйста, объясните.

-

Есть задача спроектировать контроллер нескольких независимых интерфейсов SPI, то есть 4хSPI. В тз указано, что тактовая частота может быть в пределах 100-200 Мегагерц. То есть в реальности она, получается, действительно плавает и это нужно учитывать. Насчет независимых интерфейсов, что если контроллер принимает от нескольких ведомых сразу, то этот прием может происходить на разных частотах SCLK. Опять же указывается, SCLK может быть 5-20 Мегагерц.

-

Здравствуйте, подскажите, пожалуйста, если тактовая частота процессора плавает при работе в определенном пределе, то это можно как-то описать в файле проектных ограничений или принять во внимание другим образом при разработке проекта на ПЛИС ? Спасибо.

-

ADSP-2181

Alexander_92 опубликовал тема в Сигнальные процессоры и их программирование - DSP

Здравствуйте ! Подскажите, пожалуйста, точно насчет ADSP - 2181. Он относится к ЦСП с SISD или SIMD архитектурой ?? Спасибо !!! Срочно. -

Здравствуйте ! Будьте любезны, кому не трудно, можете посоветовать любую русскоязычную литературу, касающийся архитектуры существующих ЦСП различных производителей. Буду очень благодарен, очень горит для презентации, но нужны хорошие обзорные научные статьи из интернета или книги. Всем большое спасибо ! :laughing: :help:

-

Спасибо, но не совсем понятно мне с управляющими сигналами. Я знаю, что такое дешифратор и регистры, но не улавливаю вот именно связь выхода дешифратора (от 0 до 9 ?) с регистрами.

-

Функциональная схема модуля Verilog

Alexander_92 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте ! Пожалуйста, помогите разобраться с функциональной схемой модуля Verilog. Необходимо нарисовать функциональную схему по коду. Буду благодарен любым пояснениям. :help Данный модуль выделяет десятки и единицы. Кто-то подал идею, что здесь 2 каскадно-соединенных счетчика. `timescale 1ns / 1ps module CNTS_ONE( input [5:0] CNT_SEC, input [5:0] CNT_MIN, input [5:0] CNT_HOUR, output reg [3:0] CNT1, output reg [3:0] CNT2, output reg [3:0] CNT3, output reg [3:0] CNT4, output reg [3:0] CNT5, output reg [3:0] CNT6 ); always @ (CNT_SEC) begin case (CNT_SEC) 0 : begin CNT2 <= 0; CNT1 <= 0; end 1 : begin CNT2 <= 0; CNT1 <= 1; end 2 : begin CNT2 <= 0; CNT1 <= 2; end 3 : begin CNT2 <= 0; CNT1 <= 3; end 4 : begin CNT2 <= 0; CNT1 <= 4; end 5 : begin CNT2 <= 0; CNT1 <= 5; end 6 : begin CNT2 <= 0; CNT1 <= 6; end 7 : begin CNT2 <= 0; CNT1 <= 7; end 8 : begin CNT2 <= 0; CNT1 <= 8; end 9 : begin CNT2 <= 0; CNT1 <= 9; end 10 : begin CNT2 <= 1; CNT1 <= 0; end 11 : begin CNT2 <= 1; CNT1 <= 1; end 12 : begin CNT2 <= 1; CNT1 <= 2; end 13 : begin CNT2 <= 1; CNT1 <= 3; end 14 : begin CNT2 <= 1; CNT1 <= 4; end 15 : begin CNT2 <= 1; CNT1 <= 5; end 16 : begin CNT2 <= 1; CNT1 <= 6; end 17 : begin CNT2 <= 1; CNT1 <= 7; end 18 : begin CNT2 <= 1; CNT1 <= 8; end 19 : begin CNT2 <= 1; CNT1 <= 9; end 20 : begin CNT2 <= 2; CNT1 <= 0; end 21 : begin CNT2 <= 2; CNT1 <= 1; end 22 : begin CNT2 <= 2; CNT1 <= 2; end 23 : begin CNT2 <= 2; CNT1 <= 3; end 24 : begin CNT2 <= 2; CNT1 <= 4; end 25 : begin CNT2 <= 2; CNT1 <= 5; end 26 : begin CNT2 <= 2; CNT1 <= 6; end 27 : begin CNT2 <= 2; CNT1 <= 7; end 28 : begin CNT2 <= 2; CNT1 <= 8; end 29 : begin CNT2 <= 2; CNT1 <= 9; end 30 : begin CNT2 <= 3; CNT1 <= 0; end 31 : begin CNT2 <= 3; CNT1 <= 1; end 32 : begin CNT2 <= 3; CNT1 <= 2; end 33 : begin CNT2 <= 3; CNT1 <= 3; end 34 : begin CNT2 <= 3; CNT1 <= 4; end 35 : begin CNT2 <= 3; CNT1 <= 5; end 36 : begin CNT2 <= 3; CNT1 <= 6; end 37 : begin CNT2 <= 3; CNT1 <= 7; end 38 : begin CNT2 <= 3; CNT1 <= 8; end 39 : begin CNT2 <= 3; CNT1 <= 9; end 40 : begin CNT2 <= 4; CNT1 <= 0; end 41 : begin CNT2 <= 4; CNT1 <= 1; end 42 : begin CNT2 <= 4; CNT1 <= 2; end 43 : begin CNT2 <= 4; CNT1 <= 3; end 44 : begin CNT2 <= 4; CNT1 <= 4; end 45 : begin CNT2 <= 4; CNT1 <= 5; end 46 : begin CNT2 <= 4; CNT1 <= 6; end 47 : begin CNT2 <= 4; CNT1 <= 7; end 48 : begin CNT2 <= 4; CNT1 <= 8; end 49 : begin CNT2 <= 4; CNT1 <= 9; end 50 : begin CNT2 <= 5; CNT1 <= 0; end 51 : begin CNT2 <= 5; CNT1 <= 1; end 52 : begin CNT2 <= 5; CNT1 <= 2; end 53 : begin CNT2 <= 5; CNT1 <= 3; end 54 : begin CNT2 <= 5; CNT1 <= 4; end 55 : begin CNT2 <= 5; CNT1 <= 5; end 56 : begin CNT2 <= 5; CNT1 <= 6; end 57 : begin CNT2 <= 5; CNT1 <= 7; end 58 : begin CNT2 <= 5; CNT1 <= 8; end 59 : begin CNT2 <= 5; CNT1 <= 9; end default : begin CNT2 <= 0; CNT1 <= 0; end endcase end always @ (CNT_MIN) begin case (CNT_MIN) 0 : begin CNT4 <= 0; CNT3 <= 0; end 1 : begin CNT4 <= 0; CNT3 <= 1; end 2 : begin CNT4 <= 0; CNT3 <= 2; end 3 : begin CNT4 <= 0; CNT3 <= 3; end 4 : begin CNT4 <= 0; CNT3 <= 4; end 5 : begin CNT4 <= 0; CNT3 <= 5; end 6 : begin CNT4 <= 0; CNT3 <= 6; end 7 : begin CNT4 <= 0; CNT3 <= 7; end 8 : begin CNT4 <= 0; CNT3 <= 8; end 9 : begin CNT4 <= 0; CNT3 <= 9; end 10 : begin CNT4 <= 1; CNT3 <= 0; end 11 : begin CNT4 <= 1; CNT3 <= 1; end 12 : begin CNT4 <= 1; CNT3 <= 2; end 13 : begin CNT4 <= 1; CNT3 <= 3; end 14 : begin CNT4 <= 1; CNT3 <= 4; end 15 : begin CNT4 <= 1; CNT3 <= 5; end 16 : begin CNT4 <= 1; CNT3 <= 6; end 17 : begin CNT4 <= 1; CNT3 <= 7; end 18 : begin CNT4 <= 1; CNT3 <= 8; end 19 : begin CNT4 <= 1; CNT3 <= 9; end 20 : begin CNT4 <= 2; CNT3 <= 0; end 21 : begin CNT4 <= 2; CNT3 <= 1; end 22 : begin CNT4 <= 2; CNT3 <= 2; end 23 : begin CNT4 <= 2; CNT3 <= 3; end 24 : begin CNT4 <= 2; CNT3 <= 4; end 25 : begin CNT4 <= 2; CNT3 <= 5; end 26 : begin CNT4 <= 2; CNT3 <= 6; end 27 : begin CNT4 <= 2; CNT3 <= 7; end 28 : begin CNT4 <= 2; CNT3 <= 8; end 29 : begin CNT4 <= 2; CNT3 <= 9; end 30 : begin CNT4 <= 3; CNT3 <= 0; end 31 : begin CNT4 <= 3; CNT3 <= 1; end 32 : begin CNT4 <= 3; CNT3 <= 2; end 33 : begin CNT4 <= 3; CNT3 <= 3; end 34 : begin CNT4 <= 3; CNT3 <= 4; end 35 : begin CNT4 <= 3; CNT3 <= 5; end 36 : begin CNT4 <= 3; CNT3 <= 6; end 37 : begin CNT4 <= 3; CNT3 <= 7; end 38 : begin CNT4 <= 3; CNT3 <= 8; end 39 : begin CNT4 <= 3; CNT3 <= 9; end 40 : begin CNT4 <= 4; CNT3 <= 0; end 41 : begin CNT4 <= 4; CNT3 <= 1; end 42 : begin CNT4 <= 4; CNT3 <= 2; end 43 : begin CNT4 <= 4; CNT3 <= 3; end 44 : begin CNT4 <= 4; CNT3 <= 4; end 45 : begin CNT4 <= 4; CNT3 <= 5; end 46 : begin CNT4 <= 4; CNT3 <= 6; end 47 : begin CNT4 <= 4; CNT3 <= 7; end 48 : begin CNT4 <= 4; CNT3 <= 8; end 49 : begin CNT4 <= 4; CNT3 <= 9; end 50 : begin CNT4 <= 5; CNT3 <= 0; end 51 : begin CNT4 <= 5; CNT3 <= 1; end 52 : begin CNT4 <= 5; CNT3 <= 2; end 53 : begin CNT4 <= 5; CNT3 <= 3; end 54 : begin CNT4 <= 5; CNT3 <= 4; end 55 : begin CNT4 <= 5; CNT3 <= 5; end 56 : begin CNT4 <= 5; CNT3 <= 6; end 57 : begin CNT4 <= 5; CNT3 <= 7; end 58 : begin CNT4 <= 5; CNT3 <= 8; end 59 : begin CNT4 <= 5; CNT3 <= 9; end default : begin CNT4 <= 0; CNT3 <= 0; end endcase end always @ (CNT_HOUR) begin case (CNT_HOUR) 0 : begin CNT6 <= 0; CNT5 <= 0; end 1 : begin CNT6 <= 0; CNT5 <= 1; end 2 : begin CNT6 <= 0; CNT5 <= 2; end 3 : begin CNT6 <= 0; CNT5 <= 3; end 4 : begin CNT6 <= 0; CNT5 <= 4; end 5 : begin CNT6 <= 0; CNT5 <= 5; end 6 : begin CNT6 <= 0; CNT5 <= 6; end 7 : begin CNT6 <= 0; CNT5 <= 7; end 8 : begin CNT6 <= 0; CNT5 <= 8; end 9 : begin CNT6 <= 0; CNT5 <= 9; end 10 : begin CNT6 <= 1; CNT5 <= 0; end 11 : begin CNT6 <= 1; CNT5 <= 1; end 12 : begin CNT6 <= 1; CNT5 <= 2; end 13 : begin CNT6 <= 1; CNT5 <= 3; end 14 : begin CNT6 <= 1; CNT5 <= 4; end 15 : begin CNT6 <= 1; CNT5 <= 5; end 16 : begin CNT6 <= 1; CNT5 <= 6; end 17 : begin CNT6 <= 1; CNT5 <= 7; end 18 : begin CNT6 <= 1; CNT5 <= 8; end 19 : begin CNT6 <= 1; CNT5 <= 9; end 20 : begin CNT6 <= 2; CNT5 <= 0; end 21 : begin CNT6 <= 2; CNT5 <= 1; end 22 : begin CNT6 <= 2; CNT5 <= 2; end 23 : begin CNT6 <= 2; CNT5 <= 3; end default : begin CNT6 <= 0; CNT5 <= 0; end endcase end endmodule -

Здравствуйте, дали поновее отладочную плату, установил VisualDSP ++. Но есть ещё какая-то программка SDK developer с Matlab вроде связана, правда, не могу установить из-за отсутствия лицензионного кода. Что это за программа и есть ли новые версии ? Может кто скинет какие-нибудь примеры с кодами для данной отладочной платы. Огромное спасибо !

-

Спасибо. А как называется медленный и глючный эмулятор ?

-

Спасибо, а не подскажете, какой JTAG нужен ? Как правильно называется или может ссылку скинете ? Просто важно то, когда я подключу один конец в плату, а второй в комп (есть USB даже), то Visual Dsp должен показать коннект девайса ) С Visual Dsp уже знаком, на ADSP-2181 запускал фильтр, но то был EZ-KIT Lite.

-

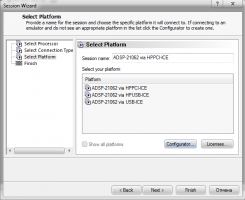

Симулятор исключен, надо на железе запустить, комп старый есть, плата вставлена, DSP21k тоже стоит, но толку пока мало, нет DSP21k Toolkit User’s Guide. А если через JTAG, то как этот интерфейс называется для данной платы ? Вообще в VisualDsp только 3 таких варианта эмуляторов к ADSP 21062, но какой из них по названию должен верно подойти ? То есть с помощью эмулятора можно будет запустить программку фильтра на EZ-LAB ?

-

Здравствуйте ! Если кто-нибудь работал со старенькой платой ADSP-21062 SHARC EZ-LAB BOARD, то сможем мне подсказать, наверное. Буду очень благодарен любой полезной информации. Стоит задача запуска цифрового фильтра на этой плате, но не совсем понятно, через какой интерфейс можно программировать данный DSP. Насколько известно, то большинство DSP от Analog devices поддерживаются средой разработки приложений Visual DSP ++. К данной плате есть только мануал по семейству Sharc, да и общий мануал EZ-LAB Development System Manual (ftp://ftp.analog.com/pub/dsp/210xx/21062/ez-lab/ugezlb31.pdf), но совсем непонятно, как на ней можно запустить хоть любую простенькую программку на С. Есть какая-то программка Diag21k, но похоже чего-то всё равно не хватает. Кто сможет подсказать, с чего хотя бы начать, тому большое, нет просто громаднейшее спасибо ! :) Help

-

Вот я нашёл, если есть у кого время, помогите разобраться с кодом, вроде синтаксис понимаю, но что это в железе не представляю. То есть у этого модуля по идее есть входы и выходы, но куда необходимо подключать вход/выход цифрового фильтра именно к этому контроллеру? Фильтр работает с дискретными значениями. Пожалуйста, объясните, как происходит управление ? Как только ПЛИСка прошьётся, то аудиопорты должны реагировать на входящий сигнал, если я подключу генератор, например. `timescale 1ns / 1ps module ac97_controller( input SYSCLK, // up to 125MHz input SYSTEM_RESET, // active on 1 input BIT_CLK, // 12,288 MHz input SDATA_IN, output SYNC, output SDATA_OUT, output RESET, output DONE, input [15:0] Slot0_in, input [19:0] Slot1_in, input [19:0] Slot2_in, input [19:0] Slot3_in, input [19:0] Slot4_in, input [19:0] Slot5_in, input [19:0] Slot6_in, input [19:0] Slot7_in, input [19:0] Slot8_in, input [19:0] Slot9_in, input [19:0] Slot10_in, input [19:0] Slot11_in, input [19:0] Slot12_in, output reg [15:0] Slot0_out, output reg [19:0] Slot1_out, output reg [19:0] Slot2_out, output reg [19:0] Slot3_out, output reg [19:0] Slot4_out, output reg [19:0] Slot5_out, output reg [19:0] Slot6_out, output reg [19:0] Slot7_out, output reg [19:0] Slot8_out, output reg [19:0] Slot9_out, output reg [19:0] Slot10_out, output reg [19:0] Slot11_out, output reg [19:0] Slot12_out ); parameter START_DELAY = 17'd131000; parameter WAIT_FOR_BITCLK_DELAY = 2'b11; // the states of the state machine parameter Idle = 2'b00, Load = 2'b01, // SlotS_out are loaded from Data_reg_in and Data_reg_out is loaded with SlotS_in Send = 2'b10, // Registers are shifted Wait_until_Start = 2'b11; // Lines 67-70 & 130 reg [9:0] Increment = 0; // integer Incremented is used for the bit count of a 256-bit frame, as well as SYNC's frequency reg [16:0] Var_start = 0; // incremented varialbe used to set the signal RESET at the start reg Reset_Ready; reg [1:0] Wait_for_BITCLK = 0; reg [2:0] Frame_Done_reg = 0; reg [255:0] Data_reg_out = 0; reg [255:0] Data_reg_in = 0; reg [1:0] StC = Idle; reg [1:0] StN = Idle; // If SYSTEM_RESET is 1, Var_start (used to count until RESET is deasserted to 1) is reset to 0 always @ (posedge SYSCLK) if (SYSTEM_RESET) Var_start <= 0; else if (Var_start == START_DELAY) Var_start <= Var_start; else Var_start <= Var_start + 1; always @ (posedge BIT_CLK) if (!Reset_Ready) Wait_for_BITCLK <= 0; else if (Wait_for_BITCLK == WAIT_FOR_BITCLK_DELAY) Wait_for_BITCLK <= Wait_for_BITCLK; else Wait_for_BITCLK <= Wait_for_BITCLK + 1; // RESET is 0 until the start delay is over assign RESET = (Var_start == START_DELAY) ? 1:0; always @ (posedge BIT_CLK) Reset_Ready <= (Var_start == START_DELAY) ? 1:0; // DONE always @ (posedge SYSCLK) if (StC != Load) Frame_Done_reg <= 0; else Frame_Done_reg <= {Frame_Done_reg[1:0], 1'b1}; assign DONE = (Frame_Done_reg[0]&Frame_Done_reg[1]&~(Frame_Done_reg[2])) ? 1:0; // Increment is incremeneted to 256 and then set to 1. Increment is reset to 0 only when a RESET occurs always @ (posedge BIT_CLK) if (StC == Idle) Increment <= 0; else if ((StN == Load) || (StN == Send)) if (Increment == 256) Increment <= 1; else Increment <= Increment +1 ; // SYNC will have (12,288MHz / 256) = 48KHz frequency & 20.8us period. SYNC is active while Slot0 is being sent only = for 16 BIT_CLKs assign SYNC = (((Increment < 16)&&(Increment > 0)) || (StN == Load)) ? 1:0; // Saving the data from SDATA_IN into Data_reg_in & cleaning Data_reg_in if a reset occurs. Data_reg_in must be shifted during the Load stat as well always @ (posedge BIT_CLK) if (Var_start < START_DELAY - 1) Data_reg_in <= 0; else Data_reg_in[255:0] <= {Data_reg_in[254:0], SDATA_IN}; // Data_reg_out being loaded with a new frame and shifted each BIT_CLK to be sent on SDATA_OUT always @ (posedge BIT_CLK) if (StN == Load) Data_reg_out <= {Slot0_in, Slot1_in, Slot2_in, Slot3_in, Slot4_in, Slot5_in, Slot6_in, Slot7_in, Slot8_in, Slot9_in, Slot10_in, Slot11_in, Slot12_in}; else Data_reg_out [255:0] <= {Data_reg_out[254:0], 1'b0}; // State machine always @ (posedge BIT_CLK or posedge SYSTEM_RESET) if (SYSTEM_RESET) StC <= Idle; else StC <= StN; always @ * begin StN <= StC; case (StC) Idle: if ((!SYSTEM_RESET) && (Wait_for_BITCLK == WAIT_FOR_BITCLK_DELAY)) StN <= Wait_until_Start; Wait_until_Start: if (Reset_Ready) StN <= Load; Load: StN <= Send; Send: if (Increment == 256) StN <= Load; default: StN <= Idle; endcase end assign SDATA_OUT = Data_reg_out[255]; always @ (posedge SYSCLK) begin if (StC == Load) begin Slot0_out <= Data_reg_in[255:240]; Slot1_out <= Data_reg_in[239:220]; Slot2_out <= Data_reg_in[219:200]; Slot3_out <= Data_reg_in[199:180]; Slot4_out <= Data_reg_in[179:160]; Slot5_out <= Data_reg_in[159:140]; Slot6_out <= Data_reg_in[139:120]; Slot7_out <= Data_reg_in[119:100]; Slot8_out <= Data_reg_in[99:80]; Slot9_out <= Data_reg_in[79:60]; Slot10_out <= Data_reg_in[59:40]; Slot11_out <= Data_reg_in[39:20]; Slot12_out <= Data_reg_in[19:0]; end end endmodule