-

Постов

3 306 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о toweroff

-

Звание

Гуру

- День рождения 23.12.1974

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

11 403 просмотра профиля

-

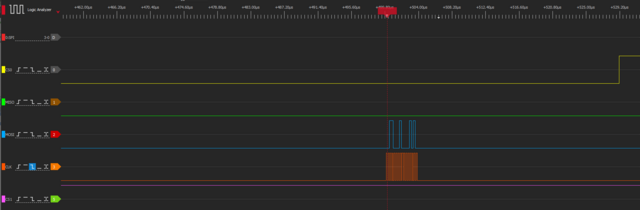

Итак, по результатам анализа эпюр, интерфейс SPI работает корректно, как с аппаратным CS0, так и с cs-gpio (CS1) проблема в конфигурировании устройства, сидящего на CS1, но это не проблема интерфейса SPI

-

пока выражается в некорректной работе. При отключении в настройках устройства, висящего на cs-gpio, устройство на аппаратном CS начинает работать корректно. чуть позже залезу анализатором, попробую посмотреть предмет конфликта

-

не очень, да. И, как оказалось, вносит свой раздрай при обмене(( пока ищу, можно ли корректировать время активирования CS до начала такта и время деактивации после

-

-

Не хочет spidev1.1 поднимать( root@OpenWrt:~# dmesg | grep spi [ 0.336207] sun6i-spi 1c69000.spi: chipselect 0 already in use [ 0.354936] spi_master spi1: spi_device register error /soc/spi@1c69000/spidev@1 [ 0.354974] spi_master spi1: Failed to create SPI device for /soc/spi@1c69000/spidev@1 root@OpenWrt:~# ls /dev/spi* /dev/spidev1.0 root@OpenWrt:~# извиняюсь... почему-то опять всплыл reg = <0>; сейчас пересоберу, проверю

-

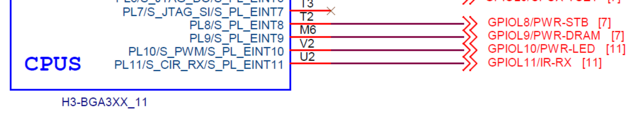

в sunxi-h3-h5.dtsi вот такое описание: r_pio: pinctrl@1f02c00 { compatible = "allwinner,sun8i-h3-r-pinctrl"; reg = <0x01f02c00 0x400>; interrupt-parent = <&r_intc>; interrupts = <GIC_SPI 45 IRQ_TYPE_LEVEL_HIGH>; clocks = <&r_ccu CLK_APB0_PIO>, <&osc24M>, <&rtc CLK_OSC32K>; clock-names = "apb", "hosc", "losc"; gpio-controller; #gpio-cells = <3>; interrupt-controller; #interrupt-cells = <3>; r_ir_rx_pin: r-ir-rx-pin { pins = "PL11"; function = "s_cir_rx"; }; r_i2c_pins: r-i2c-pins { pins = "PL0", "PL1"; function = "s_i2c"; }; r_pwm_pin: r-pwm-pin { pins = "PL10"; function = "s_pwm"; }; r_uart_pins: r-uart-pins { pins = "PL2", "PL3"; function = "s_uart"; }; }; т.е. у порта PL вообще отдельное описание и пин уже как бы занят

-

-

Пока вот такой результат (прототип на T113 до меня пока добирается, тестирую эту часть на NanopiNeoCore, там CS0 нативный, CS1 через GPIO): &spi1 { status = "okay"; cs-gpios = <0>, <&pio 11 11 GPIO_ACTIVE_LOW>; spidev@0 { compatible = "rohm,dh2228fv"; /* =spidev Kludge, workaround for "buggy DT: spidev listed directly in DT" */ spi-max-frequency = <5000000>; reg = <0>; }; spidev@1 { compatible = "rohm,dh2228fv"; /* =spidev Kludge, workaround for "buggy DT: spidev listed directly in DT" */ spi-max-frequency = <5000000>; reg = <0>; }; }; root@OpenWrt:~# dmesg | grep spi [ 0.317015] sun6i-spi 1c69000.spi: cannot register SPI master [ 0.341211] sun6i-spi 1c69000.spi: cannot register SPI master [ 0.344645] sun6i-spi 1c69000.spi: cannot register SPI master [ 0.361196] sun6i-spi 1c69000.spi: cannot register SPI master [ 0.362052] sun6i-spi 1c69000.spi: cannot register SPI master [ 0.404093] sun6i-spi 1c69000.spi: cannot register SPI master [ 0.415344] sun6i-spi 1c69000.spi: cannot register SPI master [ 1.413215] sun6i-spi 1c69000.spi: cannot register SPI master [ 1.423505] sun6i-spi 1c69000.spi: cannot register SPI master [ 1.468072] sun6i-spi 1c69000.spi: cannot register SPI master [ 1.474606] sun6i-spi 1c69000.spi: cannot register SPI master [ 1.520434] sun6i-spi 1c69000.spi: cannot register SPI master [ 1.527071] sun6i-spi 1c69000.spi: cannot register SPI master [ 5.636167] sun6i-spi 1c69000.spi: cannot register SPI master [ 20.326411] sun6i-spi 1c69000.spi: cannot register SPI master [ 20.332482] platform 1c69000.spi: deferred probe pending [ 26.551622] sun6i-spi 1c69000.spi: cannot register SPI master

-

ну вот нихрена не понял, где тут две CS линии ну и чуть выше по документу прибило совсем: точнее, тут понятно расположение значений для cs-gpio. Откуда "2 CS lines"? Где-то в драйвере sunxi видел, что cs >=4 вообще не будет рассматриваться завтра буду пробовать

-

нашёл вот так:

-

ну вот навскидку не понимаю. Тогда уж CS0 переписывается ногодрыгом но полез искать-читать...

-

с параметрами пытаюсь копаться, но пока всё равно нет понимания, как cs-gpios описывает виртуальные CSx посмотрю-попробую завтра с анализатором, но пока логики описания чип селектов не вижу, хоть тресни( гпио дескриптор -- это аппаратный SPI_CS, который мультиплексирован на GPIO? ну вот не увидел, хоть тресни, описание того, что это именно CS1. Или это просто выбор пина, а на пине мультиплексор привязан к именно CS1? тогда "софтовый" CSx как описать и какой он там по счёту будет? по факту описания? а если по ходу есть действительный аппаратный селект на конкретном пине? а аппаратный CS0 ещё вдобавок забыли убрать из контроллера и он просто не подключен никуда?

-

а зачем? к spidev могут обращаться разные процессы. Пусть в порядке очереди и лезут, зачем ещё и лишние сущности мониторить? ух.. тогда точно не понял. Объясните, пожалуйста

-

можно пояснить, моя нипанимай) параметром cs-gpios задаются CSx по порядку? <0> -- это аппаратный CS0, <gpio...> -- это ногодрыг условного CS1? если так, продолжу: таким же образом можно описывать другие GPIO как CSx? и ещё момент... на ножку вынесен только аппаратный CS1 у T113-S3. Если использовать ногодрыг, то получится так? cs-gpios = <&pio x y GPIO_ACTIVE_LOW>, <1>; правильно?

-

да, мастер. Но нет любимого Вами бареметала) так-то я и сам бы смог у линуха есть только драйверы, которым нужно правильно это сказать, а как -- не знаю(( тут получается же вот какая штука -- есть аппаратный CS (CS1) и (ибо другого нет на ножках МК) программный. И вот нет понимания, как срестить ужа и ежа