bva_rzn

Участник-

Постов

30 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о bva_rzn

-

Звание

Участник

Посетители профиля

-

Всё оказалось проще. Не учёл, что 88e1111 нужно сбрасывать нулевым уровнем.

-

управление 88e1111 по mdio

bva_rzn опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброе утро. Среда Vivado 2017, плис virtex7. К ПЛИС подключен 88e1111. Пробую им управлять по MDIO. Для начала пытаюсь считать содержимое регистра 2. Сигналы MDIO формирую uB портом gpio. Подключения в top модуле .... inout MDIO_clk; inout MDIO_data; IOBUF MDIO_data_iobuf (.I(wMDC_MDIO_o[1]), .IO(MDIO_data), .O(wMDC_MDIO_i[1]), .T(wMDC_MDIO_t[1])); IOBUF MDIO_clock_iobuf (.I(wMDC_MDIO_o[0]), .IO(MDIO_clk), .O(wMDC_MDIO_i[0]), .T(wMDC_MDIO_t[0])); wMDC_MDIO - линии с microblaze, настроенные на ввод/вывод. MDIO_data снаружи ПЛИС подтянут резистором к питанию. Тактовая частота клока MDC 1 МГц. Сигналы смотрю в ILA. Адрес phy (7) и адрес регистра 2 это уходит на phy, в ответ считываю одни единицы. В чём может быть проблема? Спасибо. -

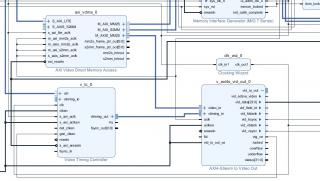

AXI4 vdma

bva_rzn опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Доброе утро. Вопрос про настройки IP блоков плата VC707. Среда Vivado 2017. Запускаю вывод изображения из внешней память DDR3 на AVD7511. С DDR3 работау через MIG. Выход MIG через AXI Interrconnect подключён к AXI4-VDMA (линии M_AXI_MM2S и M_AXI_S2MM). Линия M_AXIS_MM2S подключается к video_in блока axi4-stream-video-out. Сигналы на AVD формирую при помощи axi4-stream-video-out. Временные интервалы hsync и vsync формируются при помощи Video Timing Controlle и поступают на axi4-stream-video-out. axi4-stream-video-out работает в режиме slave. На aclk axi4-stream-video-out поступают 200 МГц, которые так же поступают на входы m_axis_mm2s_aclk блока axi_vdma. На вход clk На VTG подаю 50 МГц. ILA подключаю на линии M_AXIS_MM2S (axi4_vdma) и vtiming_out (VTC). И здесь возникли вопросы: 1) Как настроить AXI4-VDMA из uB для передачи данных из DDR3 на линию M_AXIS_MM2S? 2) На линии vtiming_out ничего не меняется. Спасибо. -

Добрый день! Процессор stm32f407vg. На нём запущена FREERTOS. stm общается с SDcard по SDIO с прерываниями от DMA. Без ОС - инициализация, запись, чтение работают. Вопрос по поводу приоритетов прерываний. Обработчики прерываний имеют вид: void SDIO_IRQHandler(void) { portBASE_TYPE xHigherPriorityTaskWoken = pdFALSE; SD_ProcessIRQSrc(); xSemaphoreGiveFromISR( c_xSemaphore_SDIO_IRQHandler, &xHigherPriorityTaskWoken ); if( xHigherPriorityTaskWoken != pdFALSE ){ portEND_SWITCHING_ISR( xHigherPriorityTaskWoken ); } } void SD_SDIO_DMA_IRQHANDLER(void) { portBASE_TYPE xHigherPriorityTaskWoken = pdFALSE; SD_ProcessDMAIRQ(); xSemaphoreGiveFromISR( c_xSemaphore_SD_SDIO_DMA_IRQHANDLER, &xHigherPriorityTaskWoken ); if( xHigherPriorityTaskWoken != pdFALSE ) { portEND_SWITCHING_ISR( xHigherPriorityTaskWoken ); } } В функции SD_ReadMultiBlocksFIXED .... xSemaphoreGive( c_xSemaphore_SDIO_IRQHandler); xSemaphoreGive( c_xSemaphore_SD_SDIO_DMA_IRQHANDLER); SDIO_ITConfig(SDIO_IT_DCRCFAIL | SDIO_IT_DTIMEOUT | SDIO_IT_DATAEND | SDIO_IT_RXOVERR | SDIO_IT_STBITERR, ENABLE); SDIO_DMACmd(ENABLE); SD_LowLevel_DMA_RxConfig((uint32_t *)readbuff, (NumberOfBlocks * BlockSize)); while (xSemaphoreTake( c_xSemaphore_SDIO_IRQHandler, cardBLOCK_TIME_WAITING)==pdFALSE); while (xSemaphoreTake( c_xSemaphore_SD_SDIO_DMA_IRQHANDLER, cardBLOCK_TIME_WAITING)==pdFALSE); .... и в функции SD_WriteMultiBlocksFIXED ... SDIO_ITConfig(SDIO_IT_DCRCFAIL | SDIO_IT_DTIMEOUT | SDIO_IT_DATAEND | SDIO_IT_RXOVERR | SDIO_IT_STBITERR, ENABLE); SDIO_DMACmd(ENABLE); SD_LowLevel_DMA_TxConfig((uint32_t *)writebuff, (NumberOfBlocks * BlockSize)); while (xSemaphoreTake( c_xSemaphore_SD_SDIO_DMA_IRQHANDLER, cardBLOCK_TIME_WAITING)==pdFALSE); ... Настройка прерываний: void Init_NVIC(void) { NVIC_InitTypeDef NVIC_InitStructure; NVIC_PriorityGroupConfig(NVIC_PriorityGroup_4); NVIC_InitStructure.NVIC_IRQChannel = SDIO_IRQn; NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 12; NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; NVIC_Init(&NVIC_InitStructure); NVIC_InitStructure.NVIC_IRQChannel = SD_SDIO_DMA_IRQn; NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 13; NVIC_Init(&NVIC_InitStructure); NVIC_InitStructure.NVIC_IRQChannel = USART2_IRQn; NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 14; NVIC_Init(&NVIC_InitStructure); } Если NVIC_IRQChannelPreemptionPriority для SDIO и SDIO_DMA поставить 12 и 13, то программа зацикливается в ожидании while ((DMAEndOfTransfer == 0x00) && (TransferEnd == 0) && (TransferError == SD_OK) && (timeout > 0)) { timeout--; } в функции SD_WaitReadOperation(). Задача, для записи данных на карту void vTaskSendSD(void *pvParameters) { volatile UINT BytesWritten; portBASE_TYPE xStatus; uint8_t ps; for (;;) { xQueueReceive(xQueue, &ps, portMAX_DELAY); if(cSDclose < 500){//250 res = f_lseek(&fil, fil.fsize); if(ps) res = f_write(&fil, buf_2, 4096, &BytesWritten); else res = f_write(&fil, buf_1, 4096, &BytesWritten); f_sync(&fil); cSDclose++; }else{ f_close(&fil); f_mount(0, NULL); } } } Каждый из массивов buf заполняется в течении 2.7 сек. Если поставить приоритеты NVIC_IRQChannelPreemptionPriority для SDIO и SDIO_DMA поставить 4 и 5 и убрать семафоры из обработчиков прерываний - проект работает, но нестабильно. Данные на SDcard могут записываться без сбоев длительное время, а может записаться 4 кБайта и всё. В чём может быть проблема, кто сталкивался? Спасибо.

- 1 ответ

-

- stm32f407vg

- freertos

-

(и ещё 1 )

C тегом:

-

Вопрос по TQ

bva_rzn опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый вечер. С TQ только начинаю разбираться. За основу взял пример от уважаемого des00. Подключаю к Cyclone IV ADS5232. Частота дискретизации 20 МГц. Подключаю по схеме Source-Synchronus Input. В качестве tco взял сигнал готовности данных tdv: min 20 нс, max 30 нс. Для начала задержку в проводниках не учитываю. В проекте также используется частота 80 МГц, полученная из входной 20 МГц при помощи pll в режиме normal mode. Конгстрейны следующие: set_time_format -unit ns -decimal_places 3 create_clock -name {SMA_CLKIN} -period 50.000 -waveform { 0.000 25.000 } [get_ports {SMA_CLKIN}] create_clock -name {VIRT_CLKIN} -period 50.000 -waveform { 0.000 25.000 } create_generated_clock -name {clk_80} -source [get_ports {SMA_CLKIN}] -multiply_by 4 set_clock_uncertainty -rise_from [get_clocks {clk_80}] -rise_to [get_clocks {clk_80}] 0.020 set_clock_uncertainty -rise_from [get_clocks {clk_80}] -fall_to [get_clocks {clk_80}] 0.020 set_clock_uncertainty -fall_from [get_clocks {clk_80}] -rise_to [get_clocks {clk_80}] 0.020 set_clock_uncertainty -fall_from [get_clocks {clk_80}] -fall_to [get_clocks {clk_80}] 0.020 set_clock_uncertainty -rise_from [get_clocks {SMA_CLKIN}] -rise_to [get_clocks {clk_80}] -setup 0.070 set_clock_uncertainty -rise_from [get_clocks {SMA_CLKIN}] -rise_to [get_clocks {clk_80}] -hold 0.100 set_clock_uncertainty -rise_from [get_clocks {SMA_CLKIN}] -fall_to [get_clocks {clk_80}] -setup 0.070 set_clock_uncertainty -rise_from [get_clocks {SMA_CLKIN}] -fall_to [get_clocks {clk_80}] -hold 0.100 set_clock_uncertainty -rise_from [get_clocks {SMA_CLKIN}] -rise_to [get_clocks {SMA_CLKIN}] 0.020 set_clock_uncertainty -rise_from [get_clocks {SMA_CLKIN}] -fall_to [get_clocks {SMA_CLKIN}] 0.020 set_clock_uncertainty -fall_from [get_clocks {SMA_CLKIN}] -rise_to [get_clocks {clk_80}] -setup 0.070 set_clock_uncertainty -fall_from [get_clocks {SMA_CLKIN}] -rise_to [get_clocks {clk_80}] -hold 0.100 set_clock_uncertainty -fall_from [get_clocks {SMA_CLKIN}] -fall_to [get_clocks {clk_80}] -setup 0.070 set_clock_uncertainty -fall_from [get_clocks {SMA_CLKIN}] -fall_to [get_clocks {clk_80}] -hold 0.100 set_clock_uncertainty -fall_from [get_clocks {SMA_CLKIN}] -rise_to [get_clocks {SMA_CLKIN}] 0.020 set_clock_uncertainty -fall_from [get_clocks {SMA_CLKIN}] -fall_to [get_clocks {SMA_CLKIN}] 0.020 set_input_delay -add_delay -max -clock [get_clocks {VIRT_CLKIN}] 30.000 [get_ports {data[*]}] set_input_delay -add_delay -min -clock [get_clocks {VIRT_CLKIN}] 20.000 [get_ports {data[*]}] set_clock_groups -exclusive -group [get_clocks {SMA_CLKIN VIRT_CLKIN}] set_false_path -from [get_clocks {SMA_CLKIN}] -to [get_clocks {clk_80}] set_false_path -from [get_clocks {VIRT_CLKIN}] -to [get_clocks {clk_80}] Проблема в том, что в снимаемых с АЦП данных периодически возникают аномальные выбросы. Хочу понять, куда копать. Вопросы следующие: 1) нужно ли использовать режим работы pll in Source-Synchronus mode? 2) ну и риторический вопрос, правильно ли задал конгстрейны? Спасибо. -

Обработка данных с АЦП

bva_rzn опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день. Есть АЦП (временная диаграмма в файле) Частота дискретизации 20 МГц. Выход DV используется для тактирования ПЛИС (Cyclone IV). Параметры t1 = 3.2 nc, t2 = 8.5 nc. Сигнал DV подаю на pll, где делаю две частоты clk_20 (инверсная для DV) и clk_80 (умноженная в 4 раза DV). Конгстреймы: create_clock -name {SMA_CLKIN} -period 50.000 -waveform { 0.000 25.000 } [get_ports {SMA_CLKIN}] create_generated_clock -name {clk_20} -source [get_ports {SMA_CLKIN}] -phase 180.000 -master_clock {SMA_CLKIN} [get_pins {p|altpll_component|auto_generated|pll1|clk[1]}] create_generated_clock -name {clk_80} -source [get_ports {SMA_CLKIN}] -multiply_by 4 -master_clock {SMA_CLKIN} [get_pins {p|altpll_component|auto_generated|pll1|clk[0]}] derive_clock_uncertainty set_input_delay -add_delay -max -clock [get_clocks {clk_20}] 8.500 [get_ports {data_ADC[*]}] set_input_delay -add_delay -min -clock [get_clocks {clk_20}] 3.200 [get_ports {data_ADC[*]}] set_clock_groups -exclusive -group {clk_20} set_clock_groups -exclusive -group {clk_80} Обработка данных от АЦП идёт в двух модулях по положительному фронту клока clk_20 и кроме того данные сохраняются в двухпортовой ОЗУ: ram_dual_port R1( .data({{4'b0},data_ADC}), .rdaddress(adRAMr), .rdclock(clk_80), .rden(1'b1), .wraddress(adRAMw), .wrclock(clk_20), .wren(1'b1), .q(wq_x)); Подскажите, пожалуйста, правильно ли составлены конгсреймы? Спасибо. -

связь fpga с nios ii

bva_rzn опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день. Подскажите, пожалуйства, правильно ли делаю. Связываю плис и nios (плата DE0-nano) при помощи двух dual-port RAM: одна для передали данных из плис в nios, другая - из nios в плис. Также используются две линии: одна для передачи сигнала готовности данных от плис в nios w_data_ready (данная линия заведена на прерывания от PIO), другая - от nios в плис. Вот часть кода: ...... ram RAMin(.clock_a(CLOCK_25), .clock_b(CLOCK_50i), .address_a(w_address_in), .address_b(w_address_in_nios), .data_a(w_data_in), .data_b(), .q_a(), .q_b(w_data_in_nios), .rden_a(1'b0), .rden_b(1'b1), .wren_a(1'b1), .wren_b(1'b0)); ram RAMout(.clock_a(CLOCK_25), .clock_b(CLOCK_50i), .address_a(w_address_out), .address_b(w_address_out_nios), .data_a(), .data_b(w_data_out_nios), .q_a(w_data_out), .q_b(), .rden_a(1'b1), .rden_b(1'b0), .wren_a(1'b0), .wren_b(1'b1)); de0_nano_Qsys d1( .clk_clk(CLOCK_50i), // clk.clk .reset_reset_n(1'b1), // reset.reset_n .sdra_wire_addr(DRAM_ADDR), // new_sdram_controller_wire.addr .sdra_wire_ba(DRAM_BA), // .ba .sdra_wire_cas_n(DRAM_CAS_N), // .cas_n .sdra_wire_cke(DRAM_CKE), // .cke .sdra_wire_cs_n(DRAM_CS_N), // .cs_n .sdra_wire_dq(DRAM_DQ), // .dq .sdra_wire_dqm(DRAM_DQM), // .dqm .sdra_wire_ras_n(DRAM_RAS_N), // .ras_n .sdra_wire_we_n(DRAM_WE_N), // .we_n .addres_nios_in_export(w_address_in_nios), // addres_nios_in.export .data_nios_in_export(w_data_in_nios), // data_nios_in.export .addres_nios_out_export(w_address_out_nios), // addres_nios_out.export .data_nios_out_export(w_data_out_nios), // data_nios_out.export .signal_nios_in_export({w_data_ready,w_data_ready_FS}), // signal_nios_in.export .signal_nios_out_export({w_data_ready_PE,reset}), // signal_nios_out.export .uart_0_rxd(RxD), // uart_0.rxd .uart_0_txd(TxD), // uart_0.txd ); Данные в eclipse считываю после возникновения прерывания по линии w_data_ready как: ... IOWR_ALTERA_AVALON_PIO_DATA(ADDRES_NIOS_IN_BASE, 0x00); aM[1][0].p_int = IORD_ALTERA_AVALON_PIO_DATA(DATA_NIOS_IN_BASE); ... Данные в плис пишу: ..... assign w_data_in = r_data_in; assign w_address_in = r_address_in; if(count == 4110) begin r_data_in <= out_conv; r_address_in <= 0; r_conv <= {{3'b001},{54'b0}}; end else; if(count == 4120) begin r_data_in <= out_conv; r_address_in <= 1; r_conv <= {{4'b0001},{53'b0}}; end else; .... При отладке в eclipse постоянно считываю нули. Подскажите, в каком направлении копать? Спасибо. -

Иголки

bva_rzn ответил bva_rzn тема в Языки проектирования на ПЛИС (FPGA)

Понял. Спасибо. -

Иголки

bva_rzn ответил bva_rzn тема в Языки проектирования на ПЛИС (FPGA)

Глупый вопрос. Разве при синтезе конструкция: r1 <= x; r2 <= r1; r3 <= r2; не образует конвейер? -

Иголки

bva_rzn опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день. Есть модуль, написанный на verilog, среда quartus 11, моделирование выполняется в model_sim_6_5. Запускаю RTL симуляцию - работает. Запускаю Gate Level симуляцию - появляются иголки на каждом клоке. Текст модуля: .... always @(posedge clk) begin if(!reset) .... else begin r_Ac <= {{2{Ac[11]}},{Ac[10:0]},{5'b00000}}; r_As <= {{2{As[11]}},{As[10:0]},{5'b00000}}; sub1res <= r_Ac - U0_fixed; sub2res <= r_As - U1_fixed; m1res <= sub1res * a1_fixed; m2res <= sub2res * a2_fixed; r_m1_out <= m1res[33:16]; r_m2_out <= m2res[36:16]; r1 <= r_m1_out; m3res <= r_m1_out * t_fixed; r4 <= r_m2_out; r2 <= r1; r_m3_out <= {{1{m3res[35]}},{m3res[35:16]}}; r7 <= r4; r3 <= r2; sub3res <= r7 - r_m3_out; r5 <= sub3res[17:0]; r6 <= r3; r8 <= r6; r9 <= r5; m4res <= r5 * r8; // (4.32) m5res <= r6 * r9; // (4.32) m6res <= r6 * r8; // (4.32) m7res <= r9 * r5; // (4.32) sub4res <= m4res - m5res; add1res <= m6res + m7res; data_out1 <= sub4res[33:16]; data_out2 <= add1res[33:16]; end end В veriloge пока не особо силён, если я правильно понимаю в схеме появляется комбинаторная логика. Идея борьбы с иголками понятна: привязка к клоку и использование синхронных регистров. Вроде так и делаю. Подскажите, пожалуйства, в чём может быть проблема? В прикреплённых файлах - результаты моделирования. Спасибо. -

фиксированная точка

bva_rzn опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день. Подскажите, можно ли настроить lpm_mult для работы с фиксированной точкой? Входные оперенды в формате 48 разрядов целая часть и 5 разрядов - дробная. Если можно, скиньте ссылки. Спасибо. -

megafunction

bva_rzn ответил bva_rzn тема в Среды разработки - обсуждаем САПРы

понял. Спасибо. -

megafunction

bva_rzn ответил bva_rzn тема в Среды разработки - обсуждаем САПРы

При запуске моделирования из Quartus Run EDA Simulation Tools->EDA Simulation Tools запускается modelsim, который начинает загружать библиотеки, скомпилированные в Quartus, что занимает время. Можно ли сделать так, что бы в modelsim эти библиотеки были сразу, т.е. не загружались бы каждый раз по-новому? Спасибо. -

megafunction

bva_rzn опубликовал тема в Среды разработки - обсуждаем САПРы

Доброго времени суток. Подскажите, где можно почитать про подключение альтеровских megafunction в modelsim. Библиотеки в Quartus 11 скомпилировал, скопировал в c:\altera\modeltech_10.1c. Добавил их в modelsim.ini по образу и подобию тех, которые там есть. Сгенерированные мегавизордом файлы для megafunction скопировал в рабочий проект в modelsim. При компиляции проекта в modelsim выдаётмся ошибка Module 'lpm_mult' is not defined. Спасибо. -

Помогите с конгстреймами

bva_rzn опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый вечер. Помогите с конгстреймом. Есть параллельный АЦП (25 МГц).Его тактирую от отдельного кварцевого генератора. С АЦП сигнал валидности данных (DV) тактирует ПЛИС (DE0-nano, Cyclone IV). Этот сигнал завожу на pll получаю 50 МГц и использую его для тактирования в SignalTap. Вот код: module Main (input clk,input [11:0] data_ADC,output clk_25,output clk_50,output lock,output [7:0] data); reg [7:0] tmp; reg [15:0] cont; pll pll1(.inclk0(clk),.c0(clk_25),.c1(clk_50),.locked(lock)); always @(posedge clk_25) begin if(lock) begin cont <= cont + 1'b1; if(cont == 16'b1111111111111111) tmp <= tmp + 1'b1; end end reg [11 : 0] adc_io_reg; reg [11 : 0] adc_reg; always @(negedge clk_25) begin if(lock) {adc_reg, adc_io_reg} <= {adc_io_reg,data_ADC}; end assign data = tmp; endmodule Файл sdc: set_time_format -unit ns -decimal_places 3 derive_clock_uncertainty create_clock -period 40.000 -name {clk} [get_ports {clk}] create_clock -period 40.000 -name {virt_clk} set_clock_groups -exclusive -group {clk virt_clk} derive_pll_clocks Вопрос: как описать описать тактирование по заднему фронту? Или сдвитуть по фазе clk_25? Как тогда описать? В SignalTap идёт один мусор. Спасибо.