woofer46

Участник-

Постов

59 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о woofer46

-

Звание

Участник

-

Добрый день, подскажите как можно сбросить прерывание по достижению в буфере приёма UART установленной границы - RDA (Receive Data Available). Каким регистром осуществляется сброс флага? Спасибо.

-

UART flex10k50RC240-4

woofer46 ответил woofer46 тема в Языки проектирования на ПЛИС (FPGA)

Как лучше сделать счетчик со сбросом? -

UART flex10k50RC240-4

woofer46 ответил woofer46 тема в Языки проектирования на ПЛИС (FPGA)

Почему асинхронное? -

UART flex10k50RC240-4

woofer46 ответил woofer46 тема в Языки проектирования на ПЛИС (FPGA)

До этого я использовал конечный автомат, на циклоне 3, но на flex он не заработал, после подачи питания первые 30 секунд работает, потом выключается -

UART flex10k50RC240-4

woofer46 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день, пытаюсь запустить юарт передатчик. Есть файл верхнего уровня - запускает юарт каждые 15 тактов. На вход модуля трансивера подаю константу - 24. Проблема в том что периодически бывают сбои (пропадает бит в середине) в отправляемых данных (скриншот), в чем ошибка или проблема? Спасибо! Top: module i2sToUart( clk_uart, uart_tx ); input wire clk_uart; output wire uart_tx; wire Reset; wire run_uart_command; Reset b2v_inst1( .clk(clk_uart), .nReset(Reset)); // reset out reg run; // Run UART reg [3:0] cnt1; always @ (negedge Reset or posedge clk_uart) begin if(!Reset) begin cnt1<=1'b0; run<=1'b0; end else begin cnt1<=cnt1+1'b1; if(cnt1<4'd4) run<=1'b1; else begin run<=1'b0; end end end assign run_uart_command = run; uart b2v_inst3( .nReset(Reset), .clk_uart(clk_uart), .run_in(run_uart_command), .data_in(8'd24), .out_tx(uart_tx) ); endmodule uart: module uart ( input nReset, input clk_uart, input run_in, // start transmitting input wire [7:0] data_in, // data to transmit output out_tx // serial Tx line ); reg[9:0] data; reg uart_busy; reg[1:0] srun_in; reg [3:0] cnt; always @ (posedge clk_uart) begin srun_in[1:0]={srun_in[0],run_in}; end assign en1=srun_in[1]&&!uart_busy; //enable for read data_in always @ (negedge nReset or posedge clk_uart) begin if(!nReset) begin data<=10'b1111111111; uart_busy<=0; end else begin if(en1) begin data[9:0]<={1'b1,data_in[7:0],1'b0}; // start+data+stop uart_busy<=1; end else if(uart_busy&&(cnt<9)) // while 10bit begin data[9:0]<={1'b1,data[9:1]}; // shift uart_busy<=1; end else begin uart_busy<=0; end end end always @ (negedge uart_busy or posedge clk_uart) begin if(!uart_busy) begin cnt<=0; end else begin cnt<=cnt+1'b1; end end assign out_tx=data[0]; endmodule Проверяю я не только логическим анализатором, но и контроллером (если пришедшее число не равно 24, то выдать его) -

К сожалению не помогло, взял на другом контроллере другие ножки ввода вывода - PC0, PC1, PC2 void main() { void main() { int i; MDR_RST_CLK->HS_CONTROL=3; while (MDR_RST_CLK->CLOCK_STATUS==0); MDR_RST_CLK->PLL_CONTROL=(11<<8)|(1<<2); MDR_RST_CLK->CPU_CLOCK=0x106; //CPU_CLK=HSE+PLL MDR_RST_CLK->PER_CLOCK|=(1<<20)|(1<<23)|(1<<24); // Open clk for SSP2, PORTC, PORTD MDR_PORTC->ANALOG|=1|(1<<1)|(1<<2); // PC0 - FSS, PC1 - CLK, PC2 - RX MDR_PORTC->FUNC=0x3F; // ReAF - PC0, PC1, PC2 MDR_PORTC->PWR=0x3F; // MDR_PORTC->OE=0; /*MDR_PORTD->ANALOG|=(1<<6); // PD6 - TX MDR_PORTD->FUNC=0x2000; // AF - PD6 MDR_PORTD->PWR|=0x3000; // MDR_PORTD->OE|=(1<<6); // PD6 - output */ MDR_RST_CLK->SSP_CLOCK|=(1<<25); // Enable SSP2 MDR_SSP2->CR0=15|(1<<4); // 16 bits, SPI TI page 339 MDR_SSP2->CR1|=(1<<3)|(1<<2)|(1<<1); MDR_RST_CLK->PER_CLOCK|=1<<21; MDR_PORTA->ANALOG|=(1<<6)|(1<<7); MDR_PORTA->FUNC|=(15<<12); MDR_PORTA->PWR|=(15<<12); MDR_PORTA->OE|=1<<7; MDR_RST_CLK->PER_CLOCK|=(1<<6)|(1<<7); MDR_RST_CLK->UART_CLOCK=(1<<24)|(1<<25); MDR_UART1->IBRD=41; MDR_UART1->LCR_H=(3<<5)|(1<<4); MDR_UART1->CR=(1<<8)|(1<<9)|(1<<0); while (1) { if((MDR_SSP2->SR&4)>0) { tx=MDR_SSP2->DR; while((MDR_UART1->FR&64)!=0); MDR_UART1->DR=tx; } } } Баги такие же 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 57 58 59 60 61 62 63 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 59 60 61 62 63 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 51 52 53 54 55 56 57 58 59 60 61 62 63 0 1 2 3 4 5 6 7 9 10 11 12 13 14 15 16 52 53 54 55 56 57 58 59 60 61 62 63 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 53 54 55 56 57 58 59 60 61 62 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 55 56 57 58 59 60 61 62 63 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 56 57 58 59 60 61 62 63 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 57 58 59 60 61 62 63 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 59 60 61 62 63 0 1 2 3 4 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 51 52 53 54 55 56 57 58 59 60 61 62 63

-

Спасибо, cейчас для прошивки использую PD1/TCK и PD0/TMS PD2 используется для приема по SSP. Соответственно если я линии программатора переопределю на JTAG A (MODE=001), то возможно проблема пропадет?

-

Вообще один из пинов предназначен для JTAG, но я использую SWD

-

Добрый день! Может кому-то приходилось работать с российским контроллером ARM Cortex M3, не могу разобраться почему SSP (SPI Texas Instruments) в режиме slave, нестабильно работает. Передаю данные с частотой 1.5 Мбит, но некоторые данные стабильно теряются, в чем может быть ошибка? void main() { ....................................................... MDR_RST_CLK->PER_CLOCK|=(1<<20)|(1<<23)|(1<<24); MDR_PORTD->ANALOG|=(1<<2)|(1<<6); MDR_PORTD->FUNC=0x2020; MDR_PORTD->PWR|=0x3030; MDR_PORTD->OE|=(1<<6); // PS! PD5 is broken! Not work! MDR_PORTC->ANALOG|=1|(1<<1); MDR_PORTC->FUNC=0x0F; MDR_PORTC->PWR|=0x0F; MDR_RST_CLK->SSP_CLOCK|=(1<<25); // Enable SSP2 MDR_SSP2->CR0=15|(1<<4); MDR_SSP2->CR1|=1<<2; // Slave MDR_SSP2->CR1|=1<<1; // Start SSP2 ................................................................... } while (1) { ............... while((MDR_SSP2->SR&4)==0); tx=MDR_SSP2->DR; while((MDR_UART1->FR&64)!=0); MDR_UART1->DR=tx; ............... } В SSP передаю счетчик от 0 до 63, на выходе UART получаю со сбоями: 0 1 2 3 4 5 6 7 8 9 10 11 12 13 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 0 1 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 0 1 2 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 0 1 2 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 0 1 2 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 0 1 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 0 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 0 1 2 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 37 38 39 40 41 42 43 44 45 46 47 Спасибо!

-

CLK domain crossing

woofer46 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

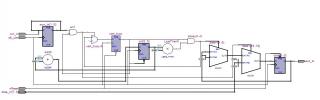

Здравствуйте! Столкнулся с проблемой: Мне необходимо из частоты 8МГц передать данные и флаг в частоту 30Мгц, я ставлю 2 д-триггера, так как переход из частоты в частоту. module(); always@(posedge CLK_8MHz) begin // . . . DATA_PRELOAD[19:8]<=DATA_KEEP[11:0]; start<=1'b1; // . . . end reg [1:0] s_start; reg [23:0] sPRELOAD1; reg [23:0] sPRELOAD2; always@(posedge CLK_30) begin s_start [1:0]<={s_start[0], start}; //Синх флага sPRELOAD1<=DATA_PRELOAD[31:8]; // Синх данных sPRELOAD2<=sPRELOAD1; end always@(posedge CLK_30) begin // . . . if(s_start[1]) DAT<=sPRELOAD2[numbit]; // . . . end endmodule Clasic Timing Analyzer, мне выдает следующие ошибки, и я ничего не могу с ними поделать, что это значит? Правильно-ли я делаю? Спасибо. -

Спасибо, хорошие статьи, сейчас я работал не с TimeQuest, а c ClasicTimerAnalyzer, буду пытаться настроить TimeQuest чтобы подробнее узнать об источнике задержек

-

master

-

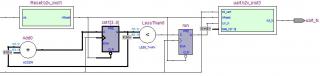

Есть модуль ControlSpi, в нем лежат те данные которые надо отправить по SPI, и этот модуль рулит сигналом отправки байта для SendSPIByte. SendSPIByte отправляет данные на частоте 5МГц SPIsendByte.v ControlSPI.v Спасибо

-

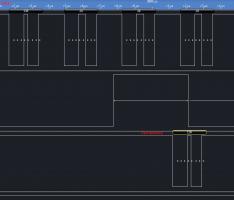

Timing Analyzer Quartus

woofer46 опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте! Подскажите, что значат следующие ошибки в Timing Analyzer Правильно-ли я понимаю, что в столбце Actual Time пишется максимальная частота на которой может работать скомпилированный модуль (58МГц)? Куда копать для исправления таких ошибок? Спасибо!