-

Постов

27 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о AiS

-

Звание

Участник

- День рождения 18.04.1985

Информация

-

Город

Array

-

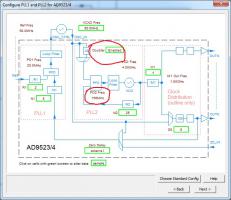

Доброго всем времени. прошу прощение за молчание. проблема вроде бы разрешилась. ну или хотя бы частично. проблем было две - с VCXO и с кодом. Проблема VCXO в том, что он имеет слишком маленький диапазон перестройки. Пытаясь синхронизоваться с 50МГцовой опорой, напряжение на подстраиваемой ножке VCXO просто уходило в зашкал. итог - PLL1 не в LOCk моде. При подаче в качестве опоры сигнала в 80МГц, сгенерированного аналогичным VCXO, PLL1 сразу входит в LOCK. (разумеется, при перерасчете соответсвующих делителей) Второй вариант решения мог быть при подключении вместо VCXO опорного сигнала в 50МГц. Но это фактически просто работа без PLL1 PLL2 не входил в LOCK по следующим причинам: 1. в даташит есть пункт MAXIMUM PFD FREQUENCY Antibacklash Pulse Width Minimum and Low 250 MHz Maximum and High 125 MHz у меня в регистре, где задается Antibacklash Pulse Width был указан максимум плюс был включен удвоитель частоты VCXO то есть на PFD приходила частота 160МГц, что противоречит указанным нормам. Тут просто надо было выключить удвоитель и пересчитать соответсвующий делитель (N2 на схеме) 2. Есть регистр "PLL2 charge pump control", если его не описывать, то ток устанавливается минимальный. ставлю его хотя бы в середину шкалы и вуаля - PLL2 входит в LOCK Наверное, для тех, кто с кристаллом не работал, вообще ничего не понятно отсюда. Для улучшения понимания приведу картинку с ADIsimCLK, хотя не уверена, что сильно поможет. Но из нее хотя бы наглядно видно, что есть удвоитель и PFD. В любом случае, вдруг кто будет мучиться с тем же? что и я, и тогда может кому-то это все пригодится.

-

ViKo, в регистрах, помимо делителей и фильтров, рассчитываемых с помощью ADIsimCLK, так же задается еще ряд параметров. так что возможно там что-то выполняется не корректно. например калибровка VCO, либо же какие-то еще управляющие регистры. собственно у меня расчет был на то, что вдруг кто уже работал с данным кристаллом и сталкивался с подобным. на счет опоры - смущает только то, что точно такие же модули синхронизации используются в аналогичной системе, правда в той системе вместо AD9524 использовался AD9518. И с ним все работает. В том числе и то, что оба ПЛЛ входят в LOCK так что я, честно сказать, в некотором ступоре. есть подозрение, что во всем виноват кристалл VCXO (во всяком случае в AD9518 он внутренней, может потому и проблем не было...) VCO, Да постскриптум был оставлен через пару минут, пока в ветке ни одного ответа даже не было. Проект завтра выложу. просто руки не дошли уже сегодня

-

_Vova, так я, собственно, через ADIsimCLK все и рассчитываю...

-

_Vova его и в одном модуле нет.

-

Kompot да в том-то и оно, что я не могу сказать, чтоб REF был искажен. VCO все модули располагаются в крейте ratiopacPRO-air 24572-031 фирмы Schroff. Синхроимпульсы до каждого модуля передаются по оптоволокну. polyakovav есть такое. я даже не спорю, что могу что-то задавать не так или не корректно. на всякий случай прикрепляю док с моими регистрами, вдруг кто чего увидит. Ahdl1.pdf

-

проблемы с синхронизацией при помощи AD9524

AiS опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Добрый день! Проблема у меня следующая. Существует система из восьми 2ГГц модулей АЦП, которые должны работать в режиме жесткой синхронности. Каждый модуль АЦП построен на базе 4х кристаллов ADS5463 с частотой дискретизации 500МГц, включенных в параллель. Частота дискретизации каждого следующего АЦП сдвинута относительно предыдущего на 90 градусов. Для формирования частоты дискретизации и ее сдвигов используется кристалл AD9524. На рисунке дано пояснение: Итак, при запуске одного модуля проблем не возникает, частоты формируются, фазовый сдвиг выполняется корректно. Проблемы начинаются при запуске системы из 8 модулей. Существует так называемая плата синхронизации, с выходов которой на каждый модуль АЦП приходит единая опорная частота (50МГц). Эта частота подается на входы REF кристалла AD9524. (рис) В качестве внешнего VXCO в каждом модуле АЦП стоит 80МГц CVPD-920. По идее, при организации такой системы все модули между собой должны работать синхронно. Но они так не работают!!! Каждый живет свей жизнью. Ко всему прочему складывается впечатление, что у каждого кристалла AD9524 формируется своя частота дискретизации, типа у одного 500МГц, у другого 500 с небольшим. Потому что при подаче на входы 8 модулей одного и тот же сигнала, видно, что сдвиг между ними не постоянный, а увеличивающийся со временем. не знаю, понятно удалось изложить суть проблемы или нет, но попробую приложить еще пару иллюстраций: На первом показан начальный сдвиг фаз между двумя модулями, на втором - сдвиг фаз спустя 16 периодов 240нс сигнала. На последнем видна асинхронность регистрации одного и того же входного сигнала при едином внешнем запуске. P.S. При более детальном изучении выяснилось, что состояние обоих PLL у AD9524 находится в UNLOCK моде. Но как с этим бороться и почему он не входит в LOCK я не могу понять:( Надеюсь на помощь более опытных и грамотных специалистов! -

всем спасибо за советы и ответы! причину нестабильности правильно описал faa вот здесь http://electronix.ru/forum/index.php?s=&am...st&p=951533 так как было поздно делать переразводку, дабы принимать данные по входным клокам, сделала проще: подала выходные синхроимпульсы первого АЦП на PLL и дабы ничего не переделывать в проекте сформировала 250 мегагерцовые частоты для остальных каналов со сдвигом в 0.5 наны между каналами. По включении один канал все еще отставал на такт, но на этот раз это оказалась стабильная задержка. TimeQuest показал, что не успевает сформироваться сигнал разрешения записи в память для данного канала. мультицикл помог разрешить эту проблему. Проблема правильного описания сдвига между входными частотами отпала сама собой, после заведения PLL. Хотя, судя по всему, для первоначальной схемы вот это является верным: На данный момент все работает!

-

faa, похоже ноги нашей проблемы растут именно отсюда (еще раз спасибо, что обратили мое внимание!!!). опять-таки у меня дш на ads5463 хранился еще за 2006 год, а там этой инфы не было, соответственно можно было еще очень долго причину искать. если не секрет, как именно обходили? использовали входные клоки для приема? нам уже поздно так делать, плата смонтирована... я вот пока хочу попробовать подцепить 500МГц на матрицу и через внутренний PLL организовать частоты для приема данных с каждого АЦП

-

у меня на 36 стр faa, спасибо за комментарий, завтра буду все проверять, может действительно в этом причина

-

faa, хотите сказать, что даже если частоты дискретизации были синхронизованы на входах АЦП, на выходах они могут быть какие угодно?

-

пришла идея описать входные клоки вот так: create_clock -name {clk_a} -period 2.000 -waveform { 0.000 1.000 } [get_ports {clk_a}] create_clock -name {clk_d} -period 2.000 -waveform { 0.500 1.500 } [get_ports {clk_d}] create_clock -name {clk_b} -period 2.000 -waveform { 1.000 2.000 } [get_ports {clk_b}] create_clock -name {clk_c} -period 2.000 -waveform { 1.500 2.500 } [get_ports {clk_c}] не знаю верно или нет, но вроде бы так они стоят именно сдвинутыми на 0.5 нс. Однако общую картину это не исправило. Где-то в DDR происходит разная задежка между каналами при выдачи данных. То есть, например, данные из первого канала DDR приемники обрабатывают два такта, а из второго - три спасибо за ссылку, попробую изучить

-

ну разумеется нужна дополнительная обработка, хотя бы по амплитудной калибровке, по сдвигам нуля и пр. но для начала, я хочу, чтобы все 4 измерения, относящиеся к одному периоду, действительно являлись таковыми. про два канала - возможно так и есть. у меня 2-3 канала могут работать нормально, а 1-2 отставать на один или пару тактов. причем от компиляции к компиляции количество каналов и сами каналы могут меняться

-

на каждый канал - своя. а разница - есть, так как в дальнейшим я эти 4 RAM читаю одновременно, и важно, чтобы в одинаковых адресах памяти хранилась информация, относящаяся к одному и тому же периоду измерений. так как дальше я собираю из этих данных один сигнал, соответсвующий измерениям на частоте 2ГГц. Если по одному из каналов произойдет сдвиг хотя бы на такт (что сейчас и происходит), то соответственно восстановленный сигнал будет уже не верен. опять таки от сдвига фаз зависит порядок приема данных. то есть при восстановлении я, читаю данные, например, из первого адреса всех четырех RAM в такой последовательности: 1 RAM,2 RAM,3 RAM ,4 RAM. Если сдвиг фаз не обеспечивается при записи в RAM, то данные могут не соответствовать в действительности должному порядку записи. не знаю, понятно или нет получилось описать

-

ну, собственно, я так же понимаю, что Fitter разводит матрицу, исходя из рекомендаций TimeQuest`а. А далее можно увидеть удалось это ему или нет. Собственно, если я прописываю в TimeQuest, что вот этот сигнал должен быть задержан относительно этого, Fitter будет стараться это сделать. Другое дело, если у меня есть уже задержанные друг относительно друга сигналы (4 клока АЦП), как мне описать, что они друг относительно друга задержаны? ибо, если я этого не сделаю, то quartus будет считать, что приходят они фронт в фронт и, собственно, если я буду задавать какие-то дальнейшие правила относительно сигналов, распространяющихся по этим клокам, fitter не сможет их выполнить. если я где-то в рассуждениях ошибаюсь, поправьте. что касается картинки, она вроде описывает, организацию сдвига на четверть периода. но это описание сдвига, созданного внутри матрицы, как я понимаю

-

ага, уже изучено. собственно, с этого и начиналось. но вопрос остался. как мне описать клоки, идущие снаружи, не сгенерированные внутри системы, сдвинутые друг относительно друга на 0.5 нс? ElectroKarp А чем мне может set_multicycle_path помочь? как я понимаю, он позволяет организовывать задержки внутри, но мне не нужно что-либо задерживать внутри, мне нужно описать уже задержанные клоки. Хотя, возможно, это я чего-то не понимаю?