-

Постов

1 951 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о sonycman

-

Звание

Любитель

- День рождения 06.09.1977

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Retained

-

Звание

Array

Посетители профиля

15 832 просмотра профиля

-

Приветствую! Коллеги, если у кого-то вдруг имеется схема или другая документация на модули фирмы Enclustra, в частности Mercury XU5 и материнской платы Mercury+ ST1 - нижайше прошу поделиться. Мануал их сайт даёт скачать без проблем, но схему нет - запрашивают фирму\адрес\и т.п., а я физ. лицо, не светит мне ничего... :(

-

Чертовщина творится. Убрал схему VGA выхода - PLL стала стабильно выдавать 32 МГц, выше пока не пробовал. До этого выше 29 МГц не поднималось. Что изменилось в разводке - если раньше в моей схеме был один MMCM и одна PLL в одном CMT блоке, то теперь вивадо развёл их по разным CMT, на разных сторонах чипа. Плюс раньше вивадо в цепи заворота тактовой между IOBUF и входом PLL вставлял BUFG, то теперь его нет. Больше вроде ничего не поменялось. Как объяснить повышение частоты PLL?

-

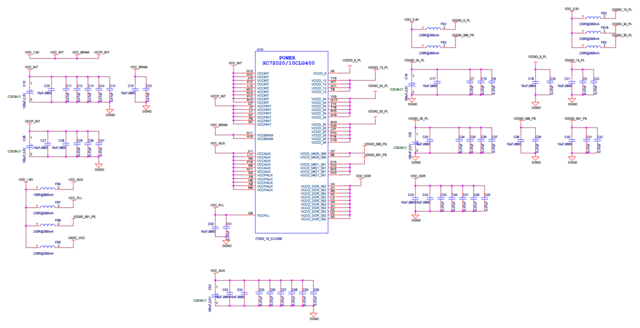

Плата используется такая: Z-Turn v1. Вот схема питания: Настройка пина: LVTTL, FAST, 8ma. Можно попробовать настройку с бОльшим током... Дифф. стандарт тоже пока не пробовал, надо глянуть в эту сторону. В этом-же банке работает VGA выход на 28.5 МГц, который можно выключить, в принципе. По поводу фазового шума, думаю, вся эта идея не укладывается в спецификацию. В настройке PLL джиттер выставил по максимуму - 1 нс. Какой он там по факту - не скажу, но вероятнее всего поболее будет. Есть ещё идея уменьшить разрядность oserdes с 8-ми до 6-ти бит, то есть снизить коэфф. умножения до 6-ти, чтобы уменьшить входную частоту PLL. Но джиттер в этом случае только вырастет, мне кажется.

-

Работает без проблем с часотой до 29 МГц, выше PLL не лочится и нормального клока на ее выходе нет. Получается,, входной пин не берет частоту выше 232 МГц (29 * 8)?

-

Beby Благодарю за помощь, собралось, когда PLL инстанциировал как у Вас, в исходнике, а не через блок-дизайн. Дальше пришлось пин, через который генерируется клок, повесить на свободно висящий пин чипа, иначе 250МГц уже не схватывается входным буфером. Всё заработало, 576р @27МГц монитор подхватил как родные! С 32 битным счётчиком такой генератор позволит мне подгонять частоту с отклонением менее наносекунды от кадра к кадру!

-

А если попробовать полноценный oserdes и завести CLK_2 на вход pll?

-

Для идеального выравнивания сигналов по времени фрейма делаю HDMI клок чуть быстрее, а лишние такты клока блокирую через BUFGCE. Не получается без вывода клока наружу. Только используя два пина - выходной и входной...

-

Видеосигнал VGA, различной частоты.

-

Только для проверки. Мне нужно генерировать частоту под входящий различный видеосигнал и синхронизироваться под него с точностью до нескольких сотен наносекунд на фрейм. На такое куцые ФАПЧ простого цинка не способны, к сожалению...

-

Да всего 27 МГц. По осциллографу клок вполне ровный, частота по осциллографу 26.96, видеосигнал 576p 50 герц. Монитор на него не реагирует. Беру клок такой-же частоты с PLL цинка (без хитрого генератора), подаю на схему вместо сгенерированного - все работает. На ultrascale есть периферийный блок display port с отличным генератором частоты, у пятых циклонов отличные PLL с 24 битным фракционным делителем, а вот у простого цинка нихрена подходящего 😞 Придется ставить внешний синтезатор частоты.

-

Именно с этого-же пина: IOBUF genclkio(.I(w_pin), .IO(io_pin), .O(pll_input), .T(1'b0)); w_pin - выход oserdes, pll_input - вход PLL. Статья довольно мутная, не знаю, где там автор проверял на практике. Проблему решил, использовав два пина. Идея, в общем-то работает, ФАПЧ лочится, но такой клок как пиксель клок видеосигнала использовать не получилось - монитор не распознаёт сигнал. Видимо, слишком большой джиттер...

-

Приветствую. Пытаюсь реализовать генератор частоты для подстройки под различный видеосигнал. У цинка весьма ограниченные PLL с куцым 3 битным дробным делителем, которые не могут сгенерировать производьную частоту. Наткнулся на вот такую статью: Breaking all the rules to create an arbitrary clock signal Смысл там в том, чтобы генерировать клок на обычной логике, на счетчике, а потом, прогнав его через oserdes (умножив, как я понимаю, его на 8 для снижения фазового шума), подать на вход PLL, которая снизит джиттер и уже этот сигнал использовать для тактирования. Попробовал в железе - роутер не может развести выход oserdese2 на вход pll. То есть не получается вывести на внешний пин сигнал с сериализатора, и потом с этого же пина завести этот сигнал на вход pll. Это я что-то делаю не так, или действительно это не возможно?

-

Ultrascale имеет когерентные порты, работа через которые позволяет обойтись без инвалидации кэша. По крайней мере в baremetal это работает.

-

Как это нет? Да в том-же xfsbl_main.c функция main: XFSBL_STAGE3: Load the partitions: XFsbl_PartitionLoad - загрузка пользовательской программы. XFSBL_STAGE4: Handoff to the applications: XFsbl_Handoff - запуск программы. Всё это находится за 5 минут 👀

-

После загрузки пользовательской программы, FSBL передает управление ей - переходом по адресу Entry point. Вроде бы доки в сети доступны, курите их и закрепляйте практикой.