Icedevil777228

Участник-

Постов

21 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Icedevil777228

-

Звание

Участник

Посетители профиля

483 просмотра профиля

-

Да получил статьи спасибо, они мне очень помогут. Можно и заблочить, но это на крайний случай.

-

Я открывал Чип Планер смотрел, а что толку? .... что сравнивать ? постой маленький проект с большим, да они очень разные. Вообщем сравнение мне ничего не дало.

-

В PLL есть функция задержки сигнала.

-

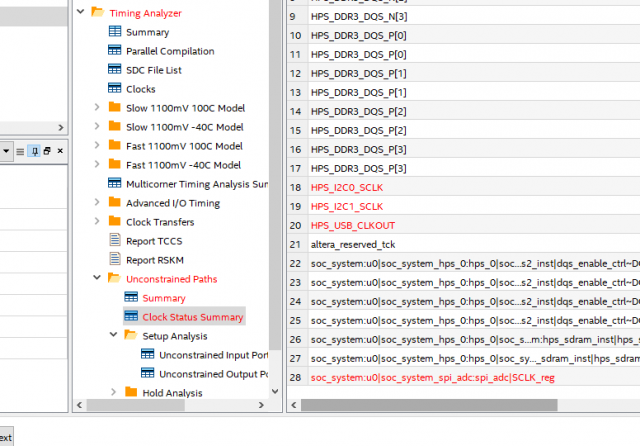

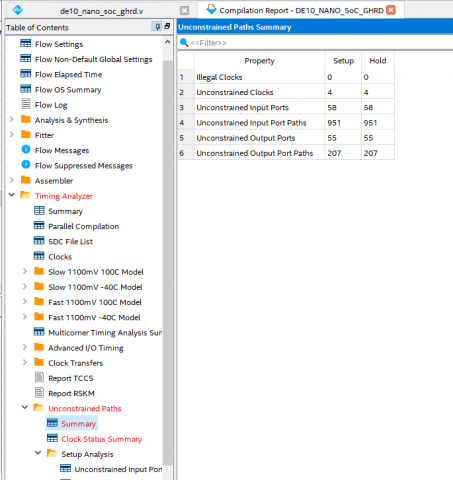

Вообщем как проект отлаживать то..... ? Я могу сделать 4 клока. clk1, clk2,clk3,clk4. Первый clk1 на NCO без задержек, clk2 подать на фильтр на линию задержки и задержать на четверть периода относительно clk1, clk3 подать на умножители в фильтре и задержать еще на четверть периода относительно clk2, clk4 подать на cумматоры и задержать еще за четверть периода относительно clk3. И тогда данные будут успевать устанавливаться, так кто-нибудь делал? Или когда с сделаю этот sdc файл он сам задержит нужные клоки в нужных местах? как работает этот sdc файл?

-

5 МГц это частота сигнала, а NCO у меня на RAM и работает от clk 300мГц. Я добивался что бы она работала без помех, но это в тестовом проекте. Когда я интегрирую ее в основной проект она перестает работать без помех даже от clk 50 Мгц.

-

Проблемы с отладкой проекта.

Icedevil777228 опубликовал тема в Работаем с ПЛИС, области применения, выбор

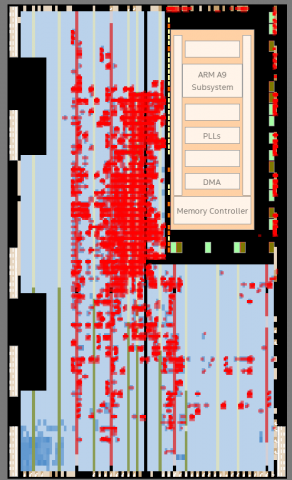

Я занимаюсь ПЛИС уже 2 года, и дошел до сложных проектов, которые просто так не работают на больших частотах. Вот так выглядит мой проект, он реализует управление РЛС, посредством различных интерфейсов. Его центром является система ЦОС состоящая из КИХ фильтра и NCO, все написано на Verilog. У меня возникла проблема, на выходе NCO (управляемый генератор синуса) и Фильтра вылезают помехи. Если отделить систему ЦОС от всего проекта, то помехи мне удавалось убрать, я задерживал clk идущий на NCO на 333ps и все отлично работало, в большом проекте я не могу подобрать задержку. Если с АЦП подать сигнал на фильтр, то на выходе фильтра он будет с помехами. Если снимать сигнал с NCO, то помехи так же присутствуют. Как они выглядят я записал на видео. Бывало, что помехи на фильтре пропадали, а на NCO появлялись и наоборот. Я понимаю, что проблемы в задержке сигнала, но я никогда не работал с Timing Analysis и не знаю с чего начать. Подскажите как решаются такие проблемы? Video_2019-07-19_164140 (online-video-cutter.com) (1).mp4 Video_2019-07-19_164140 (online-video-cutter.com) (1).mp4 Вот я задержал clk на NCO, фильтр заработал без помех, но на выходе NCO как-будто один из младших битов не успевает устанавливаться. Video_2019-07-22_115914 (online-video-cutter.com).mp4 -

Я первый день работаю в 17м Квартусе, реально не могу просимулировать выдает ошибку, может вы знаете....

-

. Я вот думаю над этим, а где и как лучше проверить работу блока ?

-

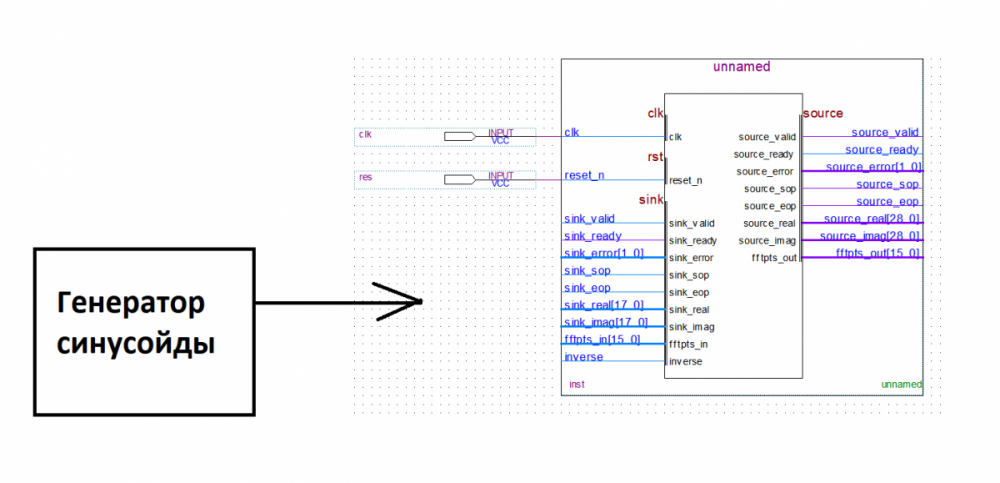

Я могу этот блок FTT в матлаб отправить или в моделсим. gen_cos_tb.txt

-

Вообщем последний вопрос можно закрыть! Я выкинул свой старый комп с 32 win 7 , взял поновее поставил современную версию Quartus 17.0, взломал ее. Зашел в Qsys сгенерировал блок FFT. Прошу прощение за мою назойливость, но мне нужно как можно быстрее развиться в данном вопросе! Напишите в Лс, кто авторитарен в вопросах работы с ядром FFT. Вообщем у этого ядра много входов и выходов которые мне ненужны. Я видел проекты где блоки FFT имеют свои блоки управления, которые им разрешают работать в определенные моменты времени, а так же на выходе процессоры, которые обрабатывают информацию, н омне для начала нужно сделать элементарный проект. Как мне сделать простой проект, где будет генератор синусоиды, который выдает например двоичный 12 битный прямой код за 32 отсчета. Вот, например, 5 точек из 32 в десятичной системе [2047 - 4095 - 2047 - 0 - 2047]. Я правильно понимаю код с синусоиды нужно подавать sink_real ? Что с остальными входными и выходными портами делать, какие из них нужно на 0, какие на 1 или может вообще не трогать? ? На выходе ожидаю получить нечто подобное:

-

Зависает на моменте Generating Megacor function top-level. Еще в интернете советуют в диспетчере задач удалить процесс quartus map , тогда программа отвисает, ядро "типа" компелируется, но сам блок ядра в схемотехническом редакторе не появляется.

-

Всем спасибо, за наводки я разобрался и сделал свой блок БПФ, теперь мне предстоит сделать блок БПФ, работающий в режиме реального времени например на 32768 точек. Я осознаю, что такой блок мне не написать руками, поэтому собираюсь использовать готовые ядра в Квартусе! Чем отличается ядро FFT в старых версиях, который находится в мега функциях от того что в Qsys? Есть версии Квартуса, где можно ркально реализовать блок FFT без лицензии в Web Edition? Вообще кто в каких версиях делал блок FFT и какие семейства ПЛИС использовал? У меня версия 13.1 но ядро не компелируется, процесс компиляции зависает, даже во взломанной версии (отдельное спасибо Burenkov за таблетку), так же зависает Fir Compiler. У меня два предположения почему зависает на моменте Generating Megacor function top-level это использование 32 битной WIN7 или я выбираю кристалл ПЛИС в котором невозможно генерировать ядро. В Квартусе 9.1 компелируется, но в железо не зашивается требует лицензию. Главный вопрос что бы бесплатно реализовать FFT в какой либо версии Квартуса его обязательно нужно взломать или нет? Есть смысл использовать Qsys ? Ну и кто нибудь сталкивался с процессом зависания ?

-

Она платная. У меня все проекты в версии 13.1. Знаете как взломать?

-

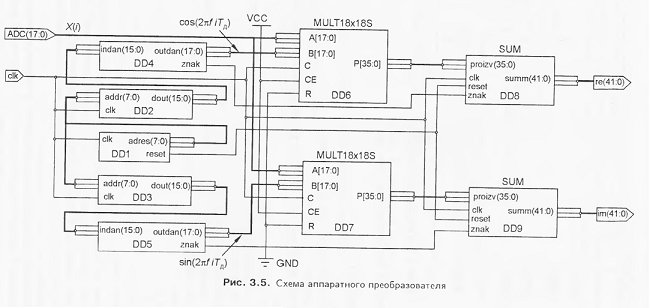

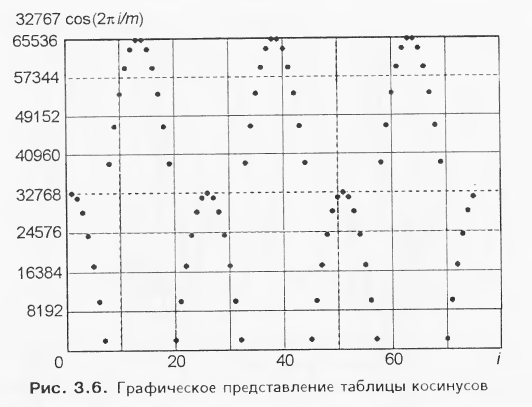

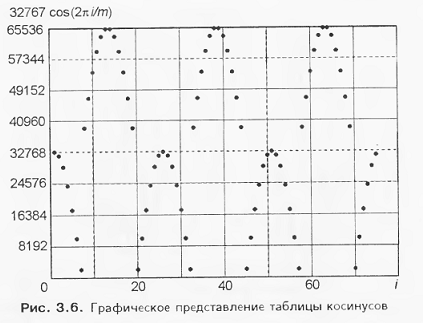

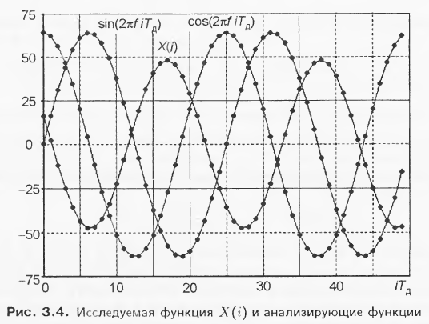

В книге Тарасова Потехина: Разработка систем цифровых сигналов на база ПЛИС на 73 странице описывается самый простой алгоритм, что я нашел, но без объяснения многих вещей. С сумматорами (DD8,DD9), умножителями(DD6 DD7) и сo cчетчиком(DD1) все понятно в книги даже приведены их VHDl коды. Помогите разобраться с DD2 DD3 на них нету кодов, их описывают как ПЗУ в которых хранятся таблици косинусов(DD2) и синусов(DD3) . Еще в книге даны эти графики в качестве подсказки, но почему то для sin отдельного графика нет. И теперь вопросы: 1 Как можно умножая на значения Сos и Sin получить спектр сигнала? 2 Я рассматривал много примеров, везде говорилось об операции "бабчока" это она и есть или как? 3 В источниках пишут БПФ по 8 / 16 / 64 /1024 точкам а у нас то что? 4 Подскажите как все - таки написать блоки DD2 DD3 5 Допустим я сделаю блоки DD2 DD3 мне нужно выход реальный выход сумматора подать на ЦАП и я сразу получу спектр синусоиды которая идет с АЦП ?

-

БПФ FFT

Icedevil777228 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Передо мной стоит задача реализовать БПФ на ПЛИС на VHDL, многие скажут, что в гугле миллион разных вариантов, я за два дня поисков не нашел подходящий вариант, т.к. основная честь "самописных ядер" очень сложна для понимания, другая часть заточена под Xsilinx, где все время идет речь о встроенных блоков умножения и памяти. Еще много простых кодов, но совсем без описания. Или варианты описаны очень абстрактно, а у меня есть конкретная задача имеется АЦП 12 бит и Cyclone 3. Я формирую синусоиду с выхода ЦАП она идет на АЦП затем необходимо преобразовать ее в СПЕКТР. Нужно сделать максимально маленький и простой проект, но главное с ПЛИС вывести спектр на 2й ЦАП и на осциллограф. Может кто подскажет хорошую книгу, или есть готовые решения, но с хорошим описанием.