BSACPLD

Свой-

Постов

863 -

Зарегистрирован

-

Посещение

-

Победитель дней

3

BSACPLD стал победителем дня 9 января

BSACPLD имел наиболее популярный контент!

Репутация

9 ОбычныйИнформация о BSACPLD

-

Звание

Знающий

- День рождения 16.06.1986

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

8 894 просмотра профиля

-

А ID чипа Artix-7 не проверяет?

-

В списке её нет. Но в моей плате реализован механизм удалённой перепрошивки через Ethernet. Главное чтобы с конфигурированием проблем не было.

-

BSACPLD подписался на W25Q64JVSSIQ и Artix-7

-

W25Q64JVSSIQ и Artix-7

BSACPLD опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, подскажите, пожалуйста, подойдёт ли W25Q64JVSSIQ для конфигурирования Artix-7? Может я слона в упор не вижу, но я перерыл весь datasheet и не нашёл конкретных значений ID code... UPD. Точно я не выспался... 16h 4017h -

Вставлю свои 5 копеек. Сейчас доступно: 1. Gowin как уже было выше сказано. Для задач с выскоми тактовыми частотами они не подходят. Проект что у меня на Xilinx спокойно собирается на 150 МГц, в Gowin едва ли вытягивает 60-70 МГц. 2. Fudan Частичный клон Xilinx. Не совместимы по распиновке с оригинальными Xilinx. Но зато частично совместимы с Vivado. Есть и своя собственная среда разработки. Все было бы хорошо, если бы не адово количество брака в поставке. В партиях 2021/2022 года брак 1%. В партии 2023 года брак 30%. В партии 2024 года брак 59%. Важно отметить, что схемотехника/топология в части ПЛИС/питания не менялись - это одно и то же изделие с минимальными модификациями в части заменить разъём, обновить Ethernet чип на новую ревизию. Брак проявляется в виде некорректной загрузки прошивки при отрицательных температурах (сам Fudan -40...+85 согласно datasheet). ПЛИС банально не проходит верификацию загруженной прошивки. 3. PangoMicro pin-to-pin с Xilinx, но среда разработки полностью своя. Отладочные платы доступны на AliExpress. Чипы пока едут. По частотам на 10-20% выше Xilinx/Fudan. 4. Б/У Xilinx после реболлинга. Доступны на AliExpress по вменяемой цене, но нужно брать у проверенного продавца чтобы не нарваться на совсем уж трэш. Также отдельные варианты доступны в Чип и Дип по не адекватной цене 10x от номинала.

-

Это очень жирно 🙂 Я уже сделал свои функции и устройство уже в серии. Тему можно закрывать.

-

Немного оффтоп, но у того же человека есть весьма неплохие корки для AXI: https://github.com/alexforencich/verilog-axi https://github.com/alexforencich/verilog-axis Использую их вместо корок от Xilinx - проект легко переносится хоть на PangoMicro, хоть на любого другого производителя. Тоже рекомендую к использованию.

-

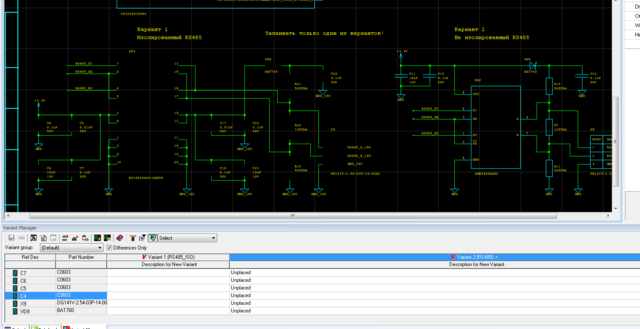

Коллеги, решил я тут попробовать Variants чтобы не прописывать руками что паять, а что нет. С генерацией BOM вопросов нет. Есть вопросы по схеме. Как сделать чтобы не используемые компоненты были зачеркнутые, а не просто становились невидимым? Версия EEVX2.7.

-

Чип слишком маленький чтобы туда сразу и Ethernet и PCIe пихать. Один только AXI Memory Mapped To PCI Express занимает 11911 LUT и 16 BRAM.

-

А если быть совсем точным, то не реально. Специалистов универсалов с глубокими знаниями хотя бы по 3 направлениям найти практически не реально - все уже давно пристроены. И ценник на таких специалистов начинается от 400К. И каждый такой специалист ооочень специфичен в общении, т.к. знает себе цену.

-

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

Причем тут маркировка? Они все по datasheet -40 обеспечивают. Брак чипов - замена сколько есть со склада и возврат денег за остальные. Новую партию сами заказали напрямую из Китая. -

А чем Вас готовый и отлаженный модуль не устраивает? Вот, например: https://github.com/alexforencich/verilog-i2c Сам я не любитель использовать чужой код, но этот модуль написан на мой взгляд весьма неплохо. Использую его уже третий год в своих проектах - пока никаких проблем не было. Да и документирован он довольно неплохо.

-

Решил я проблему с зависанием при выполнении кода из ОЗУ. Было: while(FLASH->STATR & SR_BSY); FLASH->CTLR &= ~CR_PAGE_PG; Стало: while(FLASH->STATR & SR_BSY); for (uint8_t i=0 ; i<10 ; i++) __asm__("nop"); FLASH->CTLR &= ~CR_PAGE_PG; Как я и предполагал, между сбросом флага SR_BSY и записью в FLASH->CTLR должна быть некоторая задержка.

-

Это Вы не понимаете, что ВЕСЬ код в 2КБ ОЗУ физически не помещается. Я уже писал Вам об этом.

-

0x08003FC0 Все define скопированы из SPL ch32v00x_flash.c как есть, я ничего не менял. Я просто скопировал к себе код из фирменной ch32v00x_flash.c добавив в свой flash.h атрибуты для размещения в RAM, и добавил к названиям функций RAM_* чтобы они не перекликались с функциями из фирменной библиотеки. К тому же судя по коду фирменных функций FLASH_BANK1_END_ADDRESS нигде не используется.

-

Я скопировал код из библиотеки SPL 1 в 1. Там только флаг SR_BSY проверяется. void RAM_FLASH_Unlock_Fast (void) { /* Authorize the FPEC of Bank1 Access */ FLASH->KEYR = FLASH_KEY1; FLASH->KEYR = FLASH_KEY2; /* Fast program mode unlock */ FLASH->MODEKEYR = FLASH_KEY1; FLASH->MODEKEYR = FLASH_KEY2; } void RAM_FLASH_ErasePage_Fast (uint32_t Page_Address) { if((Page_Address >= ValidAddrStart) && (Page_Address < ValidAddrEnd)) { FLASH->CTLR |= CR_PAGE_ER; FLASH->ADDR = Page_Address; FLASH->CTLR |= CR_STRT_Set; while(FLASH->STATR & SR_BSY) ; FLASH->CTLR &= ~CR_PAGE_ER; } } void RAM_FLASH_BufReset (void) { FLASH->CTLR |= CR_PAGE_PG; FLASH->CTLR |= CR_BUF_RST; while(FLASH->STATR & SR_BSY) ; FLASH->CTLR &= ~CR_PAGE_PG; } void RAM_FLASH_BufLoad (uint32_t Address, uint32_t Data0) { if((Address >= ValidAddrStart) && (Address < ValidAddrEnd)) { FLASH->CTLR |= CR_PAGE_PG; *(__IO uint32_t *)(Address) = Data0; FLASH->CTLR |= CR_BUF_LOAD; while(FLASH->STATR & SR_BSY) ; FLASH->CTLR &= ~CR_PAGE_PG; } } void RAM_FLASH_ProgramPage_Fast (uint32_t Page_Address) { if((Page_Address >= ValidAddrStart) && (Page_Address < ValidAddrEnd)) { FLASH->CTLR |= CR_PAGE_PG; FLASH->ADDR = Page_Address; FLASH->CTLR |= CR_STRT_Set; while(FLASH->STATR & SR_BSY) ; FLASH->CTLR &= ~CR_PAGE_PG; } } void RAM_FLASH_Lock_Fast (void) { FLASH->CTLR |= CR_LOCK_Set; } Может быть стоит добавить задержку перед первой проверкой флага в while? Помню с PIC18 был прикол с UART, что там флаги статуса не сразу менялись и приходилось вставлять nop перед первым опросом флага. Может быть здесь такая же проблема?...