void F()

Участник-

Постов

27 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о void F()

-

Звание

Участник

Контакты

-

Сайт

Array

-

ICQ

Array

-

Спасибо за советы. Простите, что не описал ситуацию относительно соблюдения правил помехоустойчивости. Я имел в виду минимальные требования к ПП, чтобы та заработала, пускай даже без устойчивости к шерстяным кофтам. (это и будет функционирующий макет) Да, действительно похоже. Насчет верхнего предела частоты (133MHz) - это лабораторный идеал, склоняюсь к 66 при тактовой 133. Соглашусь с Corvus, shf_05, правильный дизайн платы лежит за пределами 2 слоев. Но: Действительно, у ПЛИС-оводах в экспериментальных проектах нарушен не один стандарт проектировки ВЧ платы, однако, результат удовлетворяет требования задуманного. Вот если бы не эти три разъема (их больше двух), вопросов у меня бы не было. Неужели 6 см этого чуда все испортят? EvilWrecker, то, что вы написали не добавляет никакой информации. В чем странность этой "халтуры"? Это то Т-образное присоединение ПЛИС? Я исключил все "извивания" дорожек или этого не стоило делать? Полагаясь на принцип "прямее и проще" при расположении компонентов и прокладки шин, я не улучшаю ВЧ характеристики?

-

Спасибо за ответы, agregat и Old_horse. Хорошо, т.е. на каждую плату по резисторам. А будут ли влиять на амплитуду сигнала остальные компоненты (всего: 7 включений в шину) ? Впрочем, они же в состоянии HI-Z. Ах да. Топология других плат намного проще: прямые линии, проходящие от разъемов сразу до компонента (2-3 см). Для питания я оставил место, чтобы развести его хорошей звездой. Интересует ситуация относительно обратных сигналов. Это должны быть земляные проводники, проходящие под линиями передачи? А если я все свободное место на заполню "землей", то обеспечит ли это достаточное место для обратных? (со шлейфа идет две линии для "обратных сигналов"). К сожалению, многослойки сейчас обходятся очень дорого, потому я разбил многослойку на несколько... А шлейф - 6 см, с шагом 0.5.

-

Разводка шин с параллельными подключениями

void F() опубликовал тема в Работаем с трассировкой

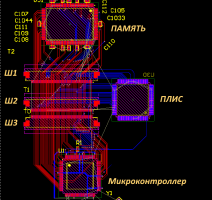

Добрый день, уважаемые. Прошу вашей помощи в непростой задаче. Дана ПП двухслойная с шиной, где частота передачи варьируется от 66-133MHz. Я завершил лишь часть разводки: Дело в том, что эти проводники подходят и к CPLD, и к SSRAM, и к коннекторам, которые подключат другие три платы короткими шлейфами. Я постарался избегать прямых углов и переходных отверстий, но последних получается 2-4 на линию. По расчетам длина линии не должна превышать 112мм иначе возникнут серьезные отражения (1/20 длины волны). Вот путь управляющего сигнала типа WE/OE. Показан наихудший случай. Тактовый сигнал я пропустил аккуратно без отверстий. Но возможно это бессмысленно, тк. частота каждой линии может быть ~ тактовой. Собственно вопросы следующие: 1) Можно ли обойтись без терминирующих резисторов на концах (крайне сложно реализовать)? Длина проводников близка к максимальной 112мм (для 133MHz). 2) Поможет ли хоть как-нибудь последовательное согласование рядом с микроконтроллером? 3) Необходимо ли устанавливать буферы на остальных платах, к которым эта ПП будет подсоединена шлейфами? 4) Заработает ли что-нибудь работать на текущий момент разработки? :) PS: PDF с разводкой имеется...PCB1_01.pdf PSS: Распишу подробнее, если необходимо. -

Всем большое спасибо. Теперь знаю в каком направлении двигаться.

-

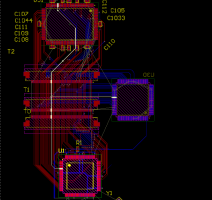

У меня возникают вопросы не того уровня, в котором находится тема. Взгляните на картинку: Я попытался разбить плату на части, чтобы упростить разводку. Однако в этом ужасе я даже не знаю с чего начать. :( Неверное с размещения компонентов? В таком случае каким правилом мне руководствоваться? Как действуют при разводке большого числа компонентов знающие люди? Микросхема, от которой идет шина, находится слева наверху; мне ее ставить поближе к краю платы?..

-

-

Ох, крайне дорого выходит четырехслойная плата >10x10cm для моих целей. Средняя цена превышает 120$. :( А на плате 10x10 выходит так: Помещается только половина крупных компонентов. Хм...

-

Спасибо. Буду разбираться.

-

Источник (master) - устройство в левом верхнем углу, остальные - подчиненные в шине S-Bus.

-

Интерфейс синхронный типа SRAM: шина данных 16бит, шина адреса 24, сигналы чтения/записи/выборки, тактовый сигнал (не дифф.пара). Описанный интерфейс является основным, соединяющим 5 устройств в шине. Есть еще один синхронный, связывающий две FPGA через FIFO. Остальные линии не критичны. PS: А что насчет использования шлейфа? На более высоком уровне схемотехники смотрится не так страшно: :)

-

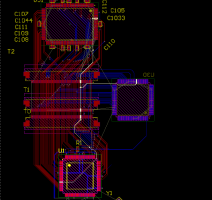

Схемотехник говорит, разводи как хочешь. Собственно, это сейчас он и пишет :-) Я делал подобное в Sprint-Layout-е, но разбивал на модули: получалось что-то такое: *img* Я не сколько за надежность переживаю, сколько за помехи в шинах. Но, что ж... Если без 4 слоев никак - будем делать четыре слоя :-) Не подскажите компанию, которая берет на заказ 4-слоя ПП в мелкой серии (< 10 шт)? PS: Возможно ли использовать короткий шлейф для соединения труднодоступных шин? Я имею ввиду плоский тонкий шлейф, подобный тем, которые в смартфонах используют.

-

Ах, да. Додумался ;-) Шина должна идти по одной стороне, а на второй уже сами подключения.

-

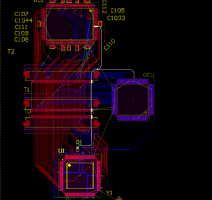

Фух. Думал о четырех, но китайцы (по крайней мере Itead Studio) не берут на изготовление четырехслойных плат больше 10x10см, а микросхемы - в этом случае - стоят впритык друг к другу. Кстати, если четырехслойная плата, то два слоя уходят полностью под сигнальные линии? Я честно представить не могу как параллельно подвести 20 линий к четырем микросхемам...

-

Разбиение сложной платы на несколько небольших

void F() опубликовал тема в Altium Designer, DXP, Protel

Добрый день, уважаемые. С Altium-ом не так давно работаю, но перешел на него из-за повышения сложности дизайна проектов. Имеется неразведенная ПП с большим количеством соединений и компонентов. В основном компоненты связаны параллельными шинами (~16-32 линий): от одного компонента идет шина, подключенная к 4-5 ПЛИС/SRAM и т.п; или же у некоторых микросхем имеются связи друг с другом похожими шинами. Мне стало страшно на это смотреть. :( Возможно стоит разделить плату на 2-3 планки, соединив их вертикально с помощью коннекторов с колодками (этакий бутерброд получается)? Как это лучше сделать в Altium-e? Еще вопрос: как вообще выполняются параллельные соединения 4-5 компонентов к одной шине на ПП? В случае с двухслойной платой можно подключить без проблем к шине только 2 компонента (сверху и снизу), я так понимаю. Заранее спасибо! PS: Частоты передачи по линиям ~66MHz, исключая тактовые. -

Спасибо за развернутый ответ. :) Если не ошибаюсь, то подходит формула: l(длина волны) = c(ск.света)/f(частота линии) И если длина проводника превышает 1/20 волны, то возникнут искажения. Я, в принципе, на это и надеялся, но кроме эффекта отражения могут возникнуть и другие ВЧ гадости. Кстати, правильное ли решение: вырезка полигонов, которые не могут иметь прямого соединения с землей (см. черные области) ?