enzaime

Участник-

Постов

83 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о enzaime

-

Звание

Частый гость

Посетители профиля

1 194 просмотра профиля

-

тактовый сигнал LVCMOS

enzaime ответил enzaime тема в от ТТЛ до LVDS здесь

Всё понял, спасибо -

тактовый сигнал LVCMOS

enzaime ответил enzaime тема в от ТТЛ до LVDS здесь

Спасибо за разъяснения. Всё с этим понятно, внимания не обратил. Обожаю этот форум и на вопрос ответят, и культурно унизить не забудут -

тактовый сигнал LVCMOS

enzaime ответил enzaime тема в от ТТЛ до LVDS здесь

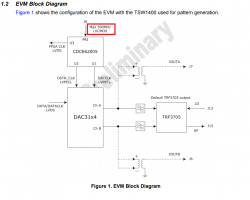

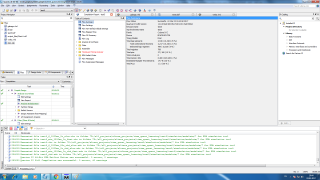

А что тогда имеется ввиду вот здесь? Это функциональная диаграмма платы из руководства пользователя И в том же документе ниже Или имеется ввиду что максимум можно 500 МГц, но его вы нигде не возьмёте? И вообще с этими отладочными платами хрень какая-то, все их делают так что нужно подавать внешний тактовый сигнал, хотя какая сложность использовать микросхему умножения входной частоты с кристалла на плате? И гибкость (мол задал другой коэффициент и получил нужную частоту), и запары для пользователя меньше, подал питание, внешний модуль ещё какой-нить подключил и радуйся. Но это так, я просто ною -

тактовый сигнал LVCMOS

enzaime опубликовал тема в от ТТЛ до LVDS здесь

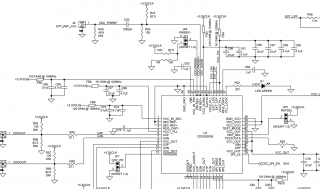

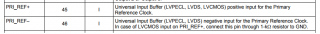

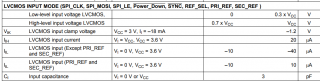

Хочу приобрести отладочную плату DAC3154EVM. Для работы платы требуется тактовый сигнал с характеристиками 1.5 Vrms LVCMOS 500 MHz. Я так понимаю, что это характеристики синусоиды с амплитудой 2.1в, частотой 500 МГц. Этот сигнал идёт на микросхему тактового генератора CDCE62005 Вот участок схемы Этот сигнал идёт с входа EXT_REF_CLK на вывод pri ref+ Вот описание выводов Вот их электрические характеристики Я не могу понять какие характеристики должен иметь входной сигнал, по току и напряжению, также какое смещение и можно ли такой сигнал подать с генератора сигналов с выходом 50 Ом? -

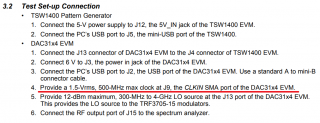

Подобрал плату DAC3162evm Это демонстрационная плата, для микросхемы DAC3162. Внутри этой микросхемы 2 ЦАПа, управляемых дифференциальной 12 битной шиной (LVDS) поочерёдно на частоте 500 Мгц. Т.е. ЦАПы работают на частоте 250 МГц. Сама плата спроектирована так, что для её работы нужна ПЛИС и внешнее тактирование. Производитель для работы с этой платой рекомендует плату TSW3100evm Это плата генерации цифрового сигнала с плис Stratix II EP2S60F1020C4N и DDR памятью. Стоит она 4500 - 5500 $, видел на ebay за 500 $, но б/у и неизвестно в каком состоянии и по какой причине продаётся с такой большой разницей в цене, возможно придёт нерабочий хлам. У меня есть отладочная плата DE0-nano с ПЛИС Cyclone IV ep4ce22f17c6n. Судя по техническому описанию эта ПЛИС может подойти, но я не уверен, что правильно всё понял. В таблице на странице 1-23 (таблица 1-24) пишут, что ПЛИС может работать на частоте 500 МГц, внутренняя память может работать на частоте 315 МГц стр 1-26 (таблица 1-27), LVDS передатчик может работать на частоте 640 МГц стр. 1-31 (таблица 1-34). Также непонятно с тактированием платы DAC3162EVM в инструкции по эксплуатации есть схема на стр.2 Там пишут, что внешний тактовый сигнал должен быть односторонним с 0.5 Vrms (это напряжение или показатель качества входно сигнала, тоже непонятно) и/или (это я тоже не понял) с максимальной частотой 500 МГц (LVPEC, ac-coupled) (с этим тоже непонятно). На самой демонстрационной плате 1 вход для тактирования, выполненный в sma, который идёт к микросхеме CDCP1803 - это тактовый буфер с программируемым делителем, от него идёт сигнал к цапу и внешней ПЛИС. Я видел, что продаются микросхемы получения тактового сигнала от кристалла, но с какими характеристиками она должна быть я не понимаю. Может кто-то подскажет подходящую микросхему или демонстрационную плату для примера или по каким характеристикам искать микросхему. Всё что я понял что выходной сигнал должен быть 500 МГц, но уровень напряжения и какие-то другие характеристики мне непонятны. Там я уже смог бы подобрать какую-нибудь аналогичную

-

Во!!! Всё как надо разъяснили, я аж всё понял, чего да как) Всем спасибо)

-

Сам знаю, что я виноват, но вот потихоньку разбираюсь) Я вспомнил, второй вид симуляции в quartus называется modelsim gate-level simulation. Это уже симуляция почти как на устройстве? И туда надо как-то подключать sdc файл? И будет ли эта симуляция показывать отличные результаты от RTL симуляции, если sdc файл написан неверно (неправильно заданы констрейны) сейчас к сожалению нет возможности это проверить(

-

Давайте) Конечно же без всяких там sdf файлов, только RTL) Я видел, что в меню симуляции в квартусе есть 2 вида: RTL и ещё какая-то (щас посмотреть не могу). Я запускал их обе, но каких-то явных различий не заметил. А sdf файл никакой я не писал и не подключал. Как-то так

-

А есть книги про то как использовать Time Quest (Altera), т.е. как правильно задавать временные ограничения с примерами. Читал Time quest для чайников, но я не всё там нашёл, что хотел. Также читал TimeQuest Quick start tutorial, опять же как-то там на мой взгляд примеров мало. В общем может кто посоветовать книги где бы было бы много примеров как простых, так и сложных. И вообще кто как осваивал временной анализ (написание временных ограничений) для ПЛИС?

-

А предсказуемо, значит так как в симуляции? Или предсказуемо означает с учётом большого опыта? Как новичку понять что будет работать, а что нет? И можно ли как-то просимулировать констрейны? В vhdl, например, есть оператор latency, нужно как-то с ним писать код, чтобы учитывать временные ограничения? Да действительно что-то там было про клок, но я особо внимания не обратил) Вот если бы за каждый варнинг било бы током, я бы начал суетиться и подозревать что что-то не так) В целом понимаю, что с температурой что-то там меняется. В общем из того, что мне написали я понял, что в симуляции виден идеальный вариант работы, т.е. как будто бы я задал правильно все констрейны Что надо как-то там ограничивать допустимыми задержками входные и выходные сигналы, задавать параметры тактового сигнала. И вот тогда всё будет как надо. Чего так сложно-то??? :(

-

Да я ПЛИС не обвиняю) Знаю, что сам виноват) Да и где просить совета как не в сообществе у людей, которые шарят? Насчёт for: почему нельзя применять, если это синтезируемая конструкция языка? (как ,например, использование типа real - несинтезируемой конструкции, используемого для симуляции ) И чего это тогда без циклов писать? Писать что-то вроде машины состояний? Это же с ума сойти можно и вообще крыша поехать может А как же тогда быть, если, например, пишешь прошивку, а ПЛИС под рукой нет, как тогда отлаживать? Я и не настаивал, на просмотре проекта) Констрейнить значит задавать временные ограничения? Нет, не задаю( А почему они не учитываются как-то там автоматически? Я ведь задаю, что частота 200 МГц (в модуле pll), да и в процессе разводки мне никаких ошибок не выдаёт. По типу: так мол и так для такой частоты проект развести не удаётся. Да и косвенно я указал ограничение, задав частоту 200 МГц, т.е. я хочу чтобы в каждом процессе по восходящему фронту операции выполнялись не менее, чем за 5 нс, а тут ещё какие-то констрейны прописывать надо? Моя не понимат( Насчёт второго: да фиг знает, это функция из библиотеки ieee.std_logic_misc.all; на форуме stackoverflow http://stackoverflow.com/questions/2897338...rray-of-vectors тут чувак, наверно умный, чёт объясняет про неё Да я интуитивно понимаю что такое может быть, если операция не успевает выполняться за отведенное время, поэтому уменьшение частоты скорее всего устранит проблему. Нет щас возможности проверить( Но почему мне среда не бросает в лицо никаких ошибок? По типу: так мол 200 МГц слишком много для реализации такой логики. А наоборот всё компилирует и файл прошивки создаётся и типа заливай и всё будет ок, а на деле шляпа какая-то выходит(

-

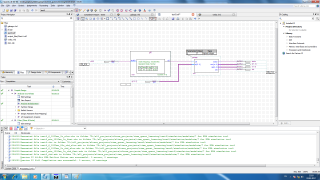

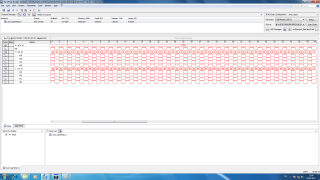

В общем штука такая в процессе изучения ПЛИС заметил вот какую вещь: по мере уменьшения емкости чипа (total logic elements) начинаются всякие странные вещи. Например, там где должна быть 1 там 0 и наоборот. Я сделал тестовый проект, в котором виден этот эффект. Использую плату CoreEP4CE10 c ПЛИС EP4CE10F17C8 и тактовым генератором на 50 МГц Реализуется следующее: n параллельных процессов в которых m раз выполняется * и / проц 1: *,/ проц 2: *,/ *,/ проц 3: *,/ *,/ *,/ *,/ проц 4: *,/ *,/ *,/ *,/ *,/ проц 5: *,/ *,/ *,/ *,/ *,/ *,/ и т.д. каждая ветка описывается так: library IEEE; use IEEE.STD_LOGIC_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; use ieee.std_logic_misc.all; entity vetka is generic(n:natural:= 10); port( clk : in STD_LOGIC; a: in std_logic_vector(15 downto 0); r:out std_logic; chisl:out std_logic ); end vetka; --}} End of automatically maintained section architecture arch of vetka is function vetv (a: std_logic_vector) return std_logic_vector is variable c: std_logic_vector(29 downto 0); begin c := x"000"&"00"&a; for i in 1 to n loop c := conv_std_logic_vector(conv_integer©*conv_integer©,30); c := conv_std_logic_vector(conv_integer©/conv_integer(c(7 downto 0)),30); end loop; return c; end; function merg (d: std_logic_vector) return std_logic is variable c: std_logic:='0'; begin for i in 0 to 29 loop c := c or d(i); end loop; return c; end; signal d:std_logic_vector(29 downto 0):=x"0000000"&"00"; signal st:std_logic_vector(3 downto 0):=x"0"; begin r <= or_reduce(d); chisl <= merg(d); process(clk) begin if(rising_edge(clk)) then if(st = x"0") then d <= vetv(a); st <= x"1"; end if; if(st = x"1") then st <= x"0"; d <= conv_std_logic_vector(0,30); end if; end if; end process; -- enter your statements here -- end arch; функция or-reduce(d) регистрирует изменение сигнала d, изменяя своё значение на противоположное при каждом изменении сигнала d. далее генерируются n процессов длины m library IEEE; use IEEE.STD_LOGIC_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity gabage is generic(m:natural:=5); port( clk : in STD_LOGIC; etalon: out std_logic; a: in std_logic_vector(15 downto 0); vetv : out STD_LOGIC_vector(m downto 0); rez: out std_logic_vector(m downto 0); alls: out std_logic ); end gabage; --}} End of automatically maintained section architecture arch of gabage is signal etst:std_logic_vector(3 downto 0):=x"0"; signal et:std_logic:='0'; signal vrez:std_logic_vector(m downto 0); component vetka is generic(n:natural:= 10); port( clk : in STD_LOGIC; a: in std_logic_vector(15 downto 0); r:out std_logic; chisl:out std_logic ); end component; function merg (d: std_logic_vector) return std_logic is variable c: std_logic:='0'; begin c := d(0); for i in 1 to m loop c := c and d(i); end loop; return c; end; begin vetv <= vrez; etalon <= et; alls <= merg(vrez); G0: for i in 0 to m generate k1:vetka generic map(n => i) port map( clk => clk, a => a, r => vrez(i), chisl => rez(i) ); end generate; process(clk) begin if(rising_edge(clk)) then if(etst = x"0") then et <= '1'; etst <= x"1"; end if; if(etst = x"1") then et <= '0'; etst <= x"0"; end if; end if; end process; -- enter your statements here -- end arch; В общем сначала я думал увидеть задержку выполнения операций для каждого процесса, сравнивая r и etalon увидеть какое-то отставание на каждой ветви от эталона (etalon). Сигнал alls объединение сигналов готовности через функцию логическое И Да и главный файл: Выходная частота pll 200 МГц входная 50 МГц Вот так это дело работает в симуляторе modelsim (gate level), например, для 8 веток Смотрел работу в чипе с помощью логического анализатора, работающего на частоте 200 МГц (частота выходных сигналов 100 МГц) Если генерировать для 4 ветвей, то всё работает как надо ( правда каких-то задержек я не увидел, возможно, неправильно смотрел) отчёт компилятора Вот что отображает логический анализатор Но если сгенерировать для 8 ветвей, то что-то непонятное происходит картинка сильно отличается от того, что в симуляторе. Сигналы готовности n должны быть равномерными с частотой 100 МГЦ, но по факту бывает так что высокий уровень несколько тактов не сменяется низким, хотя в коде нигде такого не прописано отчёт компилятора Я как-то не понимаю почему это происходит. Тоесть понятно что я что-то делаю не так, но вот что именно не понимаю Может кто сталкивался с чем-то подобным? Вот ссылка с проектом на яндекс диске https://yadi.sk/d/FEwjHm0G3EwbyD

-

ДПФ на ПЛИС

enzaime ответил enzaime тема в Работаем с ПЛИС, области применения, выбор

Предполагается что в сигнале будет от 1 частоты до 7-8. Эти частоты нужны для того чтобы определять из каких сигналов состоит исходный. Ну точность к примеру +- 200 КГц. Т.е. ответ может быть такой 5МГц +- 200 КГц. Вот как-то так. -

ДПФ на ПЛИС

enzaime ответил enzaime тема в Работаем с ПЛИС, области применения, выбор

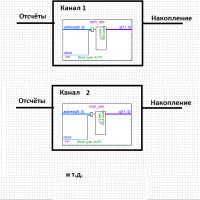

В общем набросал я схемку вот здесь видно что можно сделать несколько блоков rom памяти с таблицей синусов, а дальше чтобы получить нужный коэффициент надо просто выбрать его из таблицы. И для каждого канала хранить такую таблицу (например 100 каналов и 100 одинаковых таблиц, чтобы за 1 такт можно было получать больше 2 значений, а если бы все каналы обращались бы к 1 таблице, то действительно за 1 такт я бы больше 2 значений из памяти не получил бы). Это то что мне первое в голову пришло. Дальше да можно уменьшить количество хранимых значений таблицы (используя свойства функций sin, cos) Но может есть ещё какие варианты? Помимо тех что выше описаны? Мне просто интересно какой вариант самый правильный ( я понимаю, что есть много вариантов, вот какой будет реализован такой и будет правильным) -

ДПФ на ПЛИС

enzaime ответил enzaime тема в Работаем с ПЛИС, области применения, выбор

Задача: определить частоту сигнала в диапазоне 0 до 100 МГц за время <10 мкс (в идеале, но пока что хоть за какое-нибудь время) ДПФ это я сам так взял. ПЛИС 5csema5f31c6 (Cyclone V). Насчёт определения частоты я так понял есть 2 основных алгоритма: в лоб (ДПФ) и оптимизированное (БПФ и все его разновидности (по онованию 2,4, алгоритм Винограда и т.д.)) ДПФ потому что нет ограничения что-то вроде на количество выборок сигнала (Например для БПФ по основанию 2 можно рассчитать накопления на частотах в количестве 2,4,8,16,32 ... и отсчётов должно быть столько же, а в ДПФ можно взять для примера 321 частоту и 1567 отсчётов для каждой частоты. Как-то так) Внутри ПЛИС вроде достаточно ресурсов (именно блоков памяти), чтобы организовать 100 компонентов rom размером 1024х12 слов (т.е. будет 100 компонентов rom со своими входами и выходами (100 входов тактовых, 100 входов адрес чтения, 100 выходов значения памяти по адресу). Но да в логике 100 входов адресов и 100 выходов значений по адресам займут наверно много.