lyatte

Участник-

Постов

17 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о lyatte

-

Звание

Участник

- День рождения 14.01.1989

Контакты

-

Сайт

Array

-

ICQ

Array

Посетители профиля

2 345 просмотров профиля

-

Так в логе написано ведь следующее: А так же на сайте указано какие версии нужны. Можно использовать версию modelsim от Intel, которую они распространяли для Quartus 19 (modelsim Intel fpga starter edition 2019.2).

-

Для генерации библиотек нужна версия Mentor Graphics ModelSim SE/DE/PE (2019.2)

-

При настройке IP-Core (Altera On-Chip Memory) у вас должна быть таблица с адресами и типом памяти (UFM, CFM). Надо просто в ней в Access mode для CFM поставить write and read и тогда она должна быть доступна для записи и чтения. (Железа с MAX10 нету чтобы проверить как это будет работать).

-

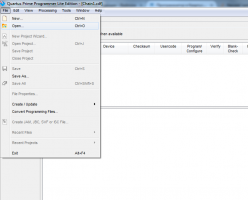

Программатор в Квартусе

lyatte ответил _sda тема в Среды разработки - обсуждаем САПРы

В Quartus 16.0 точно можно загрузить *.cdf фаил. (Если запускать приложение программатора отдельно от quartus, если из самого quartus то такой пункт меню отсутсвует). -

В своем проекте использую преобразование 8b/10b и синхронизацию осуществляю по K28.5 символу. Проверялось в железе. Стабильно принимало и синхронизация никуда не уплывала. Какие частоты заводите на порты rx_std_coreclkin, tx_std_coreclkin и на какой частоте передаёте данные и смотрите принимаемые?

-

В данном тестовом проекте Quartus расположил входную частоту на PLL на pin AB27. Для тактирования паралельной шины данных передаваемых с трансивера я использую выходную частоту с IP ядра (порт tx_std_clkout). Для принятых данных по аналогии используется частота rx_std_clkout. (данное решение было подсмотрено в reference desing examples. На выходе Pll настроены 2 частоты: Большая для передатчика, у меня равна 312.5 Мгц, из моего понимания - передатчик передаёт данные по двум фронтам, тем самым происходит умножение частоты и в итоге 625 Mbit поток данных. Меньшая частота используется как опорная для CDR, завожу ее на порт rx_cdr_refclk. Она настраивается на частоту которая настроена в IP ядре Native-Phy, в части RX (62.5 МГц).

-

Настройки нормальные. По моему проекту: у нас используется внешняя частота с тактового генератора. Она заводится на клоковый вход, чтобы была возможность нормально использовать Fraction PLL. Саму PLL настраиваем на необходимые нам частоты (у меня Datarate 625Mbit, один выход с PLL 312.5Mhz, другой 62.5Mhz). И оба используем для тактирования native-phy. В Native-phy выставлено необходимое количество каналов сразу. Всего у меня 3 трансивера. По сигналам: На вход ext_pll_clk - заводим частоту с внешней PLL. На вход rx_cdr_refclk - заводим частоту тоже с внешней PLL. Входная частота заведена в плату (REFCLK), но не используется. Быстро создал проект с минимумом IP ядер (разных блоков, не подключал сигналы которые на расположение не влияют, контакты в Pin Planner не задавал), чтобы проверить точно ли он расположит всё (чип 5CSXFC6D6F31C7). Всё нормально располагает. Верхний уровень проекта. Настройка PLL. (Настройка FPLL_CTRL - по умолчанию что предлагается в IP ядре). Настройка Native-Phy. Результат в Chip Planner.

-

Какое IP ядро вы используете (Native-Phy или Custom-Phy)? В своем проекте на 5CGX использовали все трансиверы с IP ядром Native-Phy и внешней PLL для tx. Всё заработало.

-

Можно формировать на выходе PLL одну частоту и выводить её на клоковые пины (PLL_CLKOUTp, Quartus автоматически добавит 2ю частоту на 2ю ножку пары). Необходимо только задать правильный стандарт I/O в настройках (проверялось в Q9 со стандартом Differential SSTL Class 1). Сдвиг фазы будет как раз 180 градусов, если же формировать 2 разные частоты и выводить их на пины то возможно нужно будет подбирать сдвиг фазы чтобы получить в итоге идеальные 180, и не факт что получится подобрать.

-

А вы могли бы выложить что у вас в настройках проекта в пункте Device -> Device and Pin Options -> Configuration. На сколько я помню можно на прямую задать в этом разделе микросхему для конфигурирования и Quartus на этапе создания *.sof файла сразу и создаст *.pof файл. Правда такое было в Quartus 9.1, а после не было необходимости использовать Passive Parallel и Statix II.

-

Какой режим конфигурации у вас выбран и какой на реально выбран на плате? От него зависит те микросхемы для прошивки вы можете выбирать, выберите свой вариант (Passive serial, Fast Passive Parallel или другой). Тогда должны появиться. У меня набор микросхем для выбора как раз зависит от режима конфигурации.

-

В Quartus 13 есть EPCE16, попробуйте сгенерировать для нее и прошить. Поиск выдаёт что EPCE16 и EPC16 одно и тоже.

-

Подключить внешнюю память можно. Вам нужен будет SDRAM контроллер (CY7C1380 SDRAM ведь?). А далее с его помощью оперируете с необходимым объёмом памяти. Ограничение физическое, в вашей ПЛИС всего 36 блоков M4K (165888 бит) - можно выделить около 20КБ только.

-

Нельзя просто так взять и использовать "<=" вне блока always. Почитайте про виды присвоений в verilog. assign ena = ~ shift[2] & shift[1];

-

Modelsim VHDL

lyatte ответил dima_spb тема в Языки проектирования на ПЛИС (FPGA)

В modelsim компилировать можно и через пунк меня Compile -> Compile.