-

Постов

180 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Crowbar

-

Звание

Частый гость

Контакты

-

Сайт

Array

-

ICQ

Array

Посетители профиля

2 505 просмотров профиля

-

DxDesigner шины и Flat drc-121

Crowbar опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Добрый день! В настройках DRC включены опции drc-121: Internal Checks, Flat Cheks. Версия DxDesigner EE7.9.4. Для обычных связей DRC работает без ошибок при использовании Internal и Flat групп LINK. Проблема при использовании шин BUS: как правильно задать связь между двумя одинаковыми шинами на разных листах (LINK из Flat группы не работает, вылезает ошибка "Missing internal connection symbols on net"), чтобы DRC не ругался при Flat проверках ? -

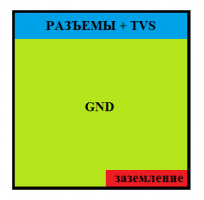

TVS'ы защищают аналоговые входы. Выбраны с малыми токами утечки. Стоят они в основном для защиты от статики (пиковая мощность 230W, 5А в пике при открытии).

-

При условии обязательной привязки потенциала защитного заземления к земле платы вне прибора (например в источнике питания). Таким образом, делать отдельные слои , компланарные GND с набегающей емкостью, для прохождения токов срабатывания защитных элементов нет смысла

-

Согласен, это самое верное решение, но в силу конструктивных особенностей неприменимо.

-

Расположение заземляющего полигона на ПП

Crowbar опубликовал тема в Электробезопасность и ЭМС

Подскажите пожалуйста, как правильно поступить. В текущем варианте ПП есть два внутренних свободных слоя, заключенных между слоями локальной земли платы (назовем ее GND). GND распределена по всей площади и места по периметру платы под ободок корпусной земли (назовем ее CHASSIS) нет. С одной стороны ПП расположены разъемы, на линях которых установлены TVS диоды. С другой стороны платы точка подключения внешнего заземления. Вопрос по подключению TVS, как лучше: 1) Подключить TVS непосредственно к GND, а свободные два слоя исключить из стека ПП/залить дополнительно полигоном GND. 2) Подключить TVS к двум внутренним слоям, которые отвести под CHASSIS. CHASSIS расположить по всей площади ПП и подключить к точке внешнего заземления (там же, где и GND заведено на заземление) -

ПЛИС на плате нет. AN-1729 я смотрел, раздел про rate adjustment вопросов не вызывает: все согласно функционалу и регистрам, описанным в основном datasheet'е. А вот раздел про phase Alignment вызывает вопросы. Так например, описанный алгоритм если посмотреть внимательно двигает не фазу CLK_OUT а сам PTP Clock т.е. получается не CLK_OUT двигается к нужным значениям счетчика, а сам счетчик к CLK_OUT. Поэтому если на стороне мастера мы привяжем счетчик к источнику точного времени, то описанный алгоритм никоим образом сам CLK_OUT к нужным отсчетам (PPS например) источника точного времени не подвинет, более того, он еще и сами PTP часы сместит, что скажется на всех ведомых устройствах в сети. Еще раз повторюсь: пока я вижу, что механизм step adjustment работает только со счетчиком (что самое интересное datasheet на DP83640 тоже только про этот функционал говорит). Я пробовал на плате делать step adjust на значения до 200нс - CLK_OUT при этом не сдвигался.

-

Дело в том, что готового формирователя PPS импульсов в DP83640 нет, есть более интересный механизм: триггеры, по которым относительно PTP Clock (счетчик) можно различные импульсы генерировать (в том числе и PPS) c дискретностью в 8ns. Как раз запасной вариант у меня частоту с триггера и выводить, а далее ее через ФАПЧ умножить и почистить. Пока хочется разобраться как разработчики данной мс смогли двигать фазу CLK_OUT относительно счетчика и добились результатов, приведенных на стр.8 в AN-1730 DP83640 Synchronous Ethernet Mode: Achieving Sub-Nanosecond Accuracy in PTP Applications, а также как на видео, начиная с 3:30: http://www.youtube.com/watch?v=6vyr7dFU_O4

-

Начали работать с физикой DP83640, которая помимо встроенного механизма синхронизации часов согласно IEEE1588 PTP имеет возможность синтезировать частоту CLK_OUT. Помимо того, что CLK_OUT с помощью механизма rate adjustment следует частоте PTP ядра (счетчик, они же часы PTP Clock), заявлено, что CLK_OUT можно сфазировать относительно PTP часов. С первого взгляда документация на этот чип богатая, но при полном прочтении возникает больше вопросов чем понимания. В частности пока не понятно как устроен механизм фазировки CLK_OUT относительно локальных часов. Может кто работал с этой физикой и реализовывал механизм подстройки CLK_OUT по фазе относительно PTP часов и подскажет, правильны ли следующие утверждения: 1) Прямого механизма двигать CLK_OUT по фазе нет, и единственная возможность приблизить фронт CLK_OUT к нужным значениям счетчика PTP Clock это "двигать" сам счетчик с использованием механизма step adjustment (сомнительный подход, но другого пока не видно) 2) Точность фазирования будет +-8ns так как счетчик работает на частоте 125 МГц, а step adjustment это просто увеличение/уменьшение значения счетчика на заданную величину 3) Механизм step adjustment не влияет на фазу CLK_OUT при любых значениях задаваемого шага

-

Коллеги, спасибо за отклики. Вакансия закрыта.

-

Для применения в геофизике (МТ, АМТ), виброакустике (авиастроение) на данном этапе _basile, да, манов и здравого смысла хватает, чтобы покрыть большинство задач, и даже библиотечный подход не в счет, требование сугубо для того, чтобы сузить диапазон требуемых архитектур. По поводу ПО: есть наработки в этих IDE. TCP/IP серверы разные бывают, опять же поверхностно пример TELNET сервера для STM32f2 за несколько дней превращается в базовый сервер с машиной состояний, вопрос скорее в другой плоскости: на сколько хорошо человек понимает инструмент который применяет (в данном случае lwip).

-

Система работает с заменяемыми модулями ввода аналоговых или цифровых данных (многоканально). Например, для работы с вибродатчиками, микрофонами, магнитными и электрическими датчиками и т.д.

-

Войковская

-

Исправлено

-

Требуется программист встраиваемых систем в новый проект

Crowbar опубликовал тема в Предлагаю работу

Требуется программист встраиваемых систем для работы в небольшом коллективе инженеров над задачами построения специализированных систем сбора данных. Чтобы не вводить в заблуждение: проект переводится на формальные рельсы с работой в офисе, систему предполагается довести до рабочего образца за год. Основные требования: 1. Знание архитектуры ARM 2. Работа в IAR на языке С (возможны варианты использования других IDE) 3. Опыт использования и наличие завершенных проектов на базе STM32F2, STM32F4, приветствуются микроконтроллеры последних серий LPC 4. Опыт работы с интерфейсами I2C, UART, SPI, USB, SDIO, Ethernet (MII/RMII) 5. Опыт применения TCP/IP стеков (lwip), файловых систем (FAT32), приветствуется опыт применения ОС реального времени (FreeRTOS) 6. Опыт разработки ПО под Windows (QT C++, VS C#, LabVIEW) 7. Знания в области аналого-цифровой схемотехники 8. Базовые знания в области ЦОС 9. Системный поход к программированию (использование систем контроля версий, умение читать и править чужой код, модульное программирование) 10. Технический английский (уверенное чтение документации, статей, переписка с зарубежными партнерами) Опыт и/или стремление к обучению в перспективе: Xilinx Kintex, Artix; Xilinx Zynq-7000 (соответственно Cortex-A9 c Linux и работа с ПЛИС продукции Xilinx в среде ISE или Vivado) Условия труда: Москва, полный рабочий день в офисе, з/п от 50 000 р. оговаривается по результатам собеседования Контакты: goldcrowbar (Sобака) l i s t . r u -

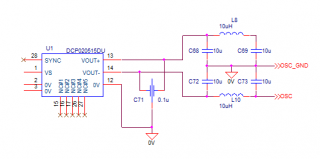

Фильтрация помех DC-DC

Crowbar ответил Crowbar тема в Силовая Преобразовательная Техника