en-valb

Участник-

Постов

91 -

Зарегистрирован

-

Посещение

-

Тактирование PTP на RTL8211FSI-VS

en-valb опубликовал тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Всем доброго дня! Есть задача подключить к процессору физик ethernet на RTL8211FSI-VS есть требование о наличии PTP. У RTL8211FSI-VS имеется вход PTP_CLKIN. На него хочу подать от генератора 125 МГц, но в регистре PTP_CLK_CFG RTL8211FSI-VS есть 6:5 биты с помощью которых можно выбрать частоту подаваемую на вход PTP_CLKIN: 10 МГц, 25 МГц и 125 МГц. Предполагаю, что частоты 10 МГц и 25 МГц используются когда период синхронизации на столько велик, что счетчик PTP переполнился бы при частоте 125 МГц. Требований к точности синхронизации нет. Самое простое решение это поставить генератор на одну частоту, но на какую? Или может быть поставить перестраиваемый генератор? Весь интернет обшарил в поисках информации, о PTP, но в основном попадается информация в части программного обеспечения, какой нибудь reference design пусть да же на другой физик найти не смог. Третья неделя как пошла, а окончательного решения принять по этому вопросу ни как не могу. Еще нужно раздать этот сигнал на 2 физика, может кто подскажет тактовые буфферы доступные сейчас к покупке, китайские какие нибудь. -

Заработало! В инструкции Gowin_EMPU_M1 Download Reference Design есть ссылка на архив с разными проектами там есть в папке solution проект DK_START_GW1N9_V1.1 с контроллером flash памяти. В проекте DK_START_GW1N9_V1.1 есть файл userflash_controller.v необходимо этот файл включить в проект вместо IP Gowin Flash Controller. Почему то в IP Core Generator Gowin Flash Controller не поддерживает режим отображения памяти. Хотя в описании ядра написано "...and AHB Bus interface is to connect AHB Bus in MCU with AHB Bus, as an instruction memory or data storage for MCU...". Ссылка на проект.

-

Всем доброго дня! Плата Tang Nano 9k c FPGA GW1NR-LV9QN88PC6/I5 ревизия C. Поднимаю SoC Cortex-M1. Пытаюсь запустить программу из User Flash. Для этого в настройках ядра Cortex-M1 вкладка Memory в разделе ITCM Select устанавливаю External Instruction Memory. В keil соответственно прописываю для: IROM1 - Start 0x00000000, Size 0x10000, IRAM1 - Start 0x20000000, Size 0x8000. Компилирую HW и SW в настройках Gowin Programmer указываю MCU Mode L и добавляю файлы *.fs и *.bin сохраняю. Все в соответствии с инструкцией Gowin_EMPU_M1 Download Reference Design на странице 15(17) глава 5 Embedded UserFlash Download. Прошиваю ПЛИС, аппаратная часть запускается (видно по 4-м светодиодам которые подтянуты pull up), но программа не стартует. Флеш память подключаю через IP блок Gowin Flash Controller в настройках указываю шину AHB. Тут я интуитивно принял решение так как сигналы которые выпускает Cortex-M1 на внешнюю флешь соответствуют сигналам шины AHB. Возможно я здесь что то не правильно сделал. В инструкции ни чего по этому поводу не нашел. В Gowin_EMPU_M1 Download Reference Design в разделе 5.3 Design Flow, в пункте 3 сказано "Instantiate UserFlash Controller (GW1N-9C/GW1NR-9C FLASH608K) Memory Map as the instruction memory of Gowin_EMPU_M1." Этот пункт я закрыл как писал выше Gowin Flash Controller-ом. Ссылка на проект. `resetall module Gowin_EMPU_M1_template ( LED, TDI, TMS, TCK, TDO, UART1RXD, UART1TXD, HCLK, //System Clock hwRstn //System Reset ); input HCLK; // System clock input hwRstn; // System reset //UART0 input UART1RXD; output UART1TXD; //JTAG inout TDI; inout TMS; inout TCK; inout TDO; //LED output [3:0] LED; wire MCLK; //mcu clock Gowin_rPLL u_Gowin_rPLL ( .clkout(MCLK), //output clkout 40MHz .clkin(HCLK) //input clkin 50MHz ); wire [31:0] EXTFLASH_HRDATA; wire EXTFLASH_HREADY; wire [1:0] EXTFLASH_HRESP; wire [1:0] EXTFLASH_HTRANS; wire [2:0] EXTFLASH_HSIZE; wire EXTFLASH_HWRITE; wire [31:0] EXTFLASH_HADDR; wire [31:0] EXTFLASH_HWDATA; wire EXTFLASH_HSEL; wire EXTFLASH_HCLK; Gowin_EMPU_M1_Top your_instance_name( .LOCKUP(), //output LOCKUP .HALTED(), //output HALTED .GPIOIN(16'h0000), //input [15:0] GPIOIN .GPIOOUT(LED), //output [15:0] GPIOOUT .GPIOOUTEN(), //output [15:0] GPIOOUTEN .JTAG_3(), //inout JTAG_3 .JTAG_4(), //inout JTAG_4 .JTAG_5(TDI), //inout JTAG_5 .JTAG_6(), //inout JTAG_6 .JTAG_7(TMS), //inout JTAG_7 .JTAG_8(), //inout JTAG_8 .JTAG_9(TCK), //inout JTAG_9 .JTAG_10(), //inout JTAG_10 .JTAG_11(), //inout JTAG_11 .JTAG_12(), //inout JTAG_12 .JTAG_13(TDO), //inout JTAG_13 .JTAG_14(), //inout JTAG_14 .JTAG_15(), //inout JTAG_15 .JTAG_16(), //inout JTAG_16 .JTAG_17(), //inout JTAG_17 .JTAG_18(), //inout JTAG_18 .UART0RXD(1'b0), //input UART0RXD .UART0TXD(), //output UART0TXD .UART1RXD(UART1RXD), //input UART1RXD .UART1TXD(UART1TXD), //output UART1TXD .TIMER0EXTIN(1'b0), //input TIMER0EXTIN .TIMER1EXTIN(1'b0), //input TIMER1EXTIN .EXTFLASH0HRDATA(EXTFLASH_HRDATA), //input [31:0] EXTFLASH0HRDATA .EXTFLASH0HREADYOUT(EXTFLASH_HREADY), //input EXTFLASH0HREADYOUT .EXTFLASH0HRESP(EXTFLASH_HRESP), //input [1:0] EXTFLASH0HRESP .EXTFLASH0HTRANS(EXTFLASH_HTRANS), //output [1:0] EXTFLASH0HTRANS .EXTFLASH0HBURST(), //output [2:0] EXTFLASH0HBURST .EXTFLASH0HPROT(), //output [3:0] EXTFLASH0HPROT .EXTFLASH0HSIZE(EXTFLASH_HSIZE), //output [2:0] EXTFLASH0HSIZE .EXTFLASH0HWRITE(EXTFLASH_HWRITE), //output EXTFLASH0HWRITE .EXTFLASH0HREADYMUX(), //output EXTFLASH0HREADYMUX .EXTFLASH0HMASTER(), //output [3:0] EXTFLASH0HMASTER .EXTFLASH0HMASTLOCK(), //output EXTFLASH0HMASTLOCK .EXTFLASH0HADDR(EXTFLASH_HADDR), //output [31:0] EXTFLASH0HADDR .EXTFLASH0HWDATA(EXTFLASH_HWDATA), //output [31:0] EXTFLASH0HWDATA .EXTFLASH0HSEL(EXTFLASH_HSEL), //output EXTFLASH0HSEL .EXTFLASH0HCLK(EXTFLASH_HCLK), //output EXTFLASH0HCLK .EXTFLASH0HRESET(EXTFLASH_HRESETn), //output EXTFLASH0HRESET .HCLK(MCLK), //input HCLK .hwRstn(hwRstn) //input hwRstn ); Gowin_Flash_Controller_Top program_flash_memory ( .AHB_HRDATA(EXTFLASH_HRDATA), //output [31:0] AHB_HRDATA .AHB_HREADY(EXTFLASH_HREADY), //output AHB_HREADY .AHB_HRESP(EXTFLASH_HRESP), //output [1:0] AHB_HRESP .AHB_HTRANS(EXTFLASH_HTRANS), //input [1:0] AHB_HTRANS .AHB_HSIZE(EXTFLASH_HSIZE), //input [2:0] AHB_HSIZE .AHB_HWRITE(EXTFLASH_HWRITE), //input AHB_HWRITE .AHB_HADDR(EXTFLASH_HADDR), //input [31:0] AHB_HADDR .AHB_HWDATA(EXTFLASH_HWDATA), //input [31:0] AHB_HWDATA .AHB_HSEL(EXTFLASH_HSEL), //input AHB_HSEL .AHB_HCLK(EXTFLASH_HCLK), //input AHB_HCLK .AHB_HRESETn(EXTFLASH_HRESETn) //input AHB_HRESETn ); endmodule Что я мог здесь пропустить? BSRAM в качестве ITCM в соответствии с главой 2 инструкции Gowin_EMPU_M1 Download Reference Design у меня все заработало.

-

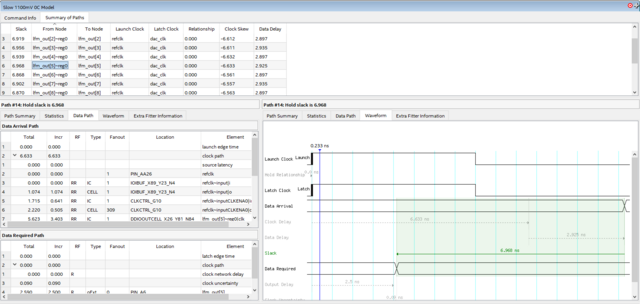

Вот теперь правильный и hold и setup!!! Значения перепутал, в min и max. В min вбил значение максимальной задержки, а в max значение минимальной задержки. #************************************************************** # Set Output Delay #************************************************************** # максимальная задержка клока до ПЛИС (задержка от источника тактовой частоты до плис по печатным проводникам через разъем HSMC) set CLK_bs_delay_max 0.1 # максимальная задержка данных от ПЛИС до ЦАП (задержка данных от портов плис по печатным проводникам через разъем HSMC до ЦАП) set DATA_delay_max 0.1 # минимальная задержка клока до ЦАП (задержка от источника тактовой частоты через мультиплексор 0.7 ns + буфер дифпары минимальная задержка 0.9 ns) #set CLK_bd_delay_min 3.45 set CLK_bd_delay_min 1.7 #(tSU ЦАП по справочнику) set tSU 1.0 set tmax [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] #set tmax [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max] # минимальная задержка клока до ПЛИС (задержка от источника тактовой частоты до плис по печатным проводникам через разъем HSMC) set CLK_bs_delay_min 0.1 # минимальная задержка данных от ПЛИС до ЦАП (задержка данных от портов плис по печатным проводникам через разъем HSMC до ЦАП) set DATA_delay_min 0.1 # максимальная задержка клока до ЦАП (задержка от источника тактовой частоты через мультиплексор 0.7 ns + буфер дифпары минимальная задержка 2.5 ns) #set CLK_bd_delay_max 5.55 set CLK_bd_delay_max 3.3 #(tH ЦАП по справочнику) set tH 1.0 set tmin [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] #set tmin [expr $CLK_bs_delay_min - $tH + $DATA_delay_min] Теперь похоже на правду). des00, благодарю за помощь от всей души!!!

-

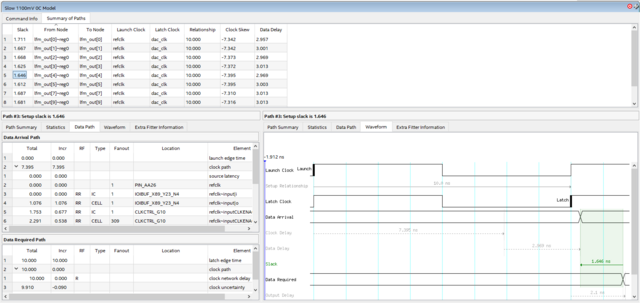

Добавил задержку CLK по плате на ЦАП, Time Quest ругаться перестал. #************************************************************** # Set Output Delay #************************************************************** # максимальная задержка клока до ПЛИС (задержка от источника тактовой частоты до плис по печатным проводникам через разъем HSMC) set CLK_bs_delay_max 0.1 # максимальная задержка данных от ПЛИС до ЦАП (задержка данных от портов плис по печатным проводникам через разъем HSMC до ЦАП) set DATA_delay_max 0.1 # минимальная задержка клока до ЦАП (задержка от источника тактовой частоты через мультиплексор 0.7 ns + буфер дифпары минимальная задержка 0.9 ns) #set CLK_bd_delay_min 3.45 set CLK_bd_delay_min 3.3 #(tSU ЦАП по справочнику) set tSU 1.0 set tmax [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] #set tmax [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max] # минимальная задержка клока до ПЛИС (задержка от источника тактовой частоты до плис по печатным проводникам через разъем HSMC) set CLK_bs_delay_min 0.1 # минимальная задержка данных от ПЛИС до ЦАП (задержка данных от портов плис по печатным проводникам через разъем HSMC до ЦАП) set DATA_delay_min 0.1 # максимальная задержка клока до ЦАП (задержка от источника тактовой частоты через мультиплексор 0.7 ns + буфер дифпары минимальная задержка 2.5 ns) #set CLK_bd_delay_max 5.55 set CLK_bd_delay_max 1.7 #(tH ЦАП по справочнику) set tH 1.0 set tmin [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] #set tmin [expr $CLK_bs_delay_min - $tH + $DATA_delay_min] Но теперь по холду подозрительно огромный запас получился. Я видимо с CLK_bd_delay_min и CLK_bd_delay_max перестарался, хотя вроде как по даташиту.

-

На счет задержки по плате, у AD/DA Data Conversion Card между CLK_IN_P куда я генератор подключил и ЦАП стоит две микросхемы, мультиплексор и буфер. На мультиплексор по даташит propagation delay 0.7 ns, а на буфер от 0.9 ns до 2.5 ns дополнительно какая то задержка по плате, пусть 0.1 ns. В сторону ПЛИС тактовая идет напрямую через разъем на выводы AA26, AB27. Соответственно в формулу я должен включить суммарную задержку CLK_bd_delay_min = 0.7+0.9+0.1 и CLK_bd_delay_max = 0.7+2.5+0.1. Я правильно понимаю? Стало значительно лучше! #************************************************************** # Set Output Delay #************************************************************** # максимальная задержка клока до ПЛИС (задержка от источника тактовой частоты до плис по печатным проводникам через разъем HSMC) set CLK_bs_delay_max 0.1 # максимальная задержка данных от ПЛИС до ЦАП (задержка данных от портов плис по печатным проводникам через разъем HSMC до ЦАП) set DATA_delay_max 0.1 # минимальная задержка клока до ЦАП (задержка от источника тактовой частоты через мультиплексор 0.7 ns + буфер дифпары минимальная задержка 0.9 ns) #set CLK_bd_delay_min 3.45 set CLK_bd_delay_min 3.3 #(tSU ЦАП по справочнику) set tSU 1.0 #set tmax [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] set tmax [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max] # минимальная задержка клока до ПЛИС (задержка от источника тактовой частоты до плис по печатным проводникам через разъем HSMC) set CLK_bs_delay_min 0.1 # минимальная задержка данных от ПЛИС до ЦАП (задержка данных от портов плис по печатным проводникам через разъем HSMC до ЦАП) set DATA_delay_min 0.1 # максимальная задержка клока до ЦАП (задержка от источника тактовой частоты через мультиплексор 0.7 ns + буфер дифпары минимальная задержка 2.5 ns) #set CLK_bd_delay_max 5.55 set CLK_bd_delay_max 1.7 #(tH ЦАП по справочнику) set tH 1.0 #set tmin [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] set tmin [expr $CLK_bs_delay_min - $tH + $DATA_delay_min] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[0]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[0]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[1]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[1]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[2]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[2]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[3]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[3]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[4]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[4]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[5]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[5]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[6]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[6]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[7]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[7]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[8]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[8]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[9]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[9]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[10]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[10]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[11]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[11]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[12]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[12]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] $tmax [get_ports {lfm_out[13]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] $tmin [get_ports {lfm_out[13]}]

-

А ведь действительно, видимо глянул в даташит ADC по ошибке, на бумажку выписал tsu и th, и больше не сверялся. Внимательности у меня конечно не занимать. Премного благодарен!!! Сейчас все исправлю.

-

Не выходит каменный цветок! Двинул фазу на +90, Time Ques перестал выдавать ошибки, но сигнал на выходе ЦАП испортился.

-

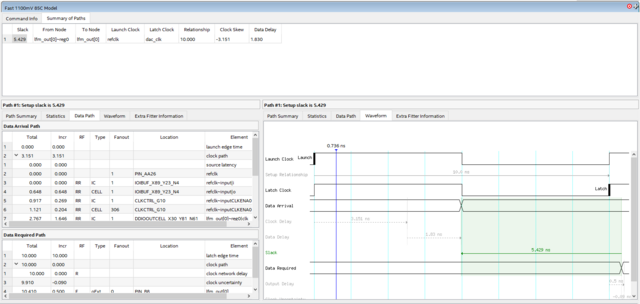

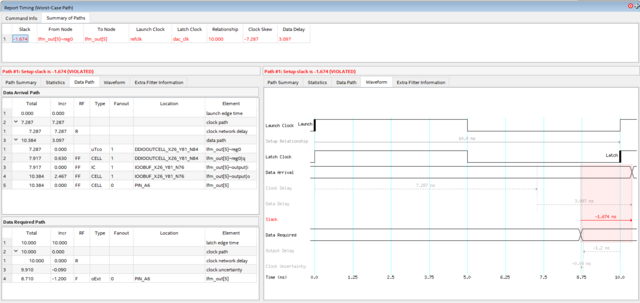

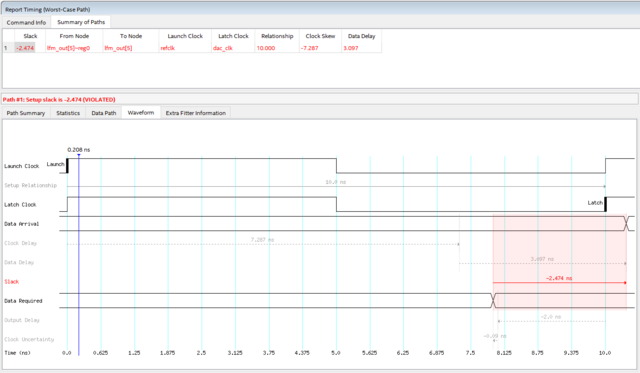

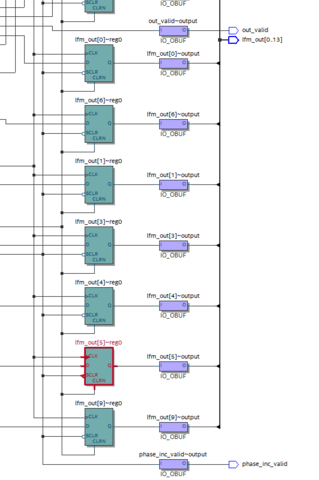

Вот что получилось: Создал виртуальный клок dac_clk #************************************************************** # Create Clock #************************************************************** create_clock -name {refclk} -period 10.000 -waveform { 0.000 5.000 } [get_ports {refclk}] create_clock -name {dac_clk} -period 10.000 -waveform { 0.000 5.000 } Объединил входной клок refclk и виртуальный клок dac_clk в эксклюзивную группу #************************************************************** # Set Clock Groups #************************************************************** set_clock_groups -exclusive -group [get_clocks {dac_clk refclk}] И переписал set_output_delay #************************************************************** # Set Output Delay #************************************************************** # максимальная задержка клока до ПЛИС (задержка от источника тактовой частоты до плис по печатным проводникам через разъем HSMC) set CLK_bs_delay_max 0.2 # максимальная задержка данных от ПЛИС до ЦАП (задержка данных от портов плис по печатным проводникам через разъем HSMC до ЦАП) set DATA_delay_max 0.5 # минимальная задержка клока до ЦАП (задержка от источника тактовой частоты через мультиплексор 0.7 ns + буфер дифпары минимальная задержка 0.9 ns) set CLK_bd_delay_min 1.6 #(tSU ЦАП по справочнику) set tSU 2.9 # минимальная задержка клока до ПЛИС (задержка от источника тактовой частоты до плис по печатным проводникам через разъем HSMC) set CLK_bs_delay_min 0.2 # минимальная задержка данных от ПЛИС до ЦАП (задержка данных от портов плис по печатным проводникам через разъем HSMC до ЦАП) set DATA_delay_min 0.5 # максимальная задержка клока до ЦАП (задержка от источника тактовой частоты через мультиплексор 0.7 ns + буфер дифпары минимальная задержка 2.5 ns) set CLK_bd_delay_max 3.2 #(tH ЦАП по справочнику) set tH 3.8 set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[0]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[0]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[1]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[1]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[2]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[2]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[3]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[3]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[4]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[4]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[5]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[5]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[6]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[6]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[7]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[7]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[8]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[8]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[9]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[9]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[10]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[10]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[11]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[11]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[12]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[12]}] set_output_delay -add_delay -max -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_max + $tSU + $DATA_delay_max - $CLK_bd_delay_min] [get_ports {lfm_out[13]}] set_output_delay -add_delay -min -clock [get_clocks {dac_clk}] [expr $CLK_bs_delay_min - $tH + $DATA_delay_min - $CLK_bd_delay_max] [get_ports {lfm_out[13]}] Теперь на диаграмме вижу, что запускающий клок это refclk, а защелкивающий клок это dac_clk Картина поменялась в лучшую сторону, но все еще не достаточно. Теперь как я понимаю необходимо подключить тактирование внутренней логики к выходу PLL и немного пододвинуть запускающий клок? Вы это имеете ввиду? module ddio( input wire d0, input wire d1, input wire clk, output wire out ); reg r_d0; reg r_d1; always @(posedge clk) begin r_d0 <= d0; r_d1 <= d1; end assign out = clk ? r_d0 : r_d1; endmodule Сейчас у меня вот так Такой вариант хуже? DDIO мне наверное не нужен, мне дифференциальную пару тактового сигнала на ПЛИС завести надо, а на ЦАП идет 14-ти разрядная параллельная шина униполярных сигналов.

-

Source-Synchronus Output

-

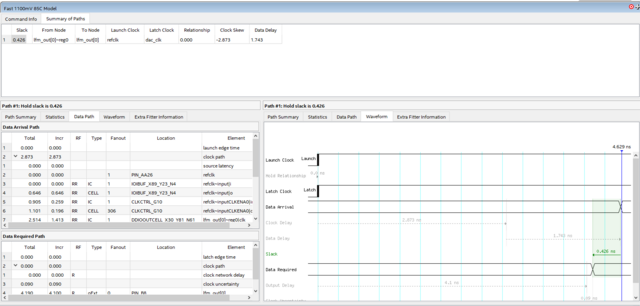

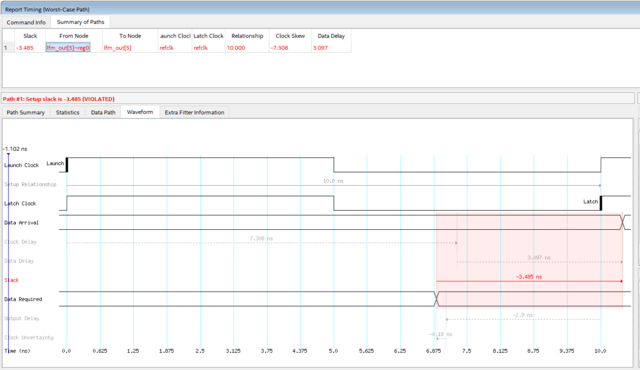

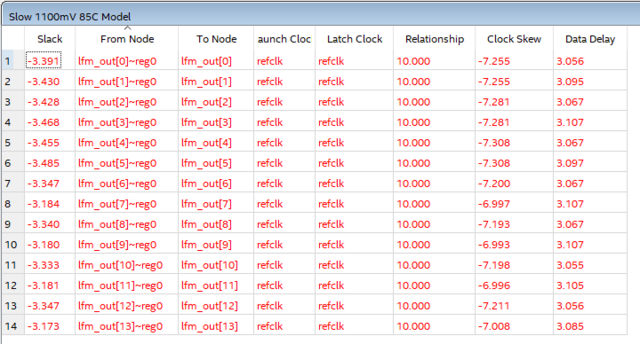

Переключил внутреннюю логику на входную частоту от которой непосредственно ЦАП тактируется, выход PLL сейчас висит не подключенный. Задал констрейны: set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[0]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[0]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[1]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[1]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[2]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[2]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[3]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[3]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[4]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[4]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[5]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[5]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[6]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[6]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[7]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[7]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[8]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[8]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[9]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[9]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[10]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[10]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[11]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[11]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[12]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[12]}] set_output_delay -add_delay -max -clock [get_clocks {refclk}] 2.900 [get_ports {lfm_out[13]}] set_output_delay -add_delay -min -clock [get_clocks {refclk}] 3.800 [get_ports {lfm_out[13]}] Сигнал на осциллографе хороший. На диаграмме выше видно, что запускающий clock задержан на 7.308 ns. Или это можно рассматривать как сдвиг фазы на 7.308 ns? Тогда нужно фазу пододвинуть, с помощью PLL наверное?

-

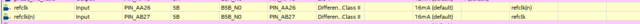

andrew_b, благодарю за помощь, планировал от внешнего 10 МГц все затактировать, но видимо придется 100 МГц генератор покупать. В pin planer для входной частоты сделал I/O Standart дифференциальный вход. Теперь этот вход 100 МГц (раньше был 50 МГц). Подключил его на PLL. У PLL теперь на входе и выходе 100 МГц. Оставил его(PLL) так как далее скорее всего понадобятся другие частоты. sdc файл полностью переделал, во вложении. Остальное пока не трогал. На AD/DA Data Conversion Card допаял перемычку на R111 чтобы вход CLK сделать униполярным и подал на него с генератора 100 МГц. Все картинки на осциллографе хорошие, но пока не заданы констрейны set_output_delay. Буду разбираться как их описать под новую конфигурацию схемы тактирования ЦАП. dds.out.sdc

-

Всем доброго дня! Прошу помочь, не могу разобраться, что делаю не так. Имеется: 1. SoCKit 2. AD/DA Data Conversion Card Генерирую ЛЧМ сигнал с помощью NCO. С помощью TimeQuest в GUI задал констрейны: 1. На входную тактовую частоту 50 МГц поступающую на PLL. 2. create_generated_clock на порождаемый с помощью PLL клок 100 МГц от входного клока 50 МГц 3. На выходную тактовую частоту из ПЛИС для DAC которая является дифференциальной. Для каждого порта dac_clk_p и dac_clk_n отдельный create_generated_clock исходя из соображений, что эти клоки порождаемые от выходной из PLL частоты 100 МГц. а) Правильно ли я тут сделал, исходя из того что assign dac_clk_p = clk_100MHz; assign dac_clk_n = ~clk_100MHz; б) Нужно ли мне объединять в эксклюзивную группу dac_clk_p и dac_clk_n? Как я понял в группу объединяются синхронные клоки здесь как раз такой случай. 4. set_output_delay -min и set_output_delay -max на порты поступающие от ПЛИС на ЦАП относительно dac_clk_p. В соответствии с datasheet на ЦАП для -min задал значение th = 3.8 nS, для -max tsu = 2.9 nS. Проблема в том, что если не задавать констрейны set_output_delay сигнал на выходе ЦАП чистый, но если задать сигнал зашумлен (иголки). Предполагаю, что я не верно задаю set_output_delay и ухудшаю параметры по tsu/th сигналов поступающих на ЦАП. dds.out.sdc dds.out_Set_Output_Delay.sdc

-

Так и понял. Подбираюсь потихоньку к Hyperlinx. На плату пока резисторы 0 Ом по шине данных поставил на всякий случай. Спасибо!

-

Пытаюсь понять на сколько адекватные результаты моделирования.