-

Постов

3 853 -

Зарегистрирован

-

если посмотреть его репозиторий много плюшек можно найти... )))

-

к BSACPLD рекомендую к использованию корки I2C по ссылке

-

привет, у тебя нет переделанного модуля I2C для 7 битной адресации - просто микросхема не поддерживает 10 битную адресацию отбой - разобрался... все работает работает в связке с stm32 логика мастер <=> процессор слейв

-

1200 мне кажется только для сериализатора/десериализатора в MIPI (схема которая превращает паралельные данные в последовательные для передачи по LVDS) а не для всей схемы Если прочитать примечание то частота для данных 1200/8=150 600 тоже довольно высокая частота - проверьте точно необходима?

-

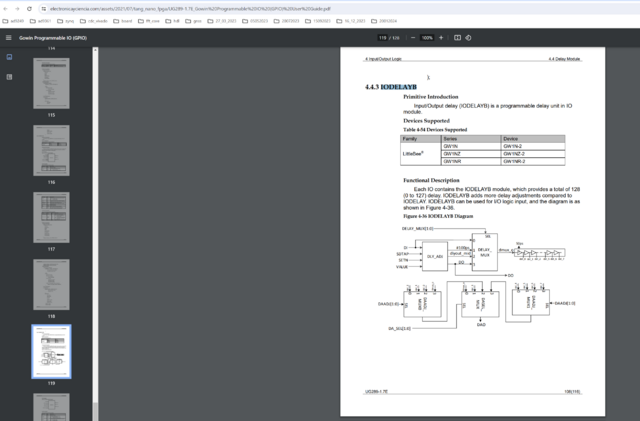

смотрели дизайн-пример https://www.gowinsemi.com/en/support/ip_detail/4/ и https://www.gowinsemi.com/en/support/database/2056/? пусть даже на другой плис... к каждой IP core среда должна генерировать файл констрейнов... во всяком случае у Intel, Xilinx так происходит... сгенерируйте пример и посмотрите что да как PS я с GOWIN не работал...

-

посмотрите

-

применение IP core двухклоковое фифо между SDRAM и логикой - как решение проблеми IP core само пропишет ограничения для CDC в sdc файл

-

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity shift_example is Port ( input_number : in STD_LOGIC_VECTOR (7 downto 0); shift_amount : in INTEGER; result_left : out STD_LOGIC_VECTOR (7 downto 0); result_right : out STD_LOGIC_VECTOR (7 downto 0)); end shift_example; architecture Behavioral of shift_example is begin -- Сдвиг влево для умножения result_left <= input_number sll shift_amount; -- Сдвиг вправо для деления result_right <= input_number srl shift_amount; end Behavioral;

-

-

Вам надо сгенерировать билиотеку для моделирования для IP core и в do файле подключить или запускать симуляцию из под Вашей студии

-

тогда работа с описаниями по ссилкам https://github.com/tirfil/VhdI2CSlave https://github.com/murattcan/FPGA-I2C-Slave можно поискать еще и включить в поиск модули на verilog кроме vhdl - уверен их много, просто я потратил на поиск 2 мин PS возможна дополнительная работа напильником

-

Возьмите плату на stm32 и организуйте обмен для отладки

-

помогите плиз скачать документ

Maverick_ опубликовал тема в Документация

https://ru.scribd.com/document/78090253/Carrier-Recovery-and-Automatic-Gain-Control-on-FPGA-s-based-platform-IEEE-802-15-3c-mm-Wave-PHY-Application -

огромное спасибо за информацию)