mirobest

Участник-

Постов

103 -

Зарегистрирован

-

Посещение

-

Все просто оказалось, забыл закрыть Симуляцию перед просмотром файла....

-

В симуляторе Vivado Custom AXI Master модифицирует содержимое DDR в фиксированной области через ZYNQ S_AXI_HP0_FPD. Пытаюсь сохранить содержимое области DDR в файл , используя команду peek_mem_file ("ddr_mem", 32'h20000000, 8'hFF) , но после остановки симуляции файл "ddr_mem" пуст. Поясните плз.

-

Подскажите как преобразовать AXI4_Lite в AXI4 , если поддержка Birst не требуется. Практически проблема состоит в том как подключить AXI4_Lite Master к S_AXI_HP0_FPD поддержка Burst не требуется

-

Дифф. пара стандарта MIPI D-PHY ( примерно 1,2GHz) проходит через несколько плат и возникает рассогласование между длиной сигналов Pos и Neg . Как правильно его компенсировать при сохранении требуемого значения импеданса дифф. пары,? Проблему рассогласования импеданса на разьемах предлагаю оставить за рамками обсуждения.

-

Вопрос закрыт

-

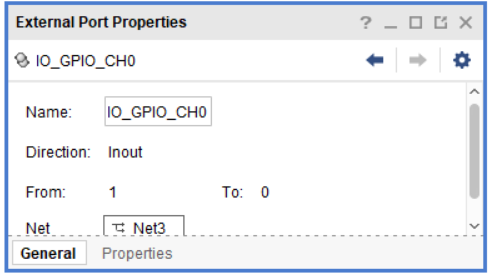

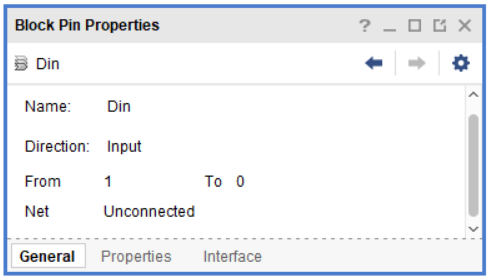

В Testbench мне необходимо приложить периодческий сигнал ( частота) к INOUT порту. Как я понял подключение REG к INOUT порту не разрешено. Как решить вопрос,?

-

Мне необходимо добавить группу сигналов в Wave Window симулятора Vivado используя TCL script. Подскажите плз как указать Симулятору ссылку на мой script?

-

cпасибо

-

-

По поводу MMCM/PLL

mirobest опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Есть два вопроса : 1. Как из произвольной частоты ( к примеру 113,3759 МГц ) сгенерировать удвоенную и деленную на 2 частоты., которые должны быть точно выравнены по фазе с исходной частотой. 2. Где посмотреть report с фактическими ( после implementation) данными по сдвигам фаз? -

посмотрел так и есть. в этой IP и подключусь

-

Или это в wrapper наверное делать нужно ручками.