kskssk

Участник-

Постов

26 -

Зарегистрирован

-

Посещение

Репутация

1 ОбычныйИнформация о kskssk

-

Звание

Участник

- День рождения 03.05.1984

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

1 266 просмотров профиля

-

Мелкие вопросы по Vivado

kskssk ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Если я правильно понял, то вы хотите с помощью атрибутов сохранить элементы, которые синтезатор выкидывает в результате оптимизации. На 99% в вашем коде есть ошибка, из-за которой появляются незадействованные выходы, которые синтезатор пытается убрать. Попытайтесь найти ее, вместо того, что бы прибивать всё гвоздями (т.е атрибутами). Если все же хотите сохранить, то наложите keep(в ise) или dont_touch(vivado) на сигналы входов-выходов памяти. -

Мелкие вопросы по Vivado

kskssk ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Этот атрибут запрещает синтезатору проводить оптимизацию на границах между компонентами. Насколько я понял, вы его хотите применить к набору примитивов. Но их потроха не могут быть оптимизированы, т.к. они - примитивы. В итоге не ясно чего вы хотите добиться использованием атрибута. Поясните. -

Не за что. Вывод printf() ведь перенаправляется либо в MDM, либо в UART, на то чтобы передать его тратится время..

-

1. Может в программе микроблейза перед командой управления gpio что-то еще запускается? Типа printf()? 2. Сброс микроблейза верно управляется? Там вроде бы активный уровень - 0. 3. Если я ничего не путаю 🙂, то в некоторых конфигурациях у микроблейза появляется порт locked, связанный с mmcm. Его проверьте, должен быть = 1.

-

Попробуйте запустить симуляцию на более длительное время - несколько миллисекунд.

-

В контексте DDR ECC вопрос: а кому-нибудь удавалось зарегистрировать ошибки при общении с памятью в ПК? Случаи с явно битой памятью не в счёт) Извиняюсь за оффтоп)

-

Можете ещё с этой темой ознакомиться для расширения кругозора) 1. Минимум 64. Откроете большой имплементироавнный проект, симулятор, редактор, pdf'ки - и 10 Гб уже съедено.. 32 будет впритык. 3. Можете глянуть например https://www.geekbench.com/ 4. См. ссылку на тему по выбору ПК. 6. Моделсим в несколько раз медленнее будет работать (проверено), остальное скорее всего так же замедлится. 8. Вам скорее всего захочется делать несколько запусков имплементации одновременно, память будет съедаться пропорционально. Можно взять пару SSD для повышения надёжности) Вивадо до 8 ядер на один запуск может задействовать, но загрузка ядер не 100%.

-

Vitis 2023.2

kskssk ответил Alex77 тема в Среды разработки - обсуждаем САПРы

Век живи - век учись..) Спасибо за инфу) Но в винде-то трюк не покатит? -

Vitis 2023.2

kskssk ответил Alex77 тема в Среды разработки - обсуждаем САПРы

С iso легче устанавливать - смонтировал образ и вперёд.. Не надо разархивировать и искать под это дополнительное место. Вообще надо бы заморочится на досуге и сравнить побитно содержимое пиратского образа и оригинального архива какими-нибудь Meld'ом) -

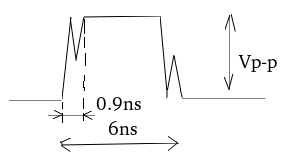

Длительность фронта по даташиту 250 пс, по осциллу 300 пс, частота тактового сигнала ~170 МГц. Высота зубчика - 0.5 Vpp на осциле и 0.3 Vpp в модели.

-

В модели: -kintexu diff_term=true - есть зубья -kintexu diff_term=false + внешний R - нет зубьев -virtex diff_term=true - нет зубьев В железе: -kintexu diff_term=true - есть зубья -kintexu diff_term=false + внешний R - есть зубья Дополнительно в модели попробовал заменить драйвер LVDS на другой, у которого есть регулировка выходного тока LVDS (приемником оставил KintexU) - при минимальном токе есть зубья, при увеличении тока зубья пропадают. В итоге в железе поставил между половинками дифпары C=4pf. Фронты подзавалились и сгладились. Извиняюсь за долгий ответ) Проворонил)

-

Проблема с LVDS DIFF_TERM на KUltrascale

kskssk опубликовал тема в Среды разработки - обсуждаем САПРы

Привет! Проблема с приемом LVDS на KUltrascale: вижу картину как на приложенном рисунке на осциллографе с помощью дифференциального пробника (полоса > 3 ГГц, емкость < 1 pf) на переходных отверстиях рядом (~1 мм) с шарами BGA ПЛИС, которая является приемником. Мне не нравятся зубчики по краям импульса (это тактовый сигнал). Удивительно, что при этом проект работает нормально в широком диапазоне температур. (Может зубчики отфильтровываются на внутренних потрохах ПЛИС?) Эл. стандарт передатчика - LVDS (Vcm = 700 мВ, Vpp = 500 мВ - все в рамках требований ПЛИС согласно даташиту и осциллографу). В проекте на ПЛИС для данных контактов выбран стандарт LVDS, включен согласующий регистр в констреинтах (DIFF_TERM_ADV = TERM_100), использован IBUFDS. Сначала было подумал, что проблема с волновым сопротивление проводников, однако на дифпарах, идущих не на ПЛИС, такой проблемы нет, все дифпары имеют одинаковую "геометрию". Попробовал смоделировать приемник и передатчик с помощью их IBIS моделей в Microcap (для ПЛИС использовал модель KUltrascale LVDS с DIFF_TERM) и к своему удивлению увидел очень похожую на осциллограф картину, только зубчики в модели поменьше - где-то 0.3 от Vpp. Откровенно говоря, за верность модели ручаться не могу, однако ее импульс по характеру очень похож на реальный. Попробовал заменить модель ПЛИСовских LVDS-приемников на "Virtex6 c DIFF_TERM" - получил импульс с нормальными фронтами, без зазубрин. Затем заменил модель ПЛИСовских LVDS-приемников на "KUltrascale без DIFF_TERM", поставил перед ними R = 100 Ом и получил импульс с нормальными фронтами, без зазубрин. После этого в констреинтах отключил согласующий резистор (DIFF_TERM_ADV = TERM_NONE), на осцилле увидел увеличение Vpp раза в 1.5, зубчики остались. Затем прицепил к плате снаружи резистор 100 Ом - осциллограмма стала примерно как и была с DIFF_TERM_ADV = TERM_100, только Vpp изменилось на 20-50 мВ не помню в какую сторону). От безысходности попробовал установить EQUALIZATION = EQ_LEVEL1 - на осцилле изменений ожидаемо нет. Все это наводит на мысль, что я что-то не понимаю в KUltrascale)..🤯 Может кто-то подскажет, как избавиться от зубчиков? Извиняюсь за корявый рисунок и отсутствие скринов, прошу понять и простить 🙂 Поправьте, если ошибся с веткой форума. -

Какая там память сейчас не припомню. Запускал одну имплементацию на 8ми потоках и там и там. Про set_param general.maxThreads знаю. Добавлю ещё, что на старом компе win7, а на новом win10. Может она не даёт процу вздохнуть полной грудью. Заметил, что в семёрке моё самописное джава-приложение работает быстрее, чем в 10ке) В приложении интенсивный обмен с плиской по Ethernet, расчёт БПФ, построение графиков.., интуитивно кажется, что Ethernet там медленнее.

-

Было 80 минут - стало 70.

-

Наконец машина собрана) В сравнении с i7-4790k (4 GHz) имплементация + синтез одного проекта быстрее на 10 минут (Было 80 минут - стало 70.)