-

Постов

21 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Sanchez_

-

Звание

Участник

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

877 просмотров профиля

-

Постоянно. На сколько силовой, в вольтах и амперах? Напишите, пожалуйста, подробнее о проекте на почту [email protected]

-

Быстро и качественно выполню работы по проектированию печатных плат любой сложности. Резюме: https://ekaterinburg.hh.ru/resume/cd3fe8a9ff018567000039ed1f306343356537

-

Пример топологии DDR3

Sanchez_ ответил HardJoker тема в Работаем с трассировкой

Спасибо! У меня f=400MHz (DDR3-800). 533 не потяенет проц. Потом покажу, что получилось и расскажу как работает. -

Пример топологии DDR3

Sanchez_ ответил HardJoker тема в Работаем с трассировкой

Добрый вечер! С книжкой знаком, как и с Кечиевым, бывал на его лекциях. Дело в том, что эту линию нельзя считать прям короткой. Период клока 2,5нс. Сколько фронт? ну пусть 20%, это 0,5нс. По расчетам того же Кечиева при фронтах в 0,5нс граница между короткой и длинной линии - 38мм. Так что как минимум это на грани. Если считать по задержке (7пс/мм), то 500пс = 70мм, т.е. время фронта соизмеримо с длинной линии. Поэтому я и подумал, что не должна быть безразлична как топология так и положение согласующих элементов. Во всех апноутах, которые мне попались, была описана топология флай-бай с терминацией в конце шины. Насколько я понял, у Вас есть информация, как можно делать иначе, (апноуты). Поделитесь, пожалуста. Содной стороны, логично поставить согласующие элементы вначале линии, и я склоняюсь к этому. Довести до средней точки, а там разделить на 2 стороны и соединить с каждой стороны по 2 чипа последовательно. Но я видел пример топологии, где они около точки деления. Есть ли в этом смысл? Есть еще у кого какие-нибудь соображения? -

Пример топологии DDR3

Sanchez_ ответил HardJoker тема в Работаем с трассировкой

Спасибо, Zurabob! за подробные ответы. Чипы друг над другом разместить не получится, т.к. одна сторона занята. Но и так (примерно как на девборде) нормально получается, т.к. не только от средней точки, но вобще вся цепь получается короче 5см. Осталась еще пара вопросов. А какая топология у клока: дифпара SCKA до резисторов и кондера и DSCK после (если смотреть по схеме в PDF)? Вроде как по рисунку и фото она идет к нижнему чипу. И как вообще ее правильно развести? Если вести ее последовательно по чипам, получается 11мм до резисторов и 46мм после на все чипы. Где должны быть резисторы и кондер, как можно ближе к источнику (процу) или около точки деления (если надо тоже делить)? -

Пример топологии DDR3

Sanchez_ ответил HardJoker тема в Работаем с трассировкой

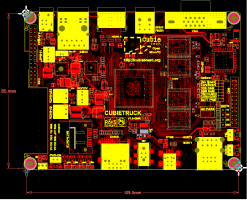

Друзья, помогите разобраться с топологией DDR3! Есть такой замечательный девборд, Cubietruck называется. Во вложении схема на него. В конце схемы есть чертеж платы и фотографии. Разработчик взял за основу проекта этот девборд, схему памяти скопировал 1 в 1 (лист 4), за искючением того, что у нас чипы памяти 4-Гиговые. Самого проекта платы кубитрака нету, есть только вот такая картинка: А теперь, внимание, вопросы. 1. Какая топология DDR3 применена на девборде? 2. Почему нет терминации на шине адреса и команд? 3. Почему это все работает? 4. Что делать мне? нужно, чтоб все заработало без лишних танцев с бубнами: а) добавить терминацию в схему и делать как положено по топологии флай-бай? б) пытаться повторить дизайн девборда, не меняя схему, у них же работает? 5. Может быть у Самсунга какие-то особенные чипы, которые работают без терминации? В даташите на память не нашел никаких упоминаний и требований по топологии и терминации. Так же как и вообще у Самсунга не нашел каких-либо апноутов по DDR3. 6. Может это такой проц замечательный у Аллвинера, который работает с любой разводкой и ему плевать на терминацию? В даташите на него, кроме того, что он поддерживает DDR3 ничего по этому поводу не сказано. Буду крайне признателен за любые дельные советы! A20_Cubietruck_HW_V10_130606.pdf -

Тема закрыта. Глубоко уважаемая фирма Терраэлектроника любезно согласилась принять товар обратно и вернуть денежные средства в полном объеме, за исключением затрат на пересылку. :a14:

-

Продается SABRE Lite – недорогая отладочная платформа на базе четырехядерного ARM Cortex-A9 микропроцессора Freescale I.MX 6 Quad, с тактовой частотой 1 ГГц, 1 МБ L2 кэш-памяти и поддержкой 64-битной памяти DDR3 или двухканальной 32-битной LPDDR2. Интегрированные FlexCAN, шина MLB, PCI Express и SATA-2 обеспечивают превосходные коммуникационные возможности, а благодаря встроенным интерфейсам LVDS, MIPI Display port, MIPI Camera port и HDMI v1.4 делают плату SABRE Lite идеальной платформой для высокотехнологичных решений, автомобильных и индустриальных мультимедийных приложений. Куплена в Терре: http://www.terraelectronica.ru/catalog_info.php?CODE=1089214 Состояние товара: распаковано, включено, проверено, что не подходит для нашей разработки, запаковано обратно. Т.е. платы экслуатировались пару дней. В наличии 2 комплекта. Продаем по 7000р./шт. Товар находится в г. Миасс Челябинской обл. Пересылка по РФ почтой Россиии или транспортной компанией, доставка за Ваш счет. Рассмотрим варианты обмена 1 SABRE Lite на 2 Banana Pi. Для тех, кто не может написать в личку: [email protected]

-

Быстро и качественно выполню работы по проектированию печатных плат любой сложности. Выполню КД на печатные узлы. Возможно изготовление опытных образцов.

-

Инженер-конструктор (проектирование ПП в Altium Designer)

Sanchez_ опубликовал тема в Ищу работу

Резюме здесь: http://hh.ru/resume/cd3fe8a9ff018567000039ed1f306343356537 Там же координаты для связи и примеры работ в портфолио. -

Поддерживаю. Выдам полную КД на прибор, если надо, то и с корпусом, + поддержка внедрения на производстве за 100 т.р. + расходы на изготовление прототипа ПП и комплектующие. Есть наработки в этом направлении. Если заинтересовало, пишите в личку, отправлю резюме.

-

Вот молодцы! :( В даташите одно пишут, а тут нате: "игнорируйте даташит, там не правильно"! Писателю даташита "петак"! :angry2:

-

Может и медленный. Земли разделены, иначе нету смысла разделять и соединять, где-то далеко в одной точке. Да мне такая система больше нравится, аналоговая часть варится сама по себе и цифровые линии не пересекают никаких вырезов.

-

Вот, например, в даташите на AD73311L производитель пишет выводы AGND и DGND садить на разные земли, которые должны соединяться в одном месте, а если это место близко к кодеку, то соединить ферритовой бусинкой. Так что к каждому кодеку свой подход и внимательно даташит читать.

-

Вполне может быть. Для диффпар в некоторых документах регламентируется минимальное расстояние между сегментами змейки. Напимер, в AN2582 Hardware and Layout Design Considerations for DDR Memory Interfaces, в таблице 3 указаны минимальные значения 20 mils, как и расстояние до соседних пар. Но это вообще минимум, если есть возможность, нужно больше делать. В данном случае, может еще сказываться большое число поворотов, каждый поворот вносит неоднородность в линию. Тут надо моделировать.