Мур

Свой-

Постов

1 367 -

Зарегистрирован

-

Посещение

-

https://www.geekom.ru/minipc-it11/?yclid=4680899536067756031 скинули цену... Видно из-за ущербного охлаждения народ воздерживается...

-

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

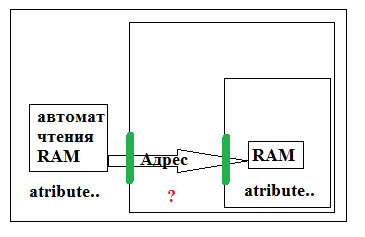

Да! Не будет этого автомата чтения! Это мера вынужденная.... Тут нет ошибки. Замысел прост,-проверить функционирование основной логики при помощи кнопок (покрыть всю вариативность дизайна ) на плате, которых в конечном дизайне уже не будет. Функции кнопок будут выполнять регистры через AXI4. Впереди интрига использования шаблона VITIS Peripheral Tests. Такая заготовка, как я понял, хороша использованием минимального ресурса внутренней памяти. Пока этой теме мало кто уделяет внимание, порождая примеры мастерства для освоения, облегчая быстрое внедрение SoC путем простого распараллеливания задач. Буду благодарен любой информации по этой теме! Все вскользь и не конкретно... Пока не разжился. Но этому стоит выделять время(когда оно появится)! -

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Супер! Вы настоящий друг!... -

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Ух ты!.. Спасибо! Через DONT_TOUCH я как раз автомат чтения (без оптимизации) и привязал к железу! Шина адреса от него только хвост торчит из-за отсутствия памяти.... Интересно, как через ентитай-порты пропустить на два уровня вниз (там где сама память)? Там эти шины тоже пометить как-то надо? Такой разрыв может быть не понят оптимизатором.. -

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Тут все просто. Мне надо оставить память (в симуляции она работает), чтобы в отладке иметь доступ к выходу памяти при помощи ILA . К тому же сам автомат, который читает был из-за этого удален. Я его сумел оставить, но его шина адреса к памяти не доходит (ее нет после имплементации).. Меня задевает другое. Имена памяти как указать? Не нашел такой сложный случай в интернете... -

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Возник вопрос из-за сложностей с атрибутами иерархии keep_hierarchical для примитивов. ..Когда они единичны все норм. А вот параметрическая генерация экземпляров показывет синтаксическую ошибку в индексах. Как это сделать правильно, кто подскажет? Прицепил сам первоначальный исходник для оценки... (там ошибка в очередности имен ADC_RAMs[]. ADC_RAMN[]. ) ......в разделе деклараций пытаюсь описать имена, как рекомендовано в UG625 attribute keep_hierarchy of architecture_name : architecture is {TRUE|FALSE|SOFT}; Пытался по-всякому component RAM64X1D_1 -- примитив generic ( INIT : bit_vector(63 downto 0) := X"0000000000000000"; IS_WCLK_INVERTED : bit := '0' ); port ( DPO : out std_ulogic; SPO : out std_ulogic; A0 : in std_ulogic; A1 : in std_ulogic; A2 : in std_ulogic; A3 : in std_ulogic; A4 : in std_ulogic; A5 : in std_ulogic; D : in std_ulogic; DPRA0 : in std_ulogic; DPRA1 : in std_ulogic; DPRA2 : in std_ulogic; DPRA3 : in std_ulogic; DPRA4 : in std_ulogic; DPRA5 : in std_ulogic; WCLK : in std_ulogic; WE : in std_ulogic ); end component; attribute BOX_TYPE of RAM64X1D_1 : component is "PRIMITIVE"; attribute keep_hierarchy : string; attribute keep_hierarchy of ADC_RAMs[0].ADC_RAMN[ 0].Dual_RAMr: architecture is "TRUE"; attribute keep_hierarchy of ADC_RAMs[0].ADC_RAMN[ 1].Dual_RAMr: architecture is "TRUE"; attribute keep_hierarchy of ADC_RAMs[0].ADC_RAMN[ 2].Dual_RAMr: architecture is "TRUE"; и т.д. .................................... attribute keep_hierarchy of ADC_RAMs[0].ADC_RAMN[31].Dual_RAMr: architecture is "TRUE"; и т.д....................... attribute keep_hierarchy of ADC_RAMs[1].ADC_RAMN[ 0].Dual_RAMr: architecture is "TRUE"; и т.д.................. .....в разделе коммуникаций порождались экземпляры вот таким макаром.. begin ----- ADC_RAMs : for k in 3 downto 0 generate --ADC ADC_RAMN : for n in 31 downto 0 generate Dual_RAMr : RAM64X1D_1 --Здесь хранятся результаты АЦП преобразования port map ( DPO => DRAMs_ADC_B(k)(n), -- Read-only 1-bit data output SPO => open, -- R/W 1-bit data output A0 => addr_radc(0), -- R/W address[0] input bit A1 => addr_radc(1), -- R/W address[1] input bit A2 => addr_radc(2), -- R/W address[2] input bit A3 => addr_radc(3), -- R/W address[3] input bit A4 => addr_radc(4), -- R/W address[4] input bit A5 => addr_radc(5), -- R/W address[5] input bit D => DRAM_ADC_B(k)(n), -- Write 1-bit data input DPRA0 => ADCdatRAM(0), -- Read-only address[0] input bit DPRA1 => ADCdatRAM(1), -- Read-only address[1] input bit DPRA2 => ADCdatRAM(2), -- Read-only address[2] input bit DPRA3 => ADCdatRAM(3), -- Read-only address[3] input bit DPRA4 => ADCdatRAM(4), -- Read-only address[4] input bit DPRA5 => ADCdatRAM(5), -- Read-only address[5] input bit WCLK => sys_clk200MHz, -- Write clock input WE => wr_mem_s -- Write enable input ); end generate ADC_RAMN; end generate ADC_RAMs; Это мне важно для мягкой отладки. Спасибо! Вопрос.vhd -

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Ух, достала же не возможность быстрого поиска в VIVADO нужных сигналов как в симуляторе, так и в схеме!... Чисто глазами и никак иначе! Другое дело для КВА. Нажимаешь первую букву имени и система поочереди подсвечивает все имена с первой выбранной нами буквой. Уверен, что не пропустишь! Экономит время и силы... -

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Я не идеал... Это мой первый опыт общения с подобными SOC системами, если не считать мое 3-х летнее творчество в ISE. Там дружественная среда и дискомфорта не испытывал! Может немного атрибутами более насыщено... Не исключаю и надеюсь, что качественный скачок впереди. И я по достоинству оценю сей инструментарий! Но пока что напрягает... Кстати, в серьезных НИИ времен СССР искали подобных зануд, которые умудрялись находить изъяны в уже отработанном, казалось, материале для рядового состава в войсках! В итоге выявлялись тупиковые сценарии поведения операторов и документация качественно обогащалась. Благодарность шла от обычных работников войны и спасла не одну жизнь! -

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Обращает внимание на нелепость подхода в системе VIVADO , которую я уже на автомате обходил применением дополнительного редактора, чтобы править VHDL код, который прячут пометкой Read-only ,а править необходимо, глядя на итоговые тексты, где теряются мои целые шины и сигналы за порождаемыми оболочками. Уже не обращал внимание на эту особенность! Стоп, думаю, а ведь это фигня! Спасти дизайн руками - последний ход дизайнера! Уже сколько раз так спасался... ...Помнится лет 20 назад возмущались, что теперь ограничивают доступ к привычному редактированию в самом низу сборок. ...И в пределе получили вот такое уродство -уже на уровне исходных кодов запрет... Идиотизм! Верно говорил мой приятель, что 21 век - век ХАЛТУРЫ! ЗЫ. Навигация по тексту с маркерами отсутствует. Только поиск с маркировкой без возможности запомнить важные места ущербно! Вертикальные редакции с ALT сразу по нескольким строкам сразу раздражает... Вот почему спасаюсь в других редакторах! -

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Мои находки при освоении VIVADO Серьёзные проблемы заключительного этапа сборки и отладки.docx Пришла интересная мысль,- уж коль мне привычнее работать в логике,- сделать проект под МикроБлейз и заливать один раз PL без этих финтов и полноценным просмотром на ILA... -

Мелкие вопросы по Vivado

Мур ответил Nick_K тема в Среды разработки - обсуждаем САПРы

Подборка от Гарсия Хавьера https://ohwr.org/project/soc-course/wikis/home Многим будет кстати! ..важный сейчас для меня вопрос, связанный с пуском дизайна PS+PL, где мне необходимо глянуть через ILA сигналы обращения к одному регистру моего IP , чтобы убедится, что примитивная логика работает. Как оказалось, вижу косвенно, что PL работает, а вот от PS тишина (хотя программно я через паузу делаю только запись по этому фиксированному адресу регистра)! Мне не понятно, как убедиться в факте выполнения этой программы на А9? Можно ли записать эту программу через JTAG как на PL ? FSBL я понял, через uCD грузится... Но мне важно видеть временную от ILA, а это на ВИВАДе! Что я тут намудрил ? Дважды грузить (чтобы видеть анализатор) наверное не верно... Спасибо за вектор верного движения и намек на мой косяк!.. -

О... GEEKOM подтянулся! На АМД- таки. И охлаждение улучшен... Информирую..

-

И все же, хоть баталии пошли в сторону оценки HDD\SSD(как буд-то именно это определяет удобство в работе плисовода), вариант Minisforum UM790 PRO подымается скоро до 890, да и концентраторы USB4 подтянутся... Такой сюжет, согласитесь, будоражит и обнадеживает на качественный скачок в творчестве. Так что температура на процессоре будет в форсаже ниже 79 градусов... Пугает только одно,-как бороться с монополией производителей, допускающих иногда брак в своих изделиях и если ты рискнул на эксперимент раньше кульминации мирового кризиса, и на прямую (в целях экономии времени и средств) через Алиекспресс , без посредников (все-таки страховка!), взять этого микро-монстра в расчете на следующие 10 лет? К кому потом обращаться? Кстати, сомнительно, что 4 нм норма будет сохранна 10 лет при диффузионных процессах на 60град........................ Да и у самих тут сервис лукавый... Как говорят мудрецы,- "каждый умирает в одиночку"!

-

Спасибо! Ценю ваше мнение... В моем случае моя CUDA-видяха с выходом на 3 монитора остается за бортом... Грущу...