Брик

Участник-

Постов

26 -

Зарегистрирован

-

Посещение

-

Я вам в лс написала)) Спасибо!

-

Добрый день. Пробую моделировать в Sigrity PowerDC (проект импортирован из MG VX1.2- ODB++). Возникает ошибка при моделировании E/T Co-Simulation : "Error#10: No loop could be generated during voltage drop computation! Please click "Check Errors/Warnings" to check if open circuit exists" Что не нравится? и где можно посмотреть ошибки "Check Errors/Warnings"? Гугл не помог. С user’s guide тоже не сложилось. Камнями только не закидывайте) спасибо!

-

Добрый день! у меня Xpedition Enterprise VX.1.2 x64 и назрел такой такой вопрос, как сгенерировать .mdc? ранее в Expedition 7.9.5EE можно было через Report Writer, возможно есть иной путь, а не через установку VX1.2 х32 Спасибо заранее :rolleyes:

-

Добрый день, подскажите, пожалуйста, как вывести координаты glue spots)

-

Добрый день! Камнями только не закидывайте, пожалуйста. Почему в DDRx Batch-Mode Wizard не доступны пункты Ibis model и т.д? Все модели присвоены, делаю аналогично "HyperLynx® Продвинутый Анализ Высокоскоростных Плат". Спасибо P.S. версии установленного HyperLynx 8.2.1 и 9.0.1

-

Мы не поняли друг друга) Xilinx на Спартан6 оставил одну общую ибис модель (.ibs) на 900 c лишним пина, и кучу .pkg на различные микросхемы данного семейства. Мне из одной общей ибис модели требуется вытащить единственную 6slx45tfgg484. И хз как это сделать. Xilinx предлагает скачать ISE и шаманить там, но пока у меня только танцы с бубнами, а дождя все так и нет :(

-

Добрый день! Снова вопрос, просьба, возможно у кого-нибудь завалялись ibis модели на семейство Spartan6, а именно на модель на 6slx45tfgg484? Такое впечатление будто заблудилась в трех соснах smile3046.gif Cкачала с xilinx и .ibs и .pkg, а как объединить, достать нужную модель мозгов не хватает, или может подскажете, по шагам, как это реализовать (работаю в Hyperlynx)? Помучилась с ISE Xilinx, но пока как-то все грустно (( Заранее всем спасибо за ответы)

-

Нужны IBIS модели ....

Брик ответил opyvovar тема в Цифровые схемы, высокоскоростные ЦС

Добрый день! Снова вопрос, просьба, возможно у кого-нибудь завалялись ibis модели на семейство Spartan6, а именно на модель на 6slx45tfgg484? Такое впечатление будто заблудилась в трех соснах :smile3046: скачала с xilinx и .ibs и .pkg, а как объединить, достать нужную модель мозгов не хватает. Разбираться с редакцией/написанием моделей, ISE/Vivado времени нет, но обязательно займусь, после сдачи проекта! Заранее всем спасибо за ответы) -

Аэйнэнэнэ, Спасибо, все получилось ^_^ У меня вообще русский текст не видно, что-то печатается, но все черно)

-

Добрый день! у меня возник вопрос по Expedition PCB) Есть, например 2 внутренних слоях (пусть будет L5 и L6), где L5 - сигнальный, а L6 - питание, можно ли их поменять местами?)

-

Как разводить на плате BGA 1 мм

Брик ответил 24mi тема в Работаем с трассировкой

agregat, Corvus, ClayMan, всем спасибо за ответы (раньше ответить не получилось, без интернета остались) :laughing: Желательно все же развести на 8 слоях, пока раскидала компоненты по плате, оставив без разводки память (JS28F256P30T95 и DDR3). В пример топологии скачала sp605, как советовал вначале agregat, разбираюсь потихоньку) -

Как разводить на плате BGA 1 мм

Брик ответил 24mi тема в Работаем с трассировкой

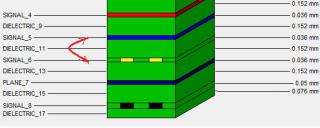

Добрый день! Прошу подсказки/помощи) Получила задание на разводку DDR3 (MT41J256M16RE-15E IT) и FBGA с шагом 1 мм (Spartan6), никогда до этого ничего подобного не делала Так вот, вопрос по ПП, у Микрона свои рекомендации к стекапам для DRR3, у Xilinx для Spartan6 свои, какие более приоритетны? Как лучше сделать? Возможен ли вариант с другим количеством слоев (3< х <12)? буду рада любой помощи =) Спасибо -

помогло Спасибо ^^ Всем спасибо)

-

не помогло(

-

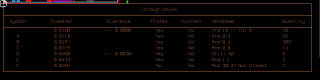

Добрый день! Пропала таблица "Through Holes" в Expedition PCB, причем Символы сверловки (Drill symbol/character assigment) появляются, а самой таблицы нет ( Drill Drawing-Through - включен (Display control -> General -> Drill Drawing ). Заранее спасибо за помощь)