pif68paf

Участник-

Постов

34 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о pif68paf

-

Звание

Участник

- День рождения 19.09.1968

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

-

Цена на CADSTAR 9.0

pif68paf ответил pif68paf тема в Zuken CADSTAR

:) Да мы тока что купили вагон этого САПР-а "по случаю", и выясняем (не представляясь естественно), сколько он стоит у конкурентов. Тоже будем приторговывать, где нибудь у "трех вокзалов", рядом с бабушками. которые укроп продают ;) Серьезно если, заказчик в нем работает, вот выясняем сколько надо пиастров на лицензию. Спасибо за информацию. -

Цена на CADSTAR 9.0

pif68paf опубликовал тема в Zuken CADSTAR

Здравствуйте! Подскажите пожалуйста сколько стоит "минимальная комплектация" CADSTAR 9.0 ? -

Платка

pif68paf ответил pif68paf тема в Примеры плат

Если не затруднит, ответьте пожалуйста на пару вопросов, которые наверняка не только меня интересуют, ну хотя бы на те, которые сочтете несекретными : ) Без схемы и софта это просто красивая платка. Т.ч. секретного ничего нет. Есть полезное, см. гербер и стекап. 1. В чем разводите(Mentor/Allegro)(или другое) ? Expedition 2005, HL 7.5, Xtreme 2. Сколько времени заняла такая разводка? Месяц. Использовали блоки, копировали топологию. Без авторазводки. В Xtreme неделю помогал товарищ. 2.1 Сколько стоит(оценочно) изготовление платы и время, которое ушло на это? 4500 за штуку. 3 недели. 3. Как паяется и отмывается опытный экземпляр(набор деталей автоматом + печь/паяльная станция+опытный монтажник/ другое(как?) ) (отмывка ручная/нет отмывки/другое)? Монтаж заказывали. Паяли в печи. + Опытный монтажник. Чем отмывали не знаю. Платы посмотрел, все очень хорошо, припоя ровно столько сколько нужно, пайки однородные, платы чистые. 3.1 Сколько стоит(оценочно) монтаж опытного экземпляра? 10000 р. Включая рентген контроль 5 БГА. Спасибо. Пожалуйста. -

Платка

pif68paf ответил pif68paf тема в Примеры плат

А фиг знает сколько, я с 96-го проектирую. Но "цифру", в общем можно делать на опыте, рекомендациях и врожденной паронои, (типа сто двадцать пять раз подвинуть один проводничек, точно зная что это ничего не изменит :). С аналогом и RF, для меня все похоже на "черную магию". Но грят, можно довериться тулзам, промоделировал, и спокойно отправляй в производство. Но я не уверен, что это так. И есчо, немного офтоп, но по теме: на платах очень часто шелкушкой нанесена разная инфа: Ну типа как на фото выше "перечеркнутая рука". Какие бывают информационые знаки и т.д. Может это как-то застандартизировано? Одним словом хотелось бы узнать что, где и какую информацию необходимо наносить. Я наношу только то что требует заказчик. Значёк этот всем понятен, боится статики, т.ч не возражает заказчик. А на счет ГОСТ-ов я не в курсе, надо у народа поспрашивать. -

Платка

pif68paf ответил pif68paf тема в Примеры плат

Таки смонтировали. Но подвели поставщики компонентов, придется самим кой чего добивать, а как не хотелось. Такие сроки поставки компонентов, что легче было бы наверно уже свой заводик в отечестве запустить. Вот думаем в штатах заказывать все, производство, комплектацию, монтаж. Уже нашел контакты, осталось сверить ценник. -

Проблемы с Silkcscreen Generator

pif68paf опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Вот такое сообщение частенько вываливается при запуске Silkcscreen Generator - а. Info: Failure loading the job preferences file "D:\WG200x_Projects\CROSS_BUR_16\PCB\Work\Layout_Temp\JobPrefsDB.jpf". А потом из приложения не выйти кроме как через диспечер задач. Не могу понять от чего это зависит. Бывает, все нормально отрабатывае на одном и том же проекте. Может кто сталкивался с проблемой? -

Платка

pif68paf ответил pif68paf тема в Примеры плат

И мне очень интересно. Надо с Сережей пивка попить. Все ж зависит от того чего он туда напихает, на сколько процентов будет заполнен Xilinx, на какой частоте "Лион" потянет ... Думаю "дуть" придеться обязательно, хотя заказчик мечтает обойтись без принудительного охлаждения. В общем, пока незнаю я :( -

Платка

pif68paf ответил pif68paf тема в Примеры плат

-

TopoR V3.0 beta

pif68paf ответил spf тема в Работаем с трассировкой

Пару лет назад один наш военный заказчик чуть не купил себе "топоров" :) Но все таки решил взять PADS. Так как нужен полный цикл проектирования МПП. Работа с библиотеками, заливками, дрс и т.д. В моем понимании "топор" это пока небольшой кусочек от полноценного САПР. Я не против "топоров", я даже очень рад, что хоть что то появилось в отечестве. Но вот товарищь на выставке, разочаровал. Мы с ним поговорили о той плате, что крутилась демонструхой на мониторе. Он меня спрашивают, вот вы ручками за сколько такую плату сделаете, я говорю ну день, может два. А он мне грит, а топор за 2 минуты. Я от такого "маркетинга" немножко офигел. Почему предлагая САПР надо использовать приемы торговли пирожками? И он быстренько переключился на более благодарных слушателей, чего со мной то дискутировать .... -

Платка

pif68paf ответил pif68paf тема в Примеры плат

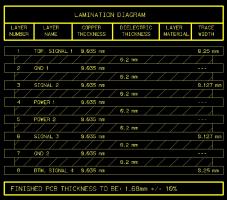

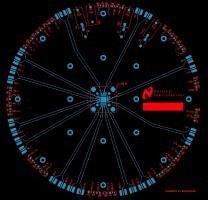

Привет Игорь, спасибо за ОТК :a14: На сигнальных слоях невысокий процент заполнения медью. Точнее наблюдается неравномерность заполнения. Технологи обычно не любят подобного на МПП с контролем импеданса - сложнее обеспечить повторяемость размеров геометрии рисунка в разных участках платы. Хотя все зависит от грамотности технолога и используемого техпроцесса. Наверно, "вообще" это верно, но конкретно в этой плате там где идут трассы с контролем импеданса, все нормально. Условия однородные. Под "rocket" слой земли. Можно было залить землей на сигнальных пространство слева, но не залил ... Нереференсное питание на слоях питания тоже не стал там подливать. Платы заказываем у проверенного поставщика, т.ч. сделают хорошо. Обратите внимание - не все апертуры считались корректно. Смотрите присоединенные рисунки (Dcode D23-D29). Я так понял что это пады конденсаторов обвъязки сар0402? По габариту ограничений не было? Про аппертуры перестал думать, как перешел на Expedition и на 274-X. У меня все читается без ошибок, на двух гербер-вьюверах, и CAM 350 тож молчит. Когда работал на Board Station, для 274-D делал таблицу апертур, мин. аппертуру задавал и т.д. Мин. конденсатор 0402, используем постоянно для объвязки под BGA c шагом 1 мм. Углы у подстеков подрезаем, что б зазор сделать поболе. Паяется без проблем. По геометрии рисунка и по отверстиям было понятно из гербера. Стек бы слоев посмотреть, если можно. Желательно с указанием типов используемых материалов. Стекап прицепил. Мы отдаем платы на стороннее производство. Сами подготавку к производству не делаем. Панели, купоны делают там же. Чего у них хлеб то отбирать? И так есть чем заняться :beer: Я рассчитываю волновое, толщины диэлектриков и препрегов задаю. А такой вот как у Вас на рисунке подробный stakup делаю крайне редко, когда заказываею не там где всегда, и если без ентого никак. И что на это сказали монтажники - пинали не шибко? Без проблем паяем платы с переходом в край пина, и даже в центр BGA пина. И еще камешек в ту же сторону - углы падов элементов лучше делать заокругленными. Значительно уменьшантся количество брака при нанесении пасты и при монтаже. С этим спорить не стану, но как то так исторически сложилось, что библиотеки которые были у нас в основе, были без скруглений (Italtel с нами поделился). Сами мы делаем футпринты по рекомендациям конкретного производителя, где тоже редко встретишь требование закруглить. Вообще говоря никогда нас технологи не просили "скруглить". Да и плат я насмотрелся забугорных при получении рабочих материалов, и тоже скругления не являются обязательными. Я бы отнес это больше к стилю проектирования, и исходным библиотекам, которыми пользуются дизайнеры, а не к проблемам технологическим. ИХМО. Кроме того, ходят упорные слухи, что на ВЧ не скругленные углы компонентов несколько "фонят" "Ходють слухи будто все подорожает, абсолютно, а особенно трусы и алкоголь" ? Как пел В.С. Высоцкий. Этим слухам верю. Ну а трассики то я все скруглил аккуратно, длинны выровнял, волновое посчитал. Перед тем прочитал все что Xilinx рекомендует по поводу"rocket", переходов, исключений и т.д. Там есть поважнее требования, чем скругления углов, хотя наверно, не повредило бы. Пока все. С наилучшими пожеланиями Игорь. И Вам спасибо. С уважением, Алексей -

Платка

pif68paf ответил pif68paf тема в Примеры плат

Здравствуйте, Игорь. Ясна. Virtex-5, прицепил нижний слой, и внутренний сигнальный. Инфа некоторая. Мин трасса. 0.127, отверстие 0.2, слоев 8, 4 сигнальных, 2 порезанных питания, 2 земли. Всего типов питаний 14. А их на теле нетуть, см. даташит :) Возможно и лучше, но так написано в ТЗ. Я видел эти картинки и раньше, спасибо. Для низкочастотных электролитов это не очень важно. У скоростных интерфейсов сделан переход в пин. И Вам удачи, спасибо за "свежий взгляд" С наилучшими пожеланиями, Алексей BTM_SIGNAL4_LAYER8.rar SIGNAL2_LAYER3.rar -

Платка

pif68paf ответил pif68paf тема в Примеры плат

Плата просто зашибись!!! Один у меня вопрос возник. Я только что закончил платку с такой же колодкой под DDR. Смотрю на чертёж, там после того как модуль памяти вставляется до платы 3.4 мм, от центра модуля, а от края 1.5 мм Не знаю, какая высота у компонента U28, но вот Y1 должен быть наверно 3 мм минимум. Как памятюха то за компоненты не цепляется ? ;) P.S. Прицепил верхний слой платки с 1.5 Гб трассами...TOP_SIGNAL1_LAYER1.rar -

Платка

pif68paf ответил pif68paf тема в Примеры плат

Проекты выкладывать низя, нарвется заказчик, фиг отобъешси ... 2 doomer#gp респект, как нынче молодежь выражается ...:) Долго делал? -

Платка

pif68paf ответил pif68paf тема в Примеры плат

Не, журнал бумажный, его листать надо, и давно это было, не найти. Да и чего на них смотреть, я вот делал для одной конторы "малоизвестной" конторы борду, правда они про то не знали, через посредника, у посредника куча индусов, мой ценник на первую плату их устроил, а потом я попросил как положено, что б не противно было работать, и тупо не выдержал конкуренции с родиной Раджи Капура :))