visht

Свой-

Постов

344 -

Зарегистрирован

-

Посещение

-

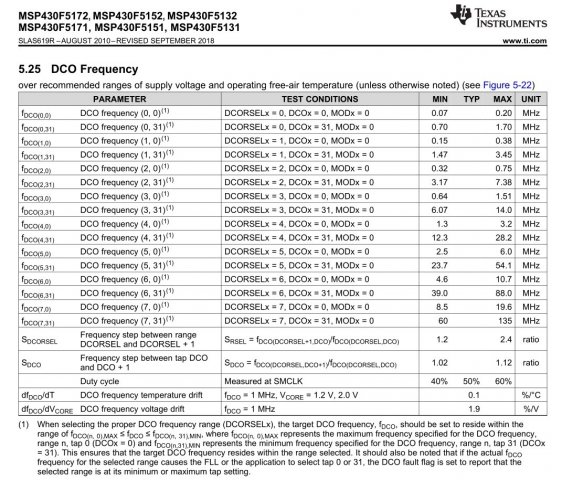

Ок, понял. тогда так: #define DCORSEL 6 PMM_setVCore(PMM_CORE_LEVEL_3); // Vcore setting of at max 3 for 24MHz MCLK UCSCTL1 = (DCORSEL << 4); UCSCTL3 = SELREF_2 | FLLREFDIV__1; // FLLref = REFO UCSCTL2 = FLLD__32 | 0x17; UCSCTL4 = SELM__DCOCLK | SELS__DCOCLKDIV; Поправьте меня, если я снова ... мимо. Выбираем частоту. D = 32, N = 23 , n = 1, REF0SC = 32768Hz Fdco = 32*(23+1)*(32768/1) = 25.165824 MHz выбираю диапазон чтобы моя частота Fdco была между MAX MIN для соответствующего диапазона DCORSEL для выбранной 25.165824 MHz это режим 6, от 10.7 до 39.0. управление DCO и MOD отдано FLL и установка частоты в моем случае заняла примерно 144728 циклов и 8.5ms в описании заявлено что не более чем n*32*32 циклов Fref = а это 31.25 ms а значит все верно. Видимо для получения точного значения частоты нужно просто подождать 30 ms. Проблема с DCOFFG остается, флаг не сбрасывается, хотя значения DCO в UCSCTL0 никак не 31 и не 0. do { UCSCTL7 &= ~DCOFFG; } while (UCSCTL7 & DCOFFG); // forever Видимо с системой флагов, у данного экземпляра что то пошло не так. Хотя как может не работать часть логики ... загадка. Пока нечем проверить точность частоты, LA семплит на 200 MHz, значит ошибка 8% (+/- 2 MHz), остается верить TI. А можно подробнее по поводу вышеупомянутого MSP430F51x2_UCS_04.c В закачанном msp430_driverlib_2_91_13_01 такого нет, есть другие, но если есть еще какие то примеры прошу ссылочку. k155la3, Спасибо за помощь.

-

может неверно понял, но вроде FLL сама должна DCO и MOD менять, если ей передано управление.

-

результат тестирования FLL UCSCTL3 = SELREF_2 | FLLREFDIV__1; // FLLref = REFO UCSCTL2 = FLLD__32 | 0x3FF; UCSCTL4 = SELM__DCOCLK | SELS__DCOCLKDIV; значение FLLN имеет смысл только до 0x08 все остальные варианты не увеличивают частоту. От внутреннего 32768Hz можно добиться максимум 4.718592 MHz режим Vcore = 3. Попытка раскачать FLL от XT1 - сваливается в дефолтный 32768Hz В чем я ошибаюсь ?

-

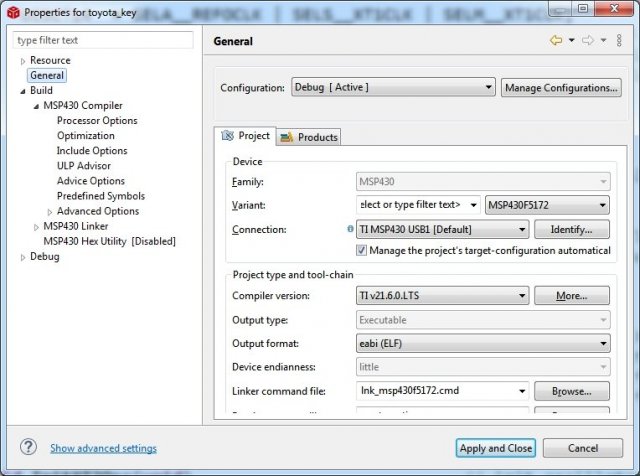

Сейчас что то взять проблематично. Да и суть задачи как раз в этом варианте корпуса. Это нормально для TI, к примеру RF430F5978 проект выложен, под CCS. Но MSP430Flasher да и они сами используют его как #include "cc430x613x.h" и ядро определяется так же. Но это всего лишь означает что с этому СС430Fxxx добавили рядом модуль, и подключили к ногам. остальные ноги вывели наружу, и дали другое название. Раньше так вообще выводы наружу делали, но сейчас экономят на выводах :) Я сравнивал хедеры, там все так же, и по тем же адресам. И выводы на порты говорят о том же. Попробуем FLL может хоть она заработает.

-

это MSP430F5172 слегка в другом корпусе Но ядро там MSP430F5172 о чем сообщает MSP-FET при подключении к MSP430Flasher

-

тестирую на рабочей плате, свою рисовать пока рано, да и делать негде, пока ... Fedex 23 февраля так и не довез мой заказ. конечно там есть к чему прицепиться, топорно сделано, кондеры блокировочные далеко от проца, но ... работало же у них. И даже если ... все равно сделано верно, выводы сначала на конденсатор, и уже от него на процессор. А толщина дорожек уж точно больше чем внутренние соединения к чипу. Даже Питание от CR2032 не решают проблему, могу конечно к ногам влепить 0402 но ... это не изменит ситуации. Есть другая платка, но там нет кварца, а цеплять на соплях - опять бездоказательно. Так ... нет такого кода. ошибка по флагам всегда. Был сброшен флаг HF при работе с LF. Что совсем нелогично, и рассматривается мной в контексте раз настроили LF то флага по HF и быть не должно. А то что флаг LF есть когда HF настроено, ну типа и не обращайте внимания.. А может должен тоже как бы сбрасываться, но не сбрасывается. т.о. нет ни одного верного варианта, флаги всегда устойчиво говорят об ошибке.

-

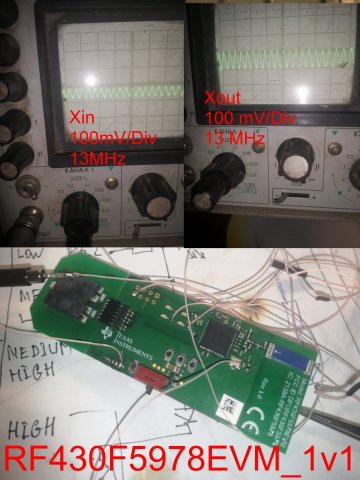

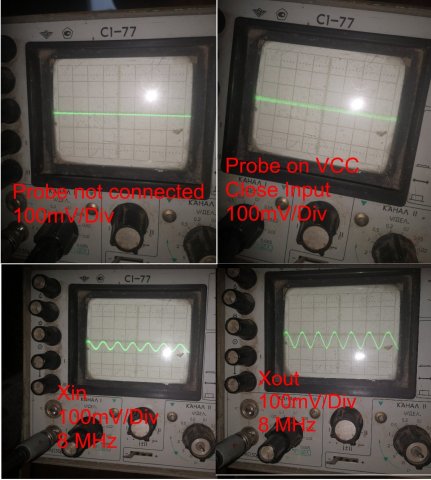

Errata почитать то можно, но ничего по теме там нет. Есть упоминание что при изменении делителей эти флаги надо чистить. По факту работы - на VCore при питании от MSP-FET или от Cr2032 пульсаций нет. Вид сигнала абсолютно идентичен состоянию открытого щупа. При питании от MSP-FET на VСС наблюдаются некоторые шумы, думаю что от питальника самого MSP-FET но они не критичны, и видны на картинках. При питании от CR2032 на VСС картина такая же как и на открытом щупе. Т.е. пульсации на уровне природного шума. Поэтому картинки по данным вариантам даже не прикладывал. По уровню, есть у меня эволюшн от TI и я на нем протестил сигналы кварца. И соответственно протестил их у себя. Я не вижу к чему придраться, все одинаково, никаких ... шумов, сбоев ... на глаз невидно. Смотрите... По резонатору, я поставил родной, который с емкостями своими. Так что и тут ... грешить как бы не на что.

-

так ведь и он нормально не работает, тоже флаг не сбрасывает. В при таком умножении ... насколько будет влиять теспературный уход по частоте ? Я проверил в качестве иcточника CR2032 (новая, 3.2V) , и ... все так же. на флагах висим. Что может быть лучше ? Да и кода тут ... пока только инициализация.

-

Не знаю что было причиной, скорее совокупность. На сейчас. генерация есть, на LF при XTS = 0, и на HF при XTS = 1. Но ... все так же флаги ошибок установлены, что на LF что на HF режимах. Если их проигнорировать, то оно как бы работает на генерируемой частоте. Но закрадываются сомнения что режимы LPM могут вести себя неадекватно из за того что процессор считает резонатор неверным. С выводом частот на пины у меня были странные глюки, может я что то не так делаю P2SEL = BIT6 | BIT7; P2DIR = BIT6 | BIT7; PMAPPWD = 0x02D52; // Get write-access to port mapping regs P2MAP7 = PM_TD0_0SMCLK; P2MAP6 = PM_TD0CLKMCLK; PMAPPWD = 0; // Lock port mapping registers При этом если я загружаю код через CSS то выводиться только на 2.7 pin, я так понимаю что MSP-FET теряет связь. А если выйти из отладки, то на обоих портах есть 1.015 МГц тест без запуска внещнего резонатора. Очень странно что отваливается отладка. По плате - все чисто. Промыл. просушил :) смущает то что даже от внутреннего генератора флаг OFIFG в SFRIFG1 остается в 1. Вообщем видимо остается пока надеяться на него, и попробовать настроить FLL.

-

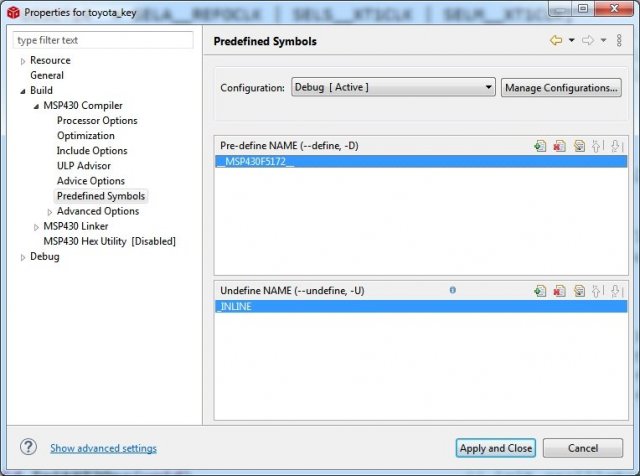

пробую на часовом кварце, тот же эффект, но генерация на ногах есть. И вот почему то становиться сброшен бит XT1HFOFFG а не XT1LFOFFG если его принять за верный, тогда он как бы стартует на 32768 может что то еще нужно сделать ? PMM_setVCore(PMM_CORE_LEVEL_0); PJSEL = BIT5 | BIT4; UCSCTL6 = 0x00; UCSCTL6 = XT2OFF | XCAP_0 | XT1DRIVE_0; do { UCSCTL7 &= ~(XT1HFOFFG | XT1LFOFFG | DCOFFG); SFRIFG1 &= ~OFIFG; } while (UCSCTL7 & XT1LFOFFG); конденсаторы оставил по 16 пик, чтоб не отпаивать. с выбором регистров тоже как бы все в норме. в CCS это выглядит так. В коде #include <msp430.h> а в нем уже #elif defined (__MSP430F5172__) #include "msp430f5172.h" Смотрю делителем на 10, как и у всех, на одном побольше синуса, на втором поменьше.

-

Прошу прощения, мерял до нажатия на "поехали" в отладке. 1V4 1V6 1V8 1V9 соответсвенно уровням от 0 по 3 вроде как тут все по даташиту.

-

1.408V. На плате конденсатор стоит. пульсаций нет. питаю от MSP-FET 3V.

-

проверил с этим UCSCTL6 = 0x0060; и с этим UCSCTL6 = 0x00; UCSCTL6 = XT2OFF | XCAP_0 | XTS_L | XT1DRIVE_2; И ... вообщем никак. Видимо у вас какой-то другой TI :) Мой опыт пока только негативный. Речь не только о процессорах а об микросхемах TI впринципе. По документации пишут одно, по факту все не так. И это еще хорошо если она вообще есть. По многим наблюдается ее полное отсутствие, причем даже тех что уже давно вышли из моды. А некоторые они вообще признавать не хотят, их упоминания даже на сайте TI нет. Насчет "компостера" недавний пример, Функция на входе массив, прерывания выключил, на выходе парсер. В отладке смотрю, фигню делает, откровенную, по шагам. и если по шагам дойти до конца фигня выходит. но если просто пройти без входа в функцию - все нормально. Второй пример, качаю MSP430.dll пакет, ну как бы должны же демо программы работать, а "фигвам", не работает. В итоге подменил входящую DLL той что из инсталла MSP430lasher.exe - заработало. А разрекламированный UniFlasher готовит архив под проц с MSP430lasher.exe и DLL но они не работают даже вместе... последняя версия, как вам такой TI?

-

4-х пиновый новый, при заказе всегда 5 шт на убой потерю оставляю. Да и перепаивал я их феном без проблем по несколько раз. поищу лодочку.