-

Постов

13 855 -

Зарегистрирован

-

Победитель дней

15

Uladzimir стал победителем дня 10 апреля

Uladzimir имел наиболее популярный контент!

Репутация

59 Очень хорошийИнформация о Uladzimir

-

Звание

Гуру

Старые поля

-

LinkedIn

Array

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

-

Altium Enterprise

Uladzimir ответил Realking тема в Altium Designer, DXP, Protel

Ну тут тоже умных хватает -

Altium Designer для начинающих

Uladzimir ответил ViKo тема в Altium Designer, DXP, Protel

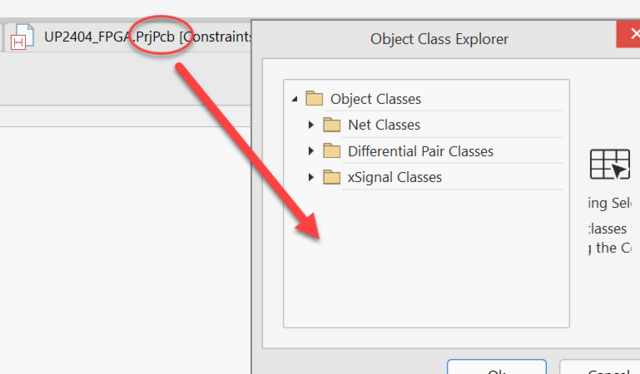

Это само собой. Но контроль этого в панели PCB очень приятен, если есть классы. Не нужно заходить на схему и выделять и сравнивать все. На небольших проектах это работает, на больших-- загнёшься все пересматривать. То есть бить схему на десятки маленьких листов -- это часто может не облегчить, а затруднить общую читаемость схемы. Тем более если их и так несколько десятков, а станет за сотню. В общем, когда первый способ (нормально рисовать) уже не справляется-- второй (через классы) - вполне рабочий и удобен. -

Altium Enterprise

Uladzimir ответил Realking тема в Altium Designer, DXP, Protel

Был точно, и некоторое первое время я даже модерацию делал Плюс был в него один точно-- регистрация на алтиум приходила через него мгновенно. Ну и ссылки на вебинары семинары и прочее тоже. Теперь ссылка на него переводит на общий сайт алтиума. -

Панель можно зафиксировать-- там есть кнопка-- не будет ездить туда сюда тогда

-

Altium Enterprise

Uladzimir ответил Realking тема в Altium Designer, DXP, Protel

Не уверен, но последний вроде уже все. Да он почти не активен был и так последнее время. -

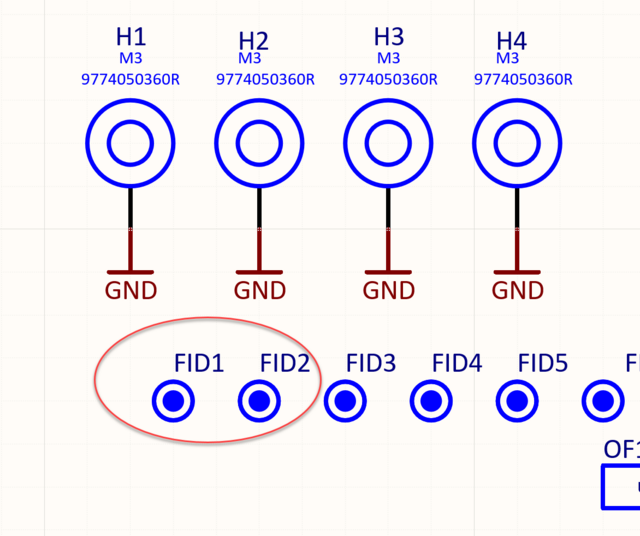

Altium Designer для начинающих

Uladzimir ответил ViKo тема в Altium Designer, DXP, Protel

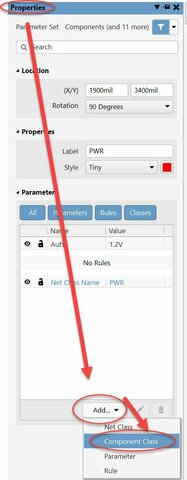

ну стоит (Component class). я использовал. когда на большом листе есть группы, которые нужно держать вместие. Те же конденсаторы, чтобы свои стояли у своих микросхем, а не у черта на куличках (тут футпринт не поможет). В общем есть задачи, где это может быть уместным. Pаd class на схеме не задашь. и даже в новом Constraint для схемы нет разделов от PCB -

Вы заблуждаетесь. в реальных схемах 99% никаких назначение выводов в схемах для FPGA нет( как в библиотечном компоненте введено-- так на схеме и оставлено). По крайней мере мне таких схем, где сделано переназначение не попадалась. У Вас наверное первая, но я ее не видел.

- 3 ответа

-

- 1

-

-

Так извиняюсь. По умолчанию там все IO (по библиотеке), если не считать Power и несколько системных. а уж что там реально назначено - это работа программера FPGA и из его оболочки должно вытягиваться. Хотя кому, кроме него это нужно-- не понятно і

-

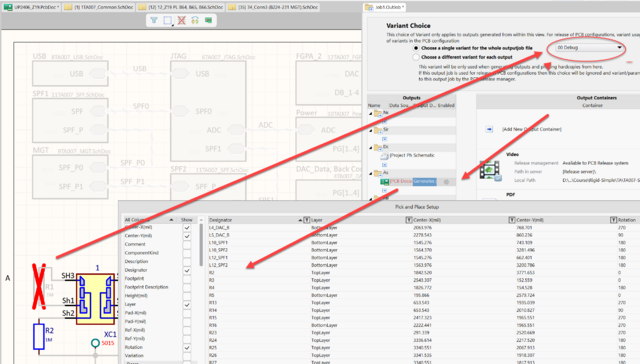

Altium 21.6 и выше

Uladzimir ответил Uladzimir тема в Altium Designer, DXP, Protel

-

Altium Designer для начинающих

Uladzimir ответил ViKo тема в Altium Designer, DXP, Protel

-

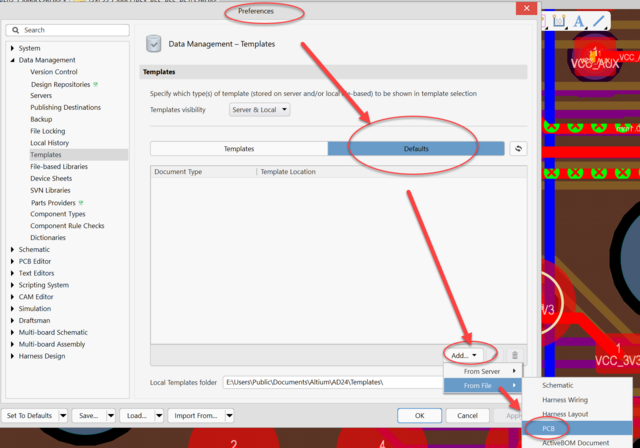

шаблоны

Uladzimir ответил Shamsutdin.xxx тема в Altium Designer, DXP, Protel

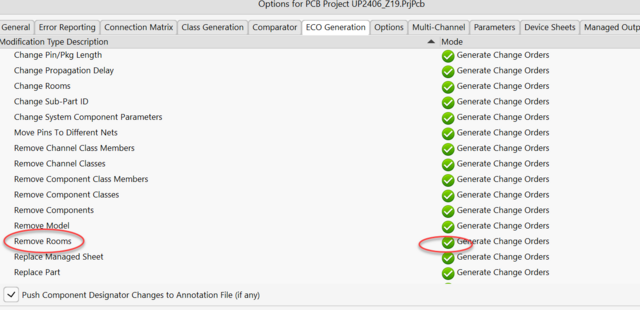

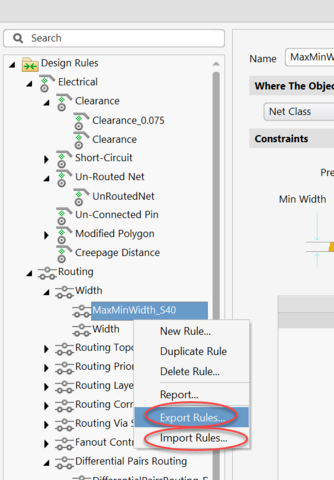

1 создайте набор правил. Сохраните правила в файл и считайте его шаблоном. Подгружайте правила из шаблона в новые проекты 2. Создайте и настройте PCBDOC. Укажите его в качестве Default -

Altium Designer для начинающих

Uladzimir ответил ViKo тема в Altium Designer, DXP, Protel

Да . Многие именно так и делают. Само УГО может быть разным. я многого насмотрелся. Если есть нормоконтролоь и он запрещает (странно, не должен), или не хочется, чтобы при печати выводился в PDF-- можно на отдельном листе схемы размещать. -

Altium Enterprise

Uladzimir ответил Realking тема в Altium Designer, DXP, Protel

-

Если проверять не надо конкретные -- ставьте на них директву No ERC . В ней можно указать что не проверять с данной цепью. Но это не в библиотеке, а на схеме. Если у конкретного компонента хочется показать направления, но и пользоваться проверкой--- тогда правильно на схеме все и подключайте. Если всегда не важно у пина это проверка но показать направление хочется хочется (это скорее всего ваш случай случай. ) ставьте Passive в библbотеке для него, а направление и другие свойства для него указывайте вручную. Обычно я так і делаю. Там, кстати много чего можно показать

-

Altium Designer для начинающих

Uladzimir ответил ViKo тема в Altium Designer, DXP, Protel