adnega

Свой-

Постов

3 571 -

Зарегистрирован

-

Посещение

-

Победитель дней

3

adnega стал победителем дня 1 декабря 2023

adnega имел наиболее популярный контент!

Репутация

10 ХорошийИнформация о adnega

-

Звание

Гуру

- День рождения 01.05.1982

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

-

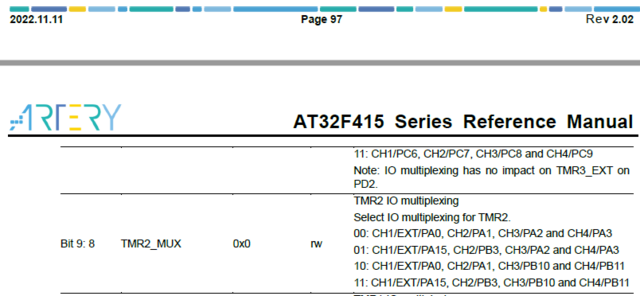

А разве TMR2 должен ремапиться на PB8/9 ? "Non-timer peripherals has priority over timer peripherals". Нужно проверить, что на этих пинах нет никакой нетаймерной периферии. Кста, в чем отличия _MUX и _GMUX регистров?

-

-

li t0, 0x1f csrw 0xbc0, t0 /* Enable nested and hardware stack */ li t0, 0x0b csrw 0x804, t0 /* Enable floating point and interrupt =0x6088 / =0x7888 */ li t0, 0x7888 csrs mstatus, t0 la t0, _vector_base ori t0, t0, 3 csrw mtvec, t0 /* la t0, main csrw mepc, t0 mret */ j main Можно поправить исходный примерно так.

-

В своем загрузчике startup от производителя не заработает, т.к. там делается переход в U-режим. И уже попытка записи csr в startup приложения вызовет сбой.

-

Чему равен Page_Address ? #define FLASH_BANK1_END_ADDRESS ((uint32_t)0x807FFFF) - не много для 16кБ флешки?

-

2000014a: jalr t0,160(zero) # 0x0 <_start> А это что? Что лежит по адресу 0xA0 ?

-

Почитал внимательно . ТС вызывает функции из функций )) Да, функции находятся в ОЗУ, но они могут использовать флешовые __riscv_save_0/__riscv_restore_0 Выглядит так: в начале функции 200000e0 <test_ram>: { 200000e0: 0c0002e7 jalr t0,192(zero) // 192=0xC0: <__riscv_save_0> 200000e4: 03000793 li a5,48 while(!(USART1->STATR & (1 << USART_STATR_TC))); ... и в конце 20000138: dfe5 beqz a5,20000130 <test_ram+0x50> test_foo(); 2000013a: 37b9 jal 20000088 <test_foo> - вызов вложенной ram-функции } 2000013c: 0ca00067 jr 202(zero) // 202=0xCA: <__riscv_restore_0> 000000c0 <__riscv_save_0>: c0: 1151 addi sp,sp,-12 c2: c026 sw s1,0(sp) c4: c222 sw s0,4(sp) c6: c406 sw ra,8(sp) c8: 8282 jr t0 000000ca <__riscv_restore_0>: ca: 4482 lw s1,0(sp) cc: 4412 lw s0,4(sp) ce: 40a2 lw ra,8(sp) d0: 0131 addi sp,sp,12 d2: 8082 ret

-

посмотрел v003 сильно отличается: CSR 0xBC0 - отсутствует; U режима нет совсем (mstatus.MPP=0b11, т.е. всегда в режиме M).

-

Не ваш случай, но на старших камушках еще и с частотой непонятки: ядро может 144МГц, а флеш то ли 120, то ли 60 МГц максимум. Типа нужно замедлятся при работе с флешью. Причем, read тоже за работу считается - не понятно(

-

Прямо сейчас на ch32v307 подобным занимаюсь. Код слинкован с адреса 0x0000_0000, но шить нужно по адресам флешки 0x0800_0000, иначе FLASH_STATR_EOP не взводится. Еще добавлю загадочный CSR 0xBC0. Туда пишется нечто, отвечающее за выборку. Может его как-то нужно сбрасывать, чтоб на флешку не влиял? И стартап от WCH любит из M переключить в U-режим исполнения. Привилегий меньше, и при работе с CSR можно улететь в HF. Кста, установка RDP блокирует от записи первые 4кБ.

-

Примерно в то время использовал КР1878ВЕ1, но мало.

-

А если по делу, то MCP я бы в trt.ru поспрашивал.

-

+1 Я везде закладываю возможность обновления прошивки. И после этого позволяю себе не боятся граблей в прошивке)

-

Сам пользуюсь расширителями на МК - периферийными контроллерами. Обновление прошивки нужно, но с каких пор это проблема?

-

Придется скрещивать. Готовой реализации Host для Миландра не нашел - нужно будет ее делать. А реализацию MSD-класса можно взять/подсмотреть из чужих исходников. Глянул, по-моему, Host в Миландре больше похож (но не есть одно и то же) на CH32V203, а не на STM32.