Поиск

Показаны результаты для тегов 'zynq'.

-

Может быть у кого-то был опыт запуска ThreadX в режиме SMP (symmetric multi processing) на Zynq-7000. Вроде в исходниках на гите (https://github.com/azure-rtos/threadx) есть порт, но не удается его запустить (проц подвисает на ошибке обращения к памяти). Буду рад любой помощи, кроме отсылок к Linux - проект устоялся и переходить на него нет смысла (сейчас все работает под ThreadX с одним ядром).

-

zynq Новое подсемейство Zynq RFSoC от AMD-Xilinx

МакроГрупп опубликовал тема в Объявления пользователей

В семействе Zynq RFSoC от AMD-Xilinx пополнение – новое подсемейство Zynq RFSoC DFE. DFE- это Digital Front-End (цифровой тракт предобработки). Сейчас в этом подсемействе анонсированы 2 модели: ZU65DR и ZU67DR. Подробности -

Добрый день. Не могу вывести данные через uart . ls /dev выдаёт наличие 2 uart : ttyPS0 и ttyPS1. echo "1" >/dev/ttyPS0 выводит данные , а echo "1" >/dev/ttyPS1 нет. Может быть кто сталкивался или знает где копать?

-

Компания Макро Групп приглашает на вебинар по нейронным сетям разработчиков решений на платформах Xilinx и специалистов по искусственному интеллекту и нейросетям. На вебинаре вы узнаете, какие шаги необходимо выполнить для запуска собственной сверточной нейросети на платформе Xilinx Zynq Ultrascale+, и увидите её работу на отладочной платформе Xilinx ZCU104. Узнаете, как это сделать и на других платформах Xilinx. Зарегистрироваться

-

- zynq

- ultrascale

-

(и ещё 4 )

C тегом:

-

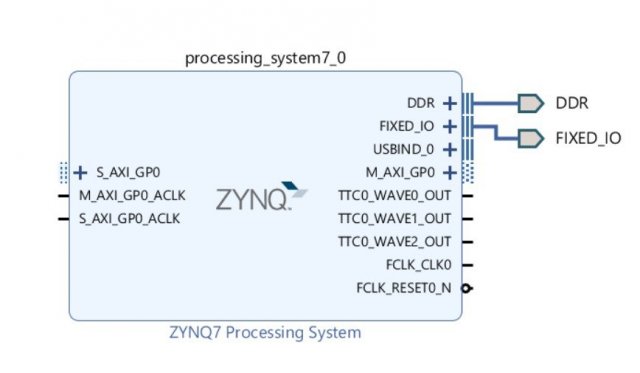

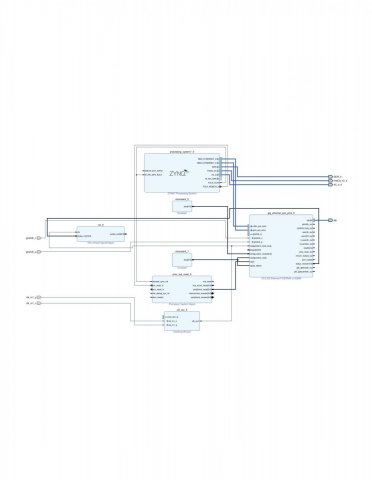

Я написал функцию "memcpy" для копирования блока данных с исходного адреса на адрес назначения. Хочу протестировать на плате (Zynq). Я новичок в MCU и изучаю эту тему самостоятельно, извините, если мой вопрос для вас глупый. Что я сделал: Я создал проект в vivado, начал block design с Zynq, изменил конфигурацию PS-PL (добавил GP Master и Slave AXI Interface) [Смотри приложение]. Я читал, что Zynq может быть Master, но Slave/ периферийнoe устройство я должен спроектировать как настраиваемое IP-ядро. Я уже нашел, как создать собственный AXI IP (slave или master). Vivado создает шаблон настраиваемого IP-ядра (slave). (1) Могу ли я использовать этот шаблон без каких-либо изменений? (2) Следует ли мне добавить дополнительную информацию (сигналы, которые я использую в функции memcpy: адреса и количество битов)? Я пропустил дизайн custom master . (3) Я сделал правильно или мастер должен быть частью настраиваемого IP ядра?

-

В данном вебинаре вы подробно познакомитесь с данными модулями, узнаете о сферах и особенностях их применения, а также увидите наглядную демонстрацию запуска ПО на данной платформе. Программа вебинара: Введение Что такое SoM-модули Kria? Магазин готовых приложений Сравнение модулей Kria K26 и Jetson TX2 Первая в мире несущая плата для SDR на основе KRIA Пример запуска приложений из магазина Xilinx Итоги, выводы и ответы на вопросы Подробнее

-

zc706 xilinx kit sfp

Drakonof опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет. Не могу понять как поднять sfp на zc706 dev kit. Vivado 2018.3 В общем есть кит zc706 и sfp (1Gbps) модуль d-link DEV-310T. Для начала нужно просто запустить в internal loopback режиме. Как я понял этот режим работы конфигурируется через configuration_vector порт ip ядра 1G/2.5G Ethernet PCS/PMA or SGMII, поставил const ip на 5 разрядов со значением 2 (1G/2.5G Ethernet PCS/PMA or SGMII v16.0 LogiCORE IP Product Guide стр. 62), вроде никаких больше установок для этого вектора не нужны (в тч Auto-Negotiation Enable). Ядро настроенно как Tri-Mode Ethernet MAC, стандарт 1000BASEX, Receive GMII Clock Source: TXOUTCLK. после сборки и портированрия бинарника и hw файла в sdk, запустил в нём lwIP Echo server пример в котром проследил что тактовый генератор (SI5324) запрограммировался (если верить статусам драйвера i2c), но сам phy изернета проходит только пару шагов инициализации по I2С и начинает слать статус ошибки. Коллега мне объяснил что phy не нужно инитить и он должен работать по дефолту, я функцию закоментировал. пример шлёт в терминал: -----lwIP TCP echo server ------ Start PHY autonegotiation Waiting for PHY to complete autonegotiation. autonegotiation complete link speed for phy address 0: 1000 DHCP Timeout Configuring default IP of 192.168.1.10 Board IP: 192.168.1.10 Netmask : 255.255.255.0 Gateway : 192.168.1.1 TCP echo server started @ port 7 и повисает, при этом после строчки "link speed for phy address 0: 1000" пример секунд 10 ждет. Не очень понимаю, это ошибка сборки моего проекта или он ждёт каких то действий) Народ подскажите куда копать что бы sfp начало что то слать в loopback. xlconstant_1[0:0] == 1 xlconstant_2[4:0] == 2 (loopback control == 1) status_vector порт ethernet ip идущий на vio == 0, что говорит: бит 0 и 1 -> нет линка (1G/2.5G Ethernet PCS/PMA or SGMII v16.0 LogiCORE IP Product Guide стр. 64), а loopback он должен быть? Еще уточнение, sfp заткнут заглушкой, те без патчкорда, но на сколько я понимаю в данном режиме это не важно. Заранее спасибо за советы. design_1.pdf -

Дооброго времени суток. Читал я тут соседние темы на форуме и вспомнилась старая задача для проекта на Zynq. А именно как можно увеличить адресное пространство (в Address Editor BD) с одного гигабайта до хотя бы двух. В спецификации указано что из 32х бит адресного пространства 3 Гб зарезервировано под внутренние нужды ARM и только 1 Гб доступен для адрессации "периферии" в PL. Один из вариантов - это сделать переключатель по какому-то адресу и свитчить выходные адреса старшим/младшим виртуальным битом. В таком случае проблема вылазит в конфигурации карты и сложность в обратоном чтении от устройств (их около 2х десятков). Второй вариант - подключить несколько устройств на одинаковые адреса, но управлять сигналом разрешения работы (нет необходимости работать паралельно). Проблема конфигурации карты остаётся ну и частичнаф сложность в реализации. Собственно какой вариант лучше/использовался юзерами. Или же есть ещё какой-то способ проще/лучше p.s. Раздумия над AXI передачей наводят на мысль, что собственно адреса "раздаёт" AXI Interconnect, при том, что вся остальная перифферия особо то ничего и не знает что и где лежит (отсюда и требование подключения одной связки master-slave). Насколько данная мысль правильная? Может есть какой-то способ "обмануть" или конверизировать адреса в Interconnect'е, тогда задача решится сама собой.

-

В двух словах. Во-первых, это мой первый опыт с Zynq, во-вторых, не могу уловить суть работы с потоковой шиной AXI-Stream. Или не понимаю сообщений от тайминг-аналайзера. Теперь подробней... Перед собственно запуском АЦП, наслушавшись как в Zynq все быстро и удобно, посмотрев несколько видео, и почитав несколько статей, создал простой проект, где Microblaze для конфигурирования в будущем АЦП и ЦАП, а ARM уже для работы с данными. Есть общая память между Zynq и Microblaze, есть общая периферия. Частота работа с периферией 50 Мгц. Раньше делал со стороны ARM 100 МГц, сейчас сделал поменьше. Не уверен, что выходную частоту процессорного ядра можно использовать в FPGA безболезненно, поэтому пропустил на всякий случай клок через Clock-wizard. Создал пару кастомных компонентов куда в дальнейшем перекочует работа с АЦП и ЦАП соответственно. И для проверки "скелета" все соединил и собрал. Сообщения про времянки уверяют меня, что ничего не работает. Пробовал вставлять регистры, вставил двухклоковую FIFO, опустил частоту работы с портом HP до смешных значений. Увеличил разрядность с 32 до 64 разрядов, завел два выхода в компоненте и использовал сразу два порта HP, помня рекомендацию Xilinx, что подключать нужно к портам через один, т.е. к 0 и 2 или к 1 и 3. Можно услышать от опытных людей критику по структуре проекта в целом и рекомендации по констрейнам? Я так понял, что как и для спартан-6 констрейны нужно прописывать только ко входной частоте, а производные клоки просчитываются автоматически. Тут также? Проект размещу по ссылке, т.к. его размер превышает ограничение в 5 Мб: EK-Z7-ZC702-G_Zynq_MB

- 19 ответов

-

- zynq

- microblaze

- (и ещё 4 )

-

Всем здравствуйте. Если кто хочет начать работать с Xilinx Zynq, но не может купить отладочный комплект или не видит смысл вкладывать в это средства, предлагаю взять погонять отладку совершенно бесплатно. Отладка Minized вполне подойдёт для начала знакомства с системой на кристалле Xilinx Zynq. Ссылка на видео с кратким обзором Minized и как её получить

-

Добрый день, хочу поделится ссылкой на проект U-boot для платы ZedBoard Возможно будет полезно новичками которые хотят подробнее разобраться с загрузчиком или что-то подправить под себя. Проект позволяет собирать U-boot из исходников и так же запускать его из под SDK с точками останова как в режиме bare-metal. Все инструкции в репозитории + видеоинструкция. Если у кого получится повторить буду рад услышать ответ. Из особенностей для отладки пришлось закомментировать часть функций SPL, все комментарии добавленные мной начинаются с /* mollex: comment , количество небольшое. Ссылка на проет: https://github.com/mollex/workspace20154_uboot_dev

-

fpga Разработка прошивки для ПЛИС и Zynq; тестового ПО на Linux

von.gostev опубликовал тема в Предлагаю работу

Город Москва Оплата 250000 за проект Работа по договору с физлицом. Срок на изготовление три месяца. Дальнейшая платная поддержка при необходимости. ТЗ прилагается. Решается задача кодирования и декодирования цифровой информации по заданному алгоритму. Необходимо разработать прошивки для кодера (Digilent Cmod A7-35T) и декодера (Zynq 7020 + Digilent Pmod DA3 + Analog Devices EVAL-AD9467), а также тестовое ПО для Linux, совместимое с Raspberry Pi 2, или же API для доступа к устройствам из-под Linux. Техническое_задание_на_программный_комплекс_кодирования_и_декодирования_цифровой_информации.pdf -

Добрый день! Необходимо сконфигурировать с помощью zynq ацп и цап, имеющий только 3 - х проводный spi. Axi-quad SPI работает только в 4-х проводном. Может кто сталкивался, как это можно сделать? Спасибо.