Поиск

Показаны результаты для тегов 'xilinx'.

-

Добрый день! Начну из далека) Для уже имеющегося верифицированного блока DisplayPort версии 1.2 был написан HDCP 1.3 на языке описания аппаратуры Verilog. Блок HDCP был проверен отдельно от DisplayPort. Для теста были использованы тестовые ключи из документации HDCP. Все эталонные данные совпали с данными в проверяемом HDCP блоке. Симуляция производится в SimVision от Cadence. Далее HDCP проверялся в составе DisplayPort. За эталонную модель было решено взять IP блок Xilinx DisplayPort TX Subsystem v2.1 в конфигурации с HDCP 1.3. IP блок DisplayPort TX был синтезирован в Vivado 2020.1 и был сгенерирован Verilog файл содержащий в себе модуль Xilinx DisplayPort TX Subsystem v2.1 (модуль dptx_ss в файле tb_xil_dptx.v). Управление Xilinx DisplayPort TX Subsystem v2.1 происходит при помощи записи и чтения в регистров управления по средствам AXI-4 lite interface (Настройку DP можно посмотреть в файле: tasks.v, таска: dp_xil_tx_init). После настройки и включения DP производиться процесс аутентификации, который проходит верно, ключи R0 и M0 совпадают с тестовыми (используются тестовые ключи из спецификации A1 и B1). Тут возникает проблема при включении шифрования HDCP: при записи значения [32'h0000_0001] в регистр Cipher Control по адресу ['h1050] и ожидания управляющего сигнала SR (Scrambler Reset), ожидается включение шифрования потока данных, но этого не происходит. Нулевой бит в регистре Cipher Status по адресу ['h1054] не принимает значение [1'b1]. Возможно я допустил ошибку в порядке настройки DP и HDCP, хотя руководствовался драйверами из Example проекта Xilinx. Файлы тестбенча прикрепляю. Может кто-то настраивал блок Xilinx DisplayPort TX Subsystem v2.1 и запускал шифрование потока? Ссылки на документацию: 1) DisplayPort 1.2 - Ссылка 2) HDCP 1.3 - Ссылка 3) Xilinx DisplayPort TX Subsystem v2.1 - Ссылка 4) Xilinx HDCP 1.x v1.0 - Ссылка tasks.v tb_xil_dptx.v list_global_defines.v

-

Доброго всем дня, Столкнулся с ещё одной проблемой наличия линка на PCI-E у плат с Артиксами, причём в этот раз LTSSM не может пройти дальше практически самой начальной фазы - Detect.Active, т.е. не отрабатывает процедура Receiver Detection. В описании GTP есть следующий пункт: Судя по нему в начале процедуры определения наличия приёмника ПЛИС должна установить уровень сигнала на линиях TXN и TXP равным (Vdd - Vswing/2). Отдельный вопрос, какое именно значение Vswing они считают правильным, но я предполагаю что 500 мВ. Vdd судя по всему это Vmgtavtt, т.е. 1,2 В. Т.е. в итоге на выходах ПЛИС должно появиться значение напряжения около 0,95 В. Далее, судя по описанию, происходит отключение управляющей цепи и уровень сигнала должен вернуться к Vcmoutac (1,2 В / 2 = 0,6 В) и ПЛИС через заданный интервал должна измерить величину напряжения на линиях TXP/TXN, по которому принимается решение о наличии на линии приёмника. Это полностью согласуется с логикой описания этого процесса в спецификации PCI-E: Однако по факту я наблюдаю совсем другую картину: 1. перед началом процедуры определения приёмника напряжение на выходах 560 мВ; 2. при включении режима определения приёмника на выходе ПЛИС появляется уровень 1,18 В с крутым фронтом (если приёмника нет или он не готов), если приёмник есть и с ним всё хорошо, то уровень около 960 мВ. 3. далее передатчик ПЛИС формирует крутой спад сигнала и уровни возвращаются к исходным 560 мВ; Т.е. не видно никакого длительного процесса заряда-разряда конденсатора, по которому бы ПЛИС с помощью компаратора (сравнивающего уровень сигнала в линии с опорным значением) могла судить о наличии приёмника на другом конце. Напротив, всё выглядит так, что ПЛИС формирует достаточно мощный импульс и в зависимости от получившегося практически стабильного по времени уровня напряжения принимает решение о наличии/отсутствии приёмника. Проблема в том, что на некоторых слотах x16 (подключённых напрямую к процессору) процессор далеко не сразу правильно настраивает свои приёмники (подключает терминаторы) или они не сразу включаются и в результате ПЛИС не может определить их наличие, а значит пойти дальше по графу состояний LTSSM. При этом особенно интересно, что в то же самое время, пока ПЛИС не может определить наличие приёмника на другом конце, процессор успешно видит приёмник в ПЛИС и начинает слать TS1/TS2, пытаясь поднимать линк. Однако через некоторый таймаут всё это прекращается, т.к. он по всей видимости не дожидается получения TS1/TS2 от ПЛИС, что логично, т.к. ПЛИС не видит приёмника. Т.е. по факту процессор сам себе обрубает линк с платой. При этом после тёплого ресета линк стабильно поднимается (процессор прогрелся и у него стало всё хорошо? 😉). Такое поведение наблюдается на паре материнских плат и число чудящих Artix`ов всего два. При этом такая проблема далеко не нова - https://support.xilinx.com/s/article/51135?language=en_US Правда в моём случае процессор не третьего, а четвёртого поколения, для которого такой эрраты в доступной документации нет и значение TX_RXDETECT_REF уже равно рекомендованному 3'b011. На проблемных платах помогает уменьшение TX_RXDETECT_REF до значения 3'b010, при этом на рабочих платах увеличение значения TX_RXDETECT_REF до 3'b100 ломает установку линка. Однако логика работы параметра TX_RXDETECT_REF непонятна, т.к. в первую очередь кажется, что этот параметр определяет пороговое значение опорного уровня сигнала внутренного компаратора, при котором приёмник считается подключенным к линии. Однако если установить значение 3'b000, то я вижу, что максимальный уровень выходного сигнала ПЛИС в процессе проверки наличия приёмника снижается до 1,03 В вместо исходных 1,18 В. При этом Detect.Active пролетает с первого раза. Если всё так хорошо, то почему AMD (Xilinx) рекомендует ставить 3'b010 в крайнем случае и то после консультации с их техподдержкой? Есть-ли у кого-нибудь понимание, как на самом деле работает механизм определения наличия приёмника у Xilinx в седьмой серии? В шестой серии, судя по осциллограммам, механизм реализован плюс-минус также. Чем на практике чревата установка низких значений TX_RXDETECT_REF? PS: предложения вида "забить и забыть" принимаются, но игнорируются, т.к. в серии возможны массовые отказы и/или проблемы в совместимости. Поэтому ищется решение, которое бы гарантировало работоспособность плат на Артиксах в максимально широком спектре материнских плат и платформ.

-

Макро групп начинает сотрудничество с ALINX Electronic Technology (Shanghai) – производителем встроенных интеллектуальных продуктов и технологических решений на базе программируемых логических интегральных схем, а также сопутствующих плат расширения. Подробнее

-

Вебинар: ПЛИС и отладочные платы PangoMicro

МакроГрупп опубликовал тема в Объявления пользователей

Приглашаем на информационно-технический вебинар, посвящённый продукции китайских компаний PangoMicro и Alinx. В связи с усиливающимися санкциями все настойчивее встает вопрос замены компонентов производства западных компаний. Компания Макро Групп, являясь ведущим центром компетенций по применению продукции Xilinx, так же занимается поставками аналогов от китайских производителей. Подробнее -

Поставщик чипов для электроники Boyukang IC CHIP

ADLBYK опубликовал тема в Производители

http://www.wtschipic.com Компания Shenzhen Boyukang Electronics Co., Ltd. была основана в 2013 г. Являюсь независимым дистрибьютором электронных компонентов IC и CHIP. У нас есть филиалы и склады в Гонконге! У нас очень хорошие партнеры в Европе и США, на Филиппинах, в Таиланде, в Корее! Вы можете запросить у нас цену в любое время! Мы продаем только оригинал, только оригинал! RFQ Assistants : Web: http://www.wtschipic.com Email:[email protected] [email protected] 24 hoursOffice: +8618565402363 Whatsapp:+8613760167773 WeChat:8613760167773 -

Приглашаем принять участие в вебинаре, посвященном ПЛИС и отладочным платам для аналогов Xilinx Kintex-7 от китайских производителей. В процессе вебинара будут рассмотрены аналоги Kintex-7 китайского производства и продемонстрирована работа с соответствующей отладочной платой. Будут рассмотрены проблемы и сложности, которые могут возникнуть в процессе применения китайских ПЛИС, и возможные пути решения этих проблем. Подробнее

-

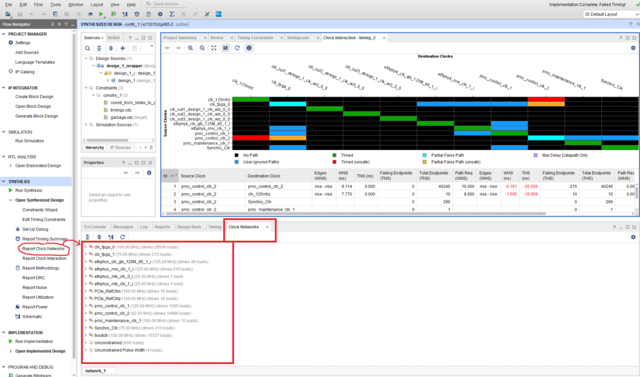

Implementation complete, failing timing!

Jul'etta опубликовал тема в Среды разработки - обсуждаем САПРы

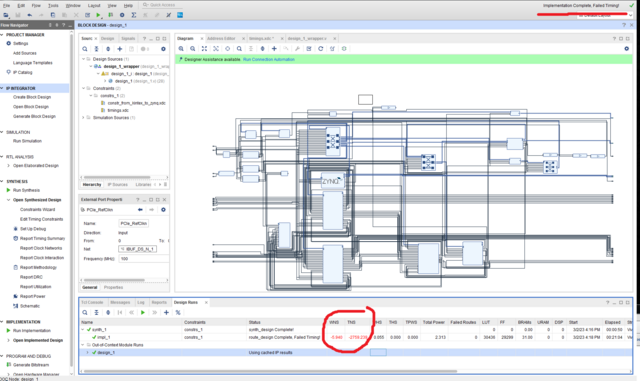

Здравствуйте. Уже пару недель бодаюсь с проблемой таймингов в проекте. Задача такая: портировать проект с одной платформы на другую. Был проект под Kintex с программным процессором микроблейз, нужен под Zynq с аппаратными процессорами арм. Соответственно, править начала с блочного дизайна в Vivado. Этап синтеза проходит без ошибок, далее имплементация - и вот тут начинается интересное. Проект пока не проходит по таймингам. Что было сделано: ознакомилась с документом "UG903 Using Constraints". Файл с временнЫми ограничениями (timing constraints) перешел ко мне от старого проекта, в соответствии с документом разобралась как это пишется. Прочитаны статьи по конвейеризации проекта (как один из вариантов решения проблем с временем распространения сигналов) - но не пойму куда (в какое место в коде) тут надо вставлять регистры, да и поможет ли это? Прочитана статья по стратегиям синтезатора. Подскажите, пожалуйста, в каком направлении копать? Разбираться ли плотней с конвейеризацией схемы или лучше изучить стратегии синтезатора или прописывать новые и новые временнЫе ограничения в файле? timings.xdc -

Микросхемы Xilinx Spartan2, Spartan3, Spartan3a, Spartan6 индустриального диапазона в количествах около 5 шт каждой. XC2STQ144I, XC3S1000FTG256I, XC3S400AFTG256I, XC6SLX100-3fgg484i Цена обсуждается- ориентировочно 50% от цены чип и дип +/-. Отправка Boxberry/Cdek.

-

Компания AMD Xilinx официально объявила о продлении поддержки всех ПЛИС 7 серии и адаптивных СнК до 2035 года. Это включает все классы скорости и температуры для ассортимента СнК Zynq ®-7000 , а также ПЛИС Kintex®-7 и Virtex®-7. Подробнее

-

- zynq-7000

- kintex ultrascale

- (и ещё 4 )

-

zynq Новое подсемейство Zynq RFSoC от AMD-Xilinx

МакроГрупп опубликовал тема в Объявления пользователей

В семействе Zynq RFSoC от AMD-Xilinx пополнение – новое подсемейство Zynq RFSoC DFE. DFE- это Digital Front-End (цифровой тракт предобработки). Сейчас в этом подсемействе анонсированы 2 модели: ZU65DR и ZU67DR. Подробности -

Микрокомпьютер raspberry pi 4 память 4Гбт + установлен радиатор, коробка есть, (после покупки поставил радиатор, подключил камеру, проверил проект на openCV и все! Состояние новый!) цена 15т.р. Микрокомпьютер orange pi pc v1.3 новый, не распакован, цена 3500р. Отладочная плата NUCLEO-H743ZI2, Отладочная плата на базе MCU STM32H743ZIT6U (ARM Cortex-M7), STLINK-V3E новая, цена 8000р. XILINX Platform Cable USB waveshare новый, цена 8000р. ULINK2 цена 2000р. Отладочная плата XILINX spartan XC2S50 цена 3000р. Отправлю почтой РФ по предоплате на карту сбербанк.

- 4 ответа

-

- stm32h743zit6u

- xilinx

-

(и ещё 2 )

C тегом:

-

Два новых загружаемых приложения, которые могут значительно сократить время разработки некоторых промышленных приложений, теперь доступны в магазине приложений AMD Kria™. Эти приложения, разработанные для плат KR260 с сертификацией Ubuntu 22.04 LTS, используются в сочетании со скромным по цене стартовым комплектом AMD Kria KR260 Robotics Starter Kit ($349 USD). Разработчики могут создавать сложные промышленные системы с аппаратным ускорением для промышленного управления и машинного зрения на стартовом комплекте робототехники Kria KR260 с минимальным опытом использования Linux и без опыта работы с ПЛИС. Подробнее

-

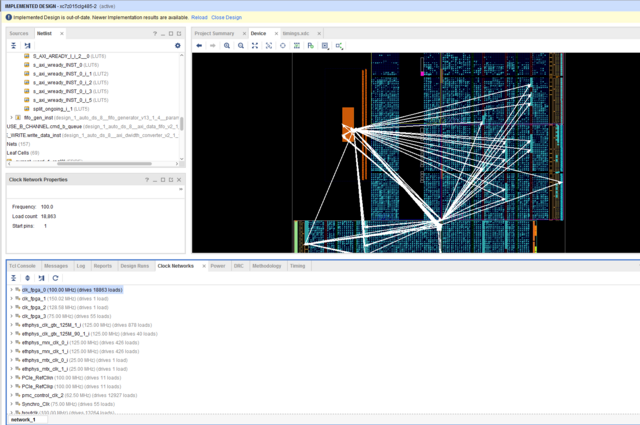

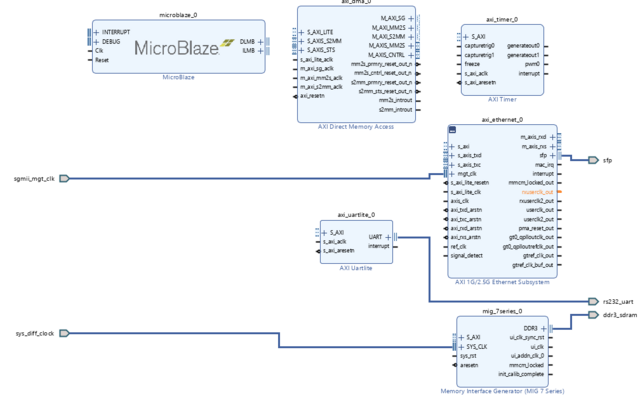

SFP проект в vivado

mixa7109 опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

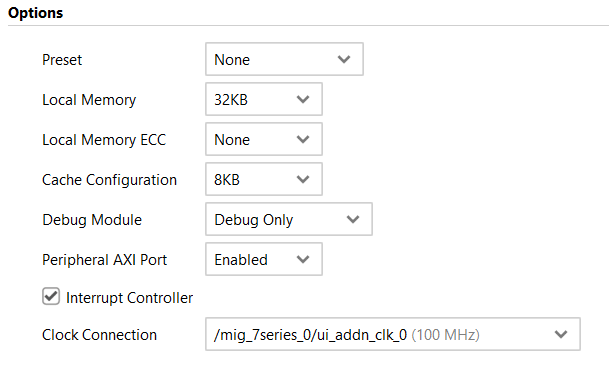

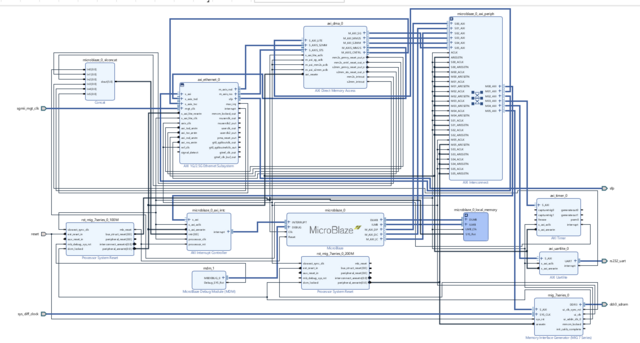

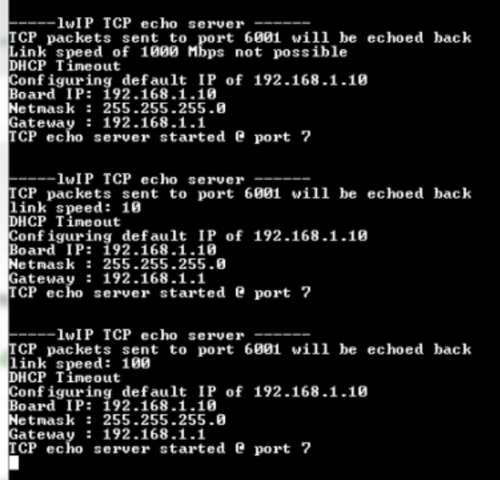

Всем добрый день, пытаюсь создать простой проект для работы с SFP и microblaze. Для microblaze используется прошивка: lwIP Echo Server. Проект учебный на отладочной плате Xilinx Kintex-7 FPGA KC705 Проектик делаю по этому гайду: https://numato.com/kb/gigabit-ethernet-example-design-using-vivado-for-mimas-a7-fpga-development-board/ Используются следующие модули: 1. MicroBlaze 2. AXI DMA 3. AXI 1G/2.5G Ethernet Subsystem 4. MIG 5. UART 6. Timer Все между собой соединяется, но на фото и не разберешь, слишком много соединений Все в сборке выглядит так: Все собирается, но сама прошивка не заводится. Даже в консоль ничего не выдается, я делал на другой платке обычный ethernet и там все работало. А ожидалось что-то типо такого: Но на выходе тишина. Причем, если запустить этот же проект, но с прошивкой на тест памяти, то все работает. Даже и не пойму, где может быть ошибка и что не так..... Проверял сами порты SFP через IBERT и тест был пройден. -

xilinx Xilinx улучшает доступ к своей документации

МакроГрупп опубликовал тема в Объявления пользователей

Компания AMD Xilinx реорганизовала доступ к технической документации, сделав его более удобным для пользователей. Теперь этот доступ осуществляется через единый портал https://docs.xilinx.com, на котором собраны все даташиты, а также имеется мощная система поиска с фильтрацией. Подробнее -

Всем привет. Много работал ранее с проектами в среде QUARTUS, очень часто приходилось отлаживать проекты в железе при помощи встроенного логического анализатора Signal Tap II. Очень удобный инструмент, ни один раз помогал мне найти и выявить ошибки, пропущенные на стадии моделирования и некоторые моменты, которые моделирование в принципе не способно обнаружить. В данный момент создаю проект в Xilinx Vivado, где на ПЛИС принимаю по JESD отчёты из АЦП, провожу некоторую обработку данных и кладу в память. Столкнулся с ситуацией, что на модели всё идеально, никаких проблем нет, но в железе не работает должным образом моя внутренняя логика (при этом приём сигнала с АЦП по JESD в норме). Стал разбираться, с помощью ядер ILA выводить интересующие меня сигналы JESD, флаги и статусы для анализа. Первая проблема, с которой я столкнулся, не могу завести ядра на частоте, которой изначально нет в ПЛИС (в момент подачи питания). Частота появляется с программируемого генератора позже и САПР Vivado говорит мне, что не может запустить ядро ILA и показать результаты... Пришлось перебрасывать все нужные мне сигналы через три регистра на стабильный клок (от DDR у меня есть 300МГц, которые всегда поступают в ПЛИС). ILA запускается, но тут начинается танец с бубном. У меня либо совсем умрёт JESD, что перестают корректно приниматься данные, либо работает но данные бьются. Причём бьются не те данные, которые я вывел на ILA, а реальные отчёты АЦП, поступающие в память. Лечится эта штука путём полного сброса проекта (команда "reset_project" TCL) и 1-2 перекомпиляции, не меняя исходников или настроек. В итоге этот процесс очень сильно стопорит процесс отладки. После каждых изменений в проекте, приходится танцевать с бубном и надеяться, что после 2-3 перекомпиляций проект получится рабочий, JESD запустится и ILA ему мешать не будет. Прошу помощи у более опытных пользователей. Как вы работаете с ILA? Как тестируете работоспособность проекта в железе на xilinx?

-

Компания Xilinx (вошедшая недавно в состав AMD) объявила, что устройства серии Versal HBM уже могут быть предоставлены участникам программы раннего доступа. Семейство Versal, выполненное по технологическим нормам 7 нм, представляет собой новейшие адаптивные вычислительные устройства, сочетающие в себе высокопроизводительные процессорные ядра ARM, программируемую логику, высокоскоростные трансиверы, внутрикристальную сеть и специализированные контроллеры. Подробнее

-

XDMA C2H

Drakonof опубликовал тема в Работаем с ПЛИС, области применения, выбор

Друзья, подскажите пожалуйста. Есть задача передавать данные с ПЛИС через pcie в ddr хоста, без запроса со стороны хоста. Т.е. иметь возможность записи данных из ПЛИСа напрямую в память хоста. Я правильно понимаю, что это делается с помощью xilinx'овского драйвера для xdma и передачу данных через канал c2h? -

Нужен xilinx 7 серии, pcie m.2 Acorn cle-215+, litefury, nitrefury и другие

-

- fpga

- fpga xilinx

-

(и ещё 2 )

C тегом:

-

Компания Xilinx выпустила две отладочные платы для серии систем на кристалле Versal – VMK180 и VCK190. Подробнее

-

На вебинаре будут показаны новые функции продукта, включая модели, программные инструменты и блоки обработки данных для глубокого обучения. Подробнее

-

amd AMD завершила сделку по приобретению Xilinx

МакроГрупп опубликовал тема в Объявления пользователей

Компания AMD объявила о завершении приобретения компании Xilinx в рамках сделки с полным пакетом акций. Приобретение, о котором первоначально было объявлено 27 октября 2020 года, создает лидера отрасли в области высокопроизводительных и адаптивных вычислений со значительно увеличенным масштабом деятельности и самым лучшим портфелем передовых вычислительных, графических и адаптивных продуктов (SoC). Подробнее -

Посетите этот веб-семинар, чтобы узнать, как создавать экономичные устройства с высокой пропускной способностью с на базе ПЛИС серии Artix UltraScale+, содержащей лучшие в своем классе приемопередатчики и самые высокие вычислительные возможности DSP для устройств с оптимизированной стоимостью. Подробнее

-

- ultrascale

- плис

-

(и ещё 2 )

C тегом:

-

fpga xilinx Релиз Vitis Al 2.0 от Xilinx

МакроГрупп опубликовал тема в Объявления пользователей

Xilinx обновил свою среду разработки приложений искусственного интеллекта Vitis AI. Теперь разработчикам доступна версия 2.0, которую можно скачать совершенно свободно с репозитория Xilinx по ссылке https://github.com/Xilinx/Vitis-AI Подробнее -

Компания Xilinx представила карту-ускоритель Alveo U55C и новый стандартизированный API, позволяющий развернуть программное обеспечение на целом кластере ПЛИС. Ускоритель Alveo U55C обеспечивает превосходную производительность на ватт для высокопроизводительных вычислений (HPC) и легко масштабируется с помощью кластерного решения Xilinx HPC. Подробнее

-

Организаторы проведут интерактивную сессию вопросов и ответов с менеджером по линейке продуктов и техническим экспертом – представителями Xilinx. Подробнее