Поиск

Показаны результаты для тегов 'ultrascale'.

-

Посетите этот веб-семинар, чтобы узнать, как создавать экономичные устройства с высокой пропускной способностью с на базе ПЛИС серии Artix UltraScale+, содержащей лучшие в своем классе приемопередатчики и самые высокие вычислительные возможности DSP для устройств с оптимизированной стоимостью. Подробнее

-

- ultrascale

- плис

-

(и ещё 2 )

C тегом:

-

В связи с моральным устареванием и сложившимся на рынке дефицитом ПЛИС серии Spartan-6, компания Xilinx рекомендует своим заказчикам переходить на более новые серии – Spartan-7, Artix-7 и Artix Ultrascale+ и предлагает принять участие в бесплатных вебинарах компаний-партнеров - Hardent и PLC2. Подробнее

-

Компания Макро Групп приглашает на вебинар по нейронным сетям разработчиков решений на платформах Xilinx и специалистов по искусственному интеллекту и нейросетям. На вебинаре вы узнаете, какие шаги необходимо выполнить для запуска собственной сверточной нейросети на платформе Xilinx Zynq Ultrascale+, и увидите её работу на отладочной платформе Xilinx ZCU104. Узнаете, как это сделать и на других платформах Xilinx. Зарегистрироваться

-

- zynq

- ultrascale

-

(и ещё 4 )

C тегом:

-

В данном вебинаре вы подробно познакомитесь с данными модулями, узнаете о сферах и особенностях их применения, а также увидите наглядную демонстрацию запуска ПО на данной платформе. Программа вебинара: Введение Что такое SoM-модули Kria? Магазин готовых приложений Сравнение модулей Kria K26 и Jetson TX2 Первая в мире несущая плата для SDR на основе KRIA Пример запуска приложений из магазина Xilinx Итоги, выводы и ответы на вопросы Подробнее

-

вебинар Вебинар Xilinx по Artix Ultrascale+

МакроГрупп опубликовал тема в Объявления пользователей

Регистрируйтесь на бесплатный вебинар Xilinx, на котором будет рассказано о недавно анонсированном расширении линейки Ultrascale+ для бюджетного сегмента широкого спектра интеллектуальных периферийных решений. Подробности -

Компания Xilinx объявила о существенном расширении линейки своих 16 нм устройств UltraScale+ - Artix UltraScale+. Подробнее...

-

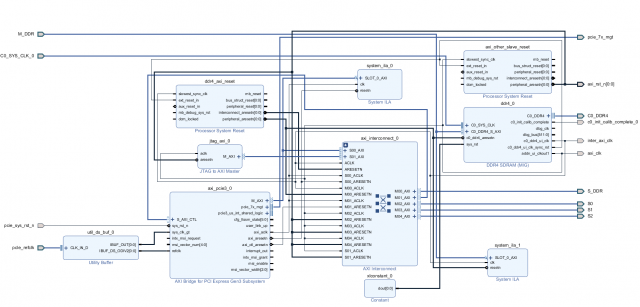

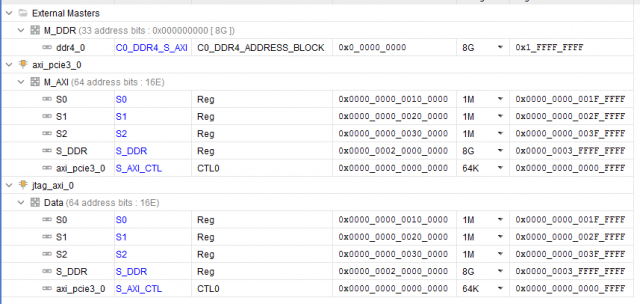

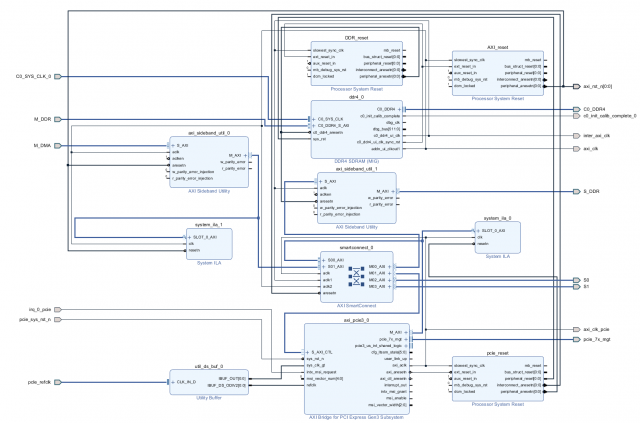

Добрый день. Долго работал с Intel (Altera) бед не знал в среде Quartus и вот пришлось перейти (к глубокому сожалению) на работу с Xilinx... Сразу был разочарован, многое из того, что доведено до автоматизма у Intel тут нужно делать самому, вникая в низкоуровневые тонкости. Очень большие ограничения на использования ip-ядер (плюс скудный набор изменяемых параметров) и плохие тайминги заводят меня в тупик. Так вот, какова суть проблемы. Работаю с Kintex Ultrascale. Понадобилось собрать систему из ядра PCIe -> interconnect ->DDR4. Прочитал кучу мануалов (PG194 v3.0, PG059 и тд.., Ответы с форумов, Видео пример настройки, Вивадовские примеры). В общем собрал систему похожую на систему из примеров. Рис. 1 Тут добавил ещё Jtag консоль для удобства отладки (в дальнейшем необходимо заменить её на свой блок ДМА), вывел интерфейсы для своих слейвов наружу. ДДР тоже вывел наружу (как S_DDR) на верхнем уровне закольцевал и вернул обратно (как M_DDR, опять же дикость связанная с XILINX пришлось решать одну из его проблем таким образом). Повесил ещё пару ИЛА для отладки и отображения шины АXI. Назначил адресные пространства. Рис. 2 Вроде всё задышало. Но с большими слеками на интерконнекте... То PCIe сама развестись не может, то на ядре ДДР какие то проблемы по таймингам. В общем всё плохо, но как то работает. По PCIe есть доступ и к DDR и к регистрам в слейвах, вроде всё корректно. Начинаю работать через Jtag консоль (в дальнейшем её нужно заменить своим блоком ДМА) и всё, ДДР не читается не пишется, комп умирает, интерконнект виснет. Проблема только при обращении к ДДР, при работе с моими слейвами регистровыми проблем нет, данные корректно пишутся и читаются. Залез по ИЛА и увидел что от ДДР не доходит сигнал BVALID и BID через интерконнект. Собственно из ДДР он вышел, но через интерконнект до второго мастера он не приходит, а для первого без проблем, всегда всё хорошо. Окей, меняю местами Jtag и PCIe та же шляпа. Jtag работает корректно, до PCIe не доходит BVALID и BID. Получается что второму мастеру по счёту просто не даётся доступ к ДДР. Листал форумы, читал советы, нашёл. Говорят что на Ultrascale и Ultrascale+ стандартный интерконнект не работает корректно, нужно ставить некий "SMARTCONNECT"... Ну окей.. читаю документацию, разбираюсь, вставляю смартконнект.. А у него оказывается выкидывает все ID(r/w/b) на шине AXI. Чтобы ID не выкидывались, ставьте "axi sideband" (говорит XILINX) до и после интерконнекта на каждой шине.. окей, поставил. Спустя все эти манипуляции я получил рабочую схему, которая может работать с двумя мастерами и без проблем читать и писать в ДДР. Рис. 3 Но эта штука разводится очень плохо. Сложность в том, что у AXI PCIe максимальная частота 250МГц, у ДДР в моём режиме (1200МГц частота памяти) AXI DDR 300МГц. Слейвы свои на такой частоте я не потяну, иначе вообще всё по таймингам умрёт... пришлось ставить в 2 раза меньше. Поставил 150МГц на слейвах. В итоге интерконнект городит очень сложную структуру из ядер клоковых конвертеров, конвертеров данных, протоколов и тд.. А потом при имплементации на эти же ядра и ругается Вивадо. Долго бьюсь над этой проблемой, не могу нормально побороть слеки. Пришлось понизить частоту ДДР до 1000МГц, соответственно AXI DDR стала 250Мгц, а частота моих слейвов 125 МГц. Слеки явно улучшились, работать можно, но проблема совсем не ушла. Как мне правильно настроить систему, чтобы не было конфликтов между ядер XILINX и всё нормально разводилось при требуемых параметрах?

- 17 ответов

-

- xilinx

- ultrascale

-

(и ещё 4 )

C тегом:

-

Проблемы с PCIE3.0 Tandem у KCU105

g700 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! Возникла проблема в конфигурации FPGA в режиме PCIE3.0 Tandem у отладочной платы KCU105. В проекте есть светодиод (led 0 на плате), который при второй стадии загрузки (по PCIE3.0) должен включатся. Порядок действий: Собираю проект design example. Констрейны для bitstream: После сборки генерирую MCS командой: Прошиваю конфигурационную память скриптом который есть в архиве program_spi.tcl Выключаю хост. Потом включаю. После загрузки вижу девайс: Читаю регисры с помощью mcap версия bitstream совпадает с ожидаемой. Прошиваю второй стадией: Поле прошивки ядро выдает сообщеие: После этого светодиод не горит, а mcap говорит: А если прошить FPGA по JTAG первой стадией, затем сделать reboot и прошить mcap воторой стадией, то светодиод горит и сообщения в ядре по irq нет. Данное IRQ принадлежит: Память конфигурационная память прошивается, через JTAG бластер по разъему J3. Версии: Vivado v2019.1 (64-bit) Хост в котором карточка Linux 4.9.0-8-amd64 #1 SMP Debian 4.9.130-2 (2018-10-27) x86_64 GNU/Linux Утилиты MCAP взята отсюда https://www.xilinx.com/support/answers/64761.html Ревизия KCU105 C Версия pci-utils pciutils-3.3.1 пробовал и с 3.6.3 одинаковый результат. В чем может быть проблема? pcie3_ultrascale_0_ex.zip -

Приветствую! Хотелось бы собрать в одном месте информацию по техникам борьбы с неразводимостью проекта в Vivado, Есть конкретный кейс, большой проект на VU13P специфика которого в том, что ядра, которые реализованы пересекаются друг с другом (например одно ядро использует 90% из всех DSP на конкретном SLR, а другое - 80% RAM SLR, а третье - половину всех LUT SLR). Репорт о роутинге: степень утилизации: Собственно репорт рекомендует попробовать: report_design_analysis -congestion report_design_analysis -complexity и штудировать UG906 report_design_analysis -complexity: report_design_analysis -congestion: Какие выводы из этого всего напрашиваются: 1. Отключение LUT combining (если допустимо) 2. Использование ограничений по -max_fanout 3. opt_design -directive ExploreArea 4. place_design -directive AltSpreadLogic_medium или place_design -directive AltSpreadLogic_high 5. route_design -directive AlternateCLBRouting 6. phys_opt_design -directive AggressiveExplore (под вопросом) 7. Понижение частоты дизайна (если возможно) Итого, с помощью некоторых из приведенных способов удалось число пересечений свести от восьми к двум, поэтому интересно дополнить этот список, чтобы продолжить эксперименты. что еще можно попробовать? ------------------------ upd: 8. Синтезировать с оверконстрейном по частоте и ретаймингом (но поскольку это не ASIC, то работает только в определенном диапазоне частот), а разводить на фактической частоте.

- 18 ответов