Поиск

Показаны результаты для тегов 'timequest'.

-

Максимальная частота тактирования

Manvel опубликовал тема в Языки проектирования на ПЛИС (FPGA)

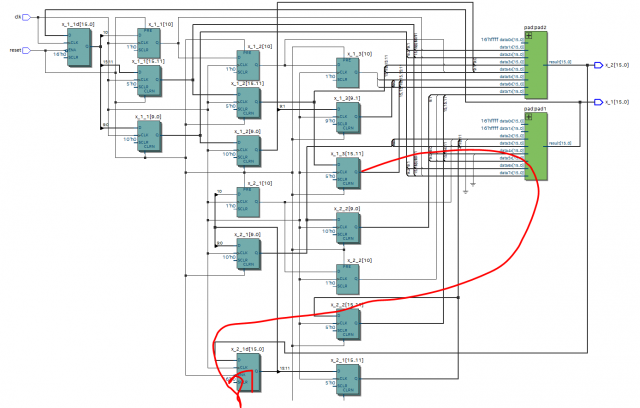

Здравствуйте, уважаемые товарищи! Эти вопросы я задавал на форуме интела но исчерпывающих для себя ответов не получил (https://community.intel.com/t5/FPGA-SoC-And-CPLD-Boards-And/Parallel-sum-frequency/m-p/1286075#M19982), поэтому решил повторить вопросы на данном форуме. И так, у меня есть задача смоделировать хаотическую систему, которая по сути из себя представляет 2 цифровых БИХ фильтра с нелинейным элементом в обратной связи. В процессе ознакомления с Verilog и с Quartus я решил, что высокой скорости можно добиться при использовании для этой задачи мегафункции от Квартуса - Parallel sum. В целом, на том железе, что у меня сейчас есть в распоряжении (DE10-lite и ice40-dac) все нормально работает на частотах тактирования 100 МГц, но имеется необходимость поднять частоты. На форуме интела мне подсказали, что надо задавать временные ограничения. Я прочитал немножко литературы (в частности https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-timing-analyzer.pdf) и у меня возникли вопросы. 1. Нужно ли задавать дополнительные временные ограничения для синхронной логики, кроме ограничений на частоту клока, например "set_max_delay -from [get_registers {x_1_3*}] -to [get_registers x_2_1d*] X ns"? Когда я задаю эти дополнительные ограничения, это почти никак не влияет на скорость собранного проекта, может эти ограничения надо задавать по другому? 2. Второй вопрос относится к быстрой и медленной модели проекта в Таймквесте. Для медленной модели Таймквест оценивает максимальную частоту около 200 МГц при этом для быстрой модели частота достигается до 340 МГц, что как бы разница существенная. По их документам (https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/wp/wp-01139-timing-model.pdf) не понятно, скорость быстрой модели больше зависит от напряжения подаваемого на кристалл или от качества кристалла, эти два параметра занесены под одну модель, а железа на такие скорости пока не имеются для экспериментальной проверки, ну и покупка железа будет зависеть именно от возможных максимальных частот.- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

Начну с основной проблемы. Потребовалось выполнить несколько операций ЦОС на ПЛИС. Разобравшись с языками описания цифровых схем были созданы три модуля: для БПФ, для взаимной корреляции сигнала и ещё один математический. По отдельности они проходили проверку работоспособности в железе на столе, но иногда всё разваливалось: бывали неудачные случаи разводки и результаты были неадекватные. После объединения всех трёх модулей в один проект работоспособная прошивка и вовсе перестала получаться. Почитав форумы и статьи понял, что может помочь задание временных ограничений на пути прохождения сигнала. (Например: "Если временные требования не заданы, то компилятор не производит оптимизацию задержек и они имеют произвольные значения и большой разброс." Источник: Lab1.pdf (spbstu.ru)) Я начал заниматься описанием временных ограничений, вижу на Chip Planer, что пути меняются, но какие-либо выводы по этому сделать не могу. Поэтому хотелось бы получить совет от тех, кто уже этим успешно занимался. Правильно ли вычислена ошибка? В верном ли направлении двигаюсь? Правильно ли мной описаны временные задержки блока БПФ: я описал прохождение сигнала из входной памяти (FFT:inst2, FFT:inst4 проекта) на бабочку (FFT:inst23), с результата вычисления бабочки до буферной памяти (FFT:inst21, FFT:inst22) и из буферной памяти до входа в бабочку при условии, что выполнение бабочки и установка адресов памяти выполняется не дольше, чем за 80 нс? Весь проект для Quartus II 13.0.1: MainDD3.zip — RGhost — файлообменник Ниже прикреплён файл временных ограничений sdc. P.S. Разработка ведётся под ПЛИС 5578ТС024. Для её конфигурирования используется прилагающееся к ПЛИС ПО и список цепей vqm из Quartus. Собственное ПО ПЛИС – одна из причин почему не использовалась мегафункция БПФ. Также для одного и того же списка цепей ПО может выдать как работоспособную прошивку, так и нет. В ПО есть возможность подгрузки файла временных ограничений, но тоже со своими особенностями. Если кто-то может и имеет желание помочь разобраться в этом, то оставьте контакт в телеграмм. MainDD3.sdc

-

Здравствуйте все! Есть FIFO с разными тактами на входе и на выходе, сделано в Quartus из мегафункции dcfifo. Скажите, пожалуйста, как правильно описать для него ограничения в файле sdc? Я почитал FIFO Intel® FPGA IP User Guide, раздел DCFIFO Timing Constraint Setting, но не понял, к сожалению. Или подскажите, пожалуйста, что почитать. Заранее признателен.

-

DVI и TimeQuest

rash230691 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

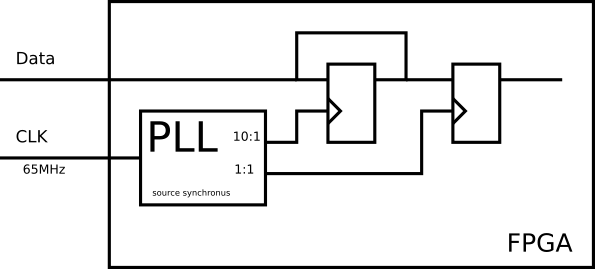

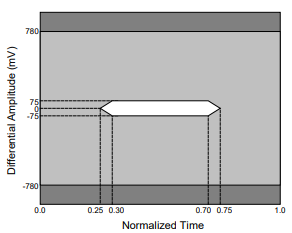

Доброго всем! Имеется плата с кривым разводом DVI и как следствие кривым приемом данных по этому самому DVI. Решил поправить данную ситуацию с помощью TimeQuest, но, скорее всего из-за малого опыта, у меня это не удалось. Схема всего этого безобразия во вложении, вкратце поясню: данные со скоростью 650 Mbps поступают в сдвиговый регистр 1:10, далее уходят на пиксельной частоте в обработку PLL имеет тип source synchronous, умножает входную частоту на 20, первый выход делит на 2, второй на 20 имеется простой блок подстройки фаз PLL, который ориентируется на входные данные Все что я знаю о источнике сигналов - глазковая диаграмма из спецификации на интерфейс(во вложении, диаграмма нормализованная) Имея сей стартовый набор данных, я набросал ограничений: Описал входную частоту Описал виртуальную частоту со сдвигом 180 градусов(center aligned) Объединил их в одну группу Задал задержки относительного виртуальной частоты Собственно к чему все это... Просьба "оценить" написанные ограничения, да и от советов по приему и десериализации данных сигналов не откажусь -

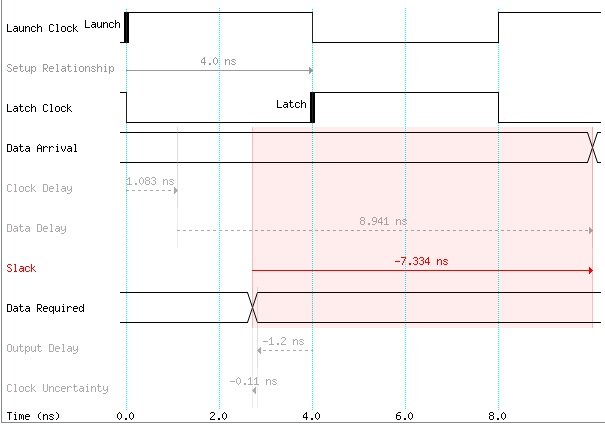

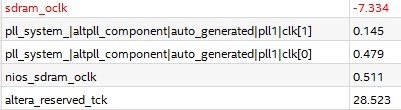

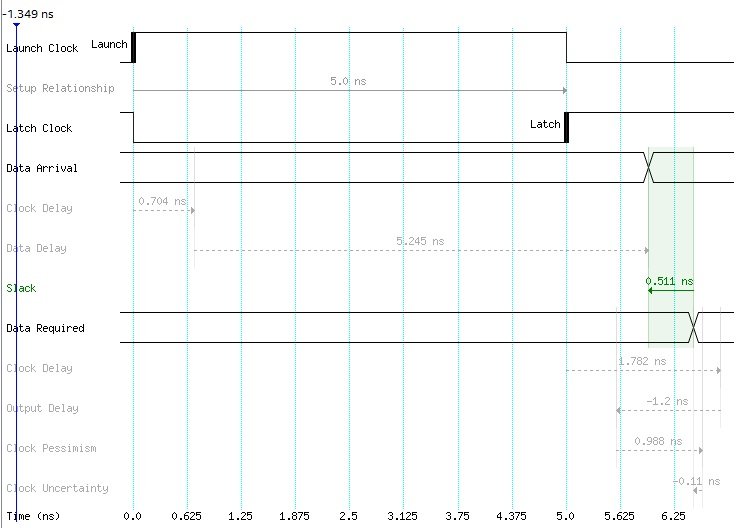

Здравствуйте, пишу свой первый проект на ПЛИС (verilog, max10), проект создаю в учебных целях. Создал систему в Qsys: nios, память(sdram), Jtag, и самописный компонент. Внутри самописного компонента, с просторов интернета контроллер памяти sdram(отдельно от памяти nios), счетчик и DCFIFO для передачи из счетчика на sdram. Nios запускает счетчик, тот в считает до оперделенного числа, и записывает в FIFO, оттуда контроллер sdram забирает данные и пишет в память. Nios и счетчик работают на 100Мгц, sdram и память на 125Мгц, FIFO двухклоковое на запись 100 Мгц на чтение 125 Мгц. На симуляции все работает отлично но в железе появляются проблемы констрейнов. В assigment поставил sdram выводам fast IO, клоки сделал Global Clock. Sdram для Nios работет timequest не ругается, а в моем компоненте постоянно ошибки памяти и я не могу понять почему такие большие слаки. Память микрон MT48LC16M16A2. На nios память микрон MT48LC4M32B2. Констрейны nios sdram Констрейны контроллера Общая картина: Клок Nios sdram Sdram внутри компонента. Не могу понять причину почему sdram внутри моего компонента так отличается от sdram используемого nios. Уже 2 недели бьюсь, может кто-то подскажет? Исходник компонента прилагаю. src.sv