Поиск

Показаны результаты для тегов 'system verilog'.

-

Использование UVM

AntonB опубликовал тема в Методы и средства верификации ПЛИС/ASIC

Посоветуйте материал для изучения UVM ?- 27 ответов

-

- fpga

- verification

-

(и ещё 1 )

C тегом:

-

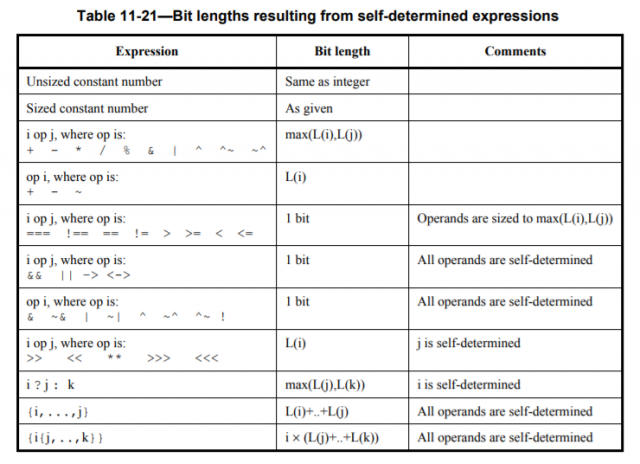

Здравствуйте, коллеги! Предпочитаю в выражениях явно приводить размерность вектора к необходимой разрядности, однако появилась потребность разобраться с приведением разрядности по стандарту. Есть непонятный момент, нужна помощь.. Изучаю этот вариант стандарта IEEE_Std_1800-2012 SystemVerilog(для верилога написано то же самое) : IEEE_Std_1800-2012 SystemVerilog.pdf Разрядность векторов саомоопеределённом выражении вычисляется согласно таблице 11-21 на странице 248: Однако есть и контекстно-определённые выражения. Примеры из документа: logic [15:0] a, b; // 16-bit variables logic [15:0] sumA; // 16-bit variable logic [16:0] sumB; // 17-bit variable sumA = a + b; // expression evaluates using 16 bits sumB = a + b; // expression evaluates using 17 bits Здесь всё понятно - учитывается разрядность вектора слева от оператора " = " Далее они приводят пример, где суммирование с числом 0(int = 32bit) расширяет контекст всего выражения и не допускает потери информации при выполнении первого оператора " + ": answer = (a + b + 0) >> 1; // will work correctly Отсюда я делаю вывод, что контекстом является всё выражение, а не только то, что стоит слева от оператора " = ". Т.е. при выполнении первого оператора " + " a и b уже будут расширены до 32 бит. Пока что тоже всё логично. А вот далее следует непонятное.. logic [3:0] a; logic [5:0] b; logic [15:0] c; c = {a**b}; // expression a**b is self-determined, 4 bits c = a**b; // expression size is determined by c, 16 bits Почему конкатенация не учитывает контекст, а возведение в степень - учитывает? Ведь и тот, и другой оператор присутствуют в приведенной выше таблице самооперделённых выражений. И будет ли учитывать контекст, к примеру, оператор " << " ? logic [3:0] a; logic [15:0] c; c = a << 1; // expression size is ? Почему разработчики не разделили таблицу на 2: операторы, учитывающие контекст, и игнорирующие его? Благодарю за помощь!

-

Компания Syntacore, разработчик микропроцессорного IP, ищет сотрудника на позицию RTL Designer. Обязанности: Разработка и верификация сложных функциональных модулей для ASIC на Verilog/System Verilog. Требования: Опыт разработки и верификации RTL для ASIC от 3 лет; Отличное знание Verilog/System Verilog; Опыт использования RTL симулятора от 3 лет (any vendor); Знакомство с архитектурой современных процессоров, знание современных SoC интерфейсов (ACE, AXI); Уверенный пользователь Linux; Знание английского языка на уровне чтения технической документации и умения вести переписку на технические темы; Опыт работы с системами контроля версий. Мы предлагаем: Высокую оплату труда (по результатам собеседования); Оформление по ТК РФ; Интересную и перспективную работу, возможность быстрого профессионального и карьерного роста; Гибкий рабочий график; ДМС, оплачиваемый отпуск и больничный; Возможность публикаций и поездок на конференции. Контактная информация: [email protected] Дарья Также другие вакансии компании можно посмотреть на сайте https://spb.hh.ru/employer/2132324