Поиск

Показаны результаты для тегов 'rom'.

-

Здравствуйте. С недавнего времени осваиваю разработку проектов под ПЛИС для семейства ProASIC3E (ранее имел дело только с Altera и Xilinx) и столкнулся с проблемой нехватки информации и технической поддержке. В моем проекте имеется два процессорных ядра каждое из которых имеет память ROM 4096x32 инструкций. В результате разводки выдается ошибка: Error: [fail_to_route]: Router fails. Shorts = 6407. Open nets = 0. Я подозреваю, что не хватает каких то ресурсов. Где посмотреть что это значит? Синтез проекта проходит нормально: Core Cells : 46826 of 75264 (62%) IO Cells : 46 RAM/ROM Usage Summary Block Rams : 79 of 112 (70%) Скажите пожалуйста можно ли в семействе ProASIC3E реализовать память типа ROM на встроенный блоках памяти (RAM) по аналогии как в ПЛИС Altera? Директива синтезатора Synplify Pro: synthesis syn_romstyle = "lsram" — не дает результата (память реализуется на логический элементах). Пример: module rom1(clk, addr, q)/* synthesis syn_romstyle = "lsram" */; input clk; input [11:0] addr; output [31:0] q; reg [31:0] m; reg [31:0] q; always @(posedge clk) begin q[31:0] <= m[31:0]; end always @(*) begin case (addr[11:0]) 12'h000 : m[31:0] = 32'hA0FC0000; 12'h001 : m[31:0] = 32'hA0FE0000; 12'h002 : m[31:0] = 32'hA0FD0000; 12'h003 : m[31:0] = 32'h04FF0000; 12'h004 : m[31:0] = 32'h00000100; 12'h005 : m[31:0] = 32'h6BFCFCFC; ... Синтезатор понимает, что это ROM: @N: MO106 :"f:\project\microsemi\core\hdl\rom1.v":19:1:19:4|Found ROM .delname. (in view: work.rom1(verilog)) with 4096 words by 32 bits. Заранее благодарен за любую оказанную помощь в моей проблеме.

-

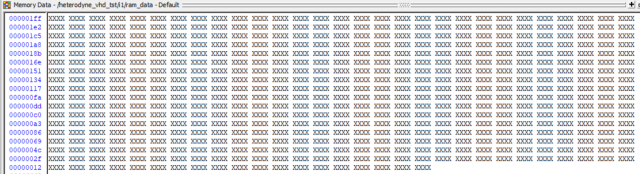

Всем привет! Следующая проблема, я пытаюсь инициализировать память с помощью атрибутов: type memory is array (511 downto 0) of std_logic_vector (15 downto 0); signal ram_data: memory; attribute ram_init_file : string; attribute ram_init_file of ram_data : signal is "mem.mif"; Он синтезирует память со следующими параметрами: Info (12133): Instantiated megafunction "altsyncram:ram_data_rtl_0" with the following parameter: Info (12134): Parameter "OPERATION_MODE" = "ROM" Info (12134): Parameter "WIDTH_A" = "16" Info (12134): Parameter "WIDTHAD_A" = "9" Info (12134): Parameter "NUMWORDS_A" = "512" Info (12134): Parameter "OUTDATA_REG_A" = "UNREGISTERED" Info (12134): Parameter "ADDRESS_ACLR_A" = "NONE" Info (12134): Parameter "OUTDATA_ACLR_A" = "NONE" Info (12134): Parameter "INDATA_ACLR_A" = "NONE" Info (12134): Parameter "WRCONTROL_ACLR_A" = "NONE" Info (12134): Parameter "INIT_FILE" = "mem.mif" И все было было бы хорошо, но в ModelSim вижу следующее: Если задать память через мегафункции и там прописать файл инициализации, то все хорошо, но мне надо научиться через атрибуты. В чем проблемы? Вот все библиотеки: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; use ieee.math_real.all; LIBRARY altera_mf; USE altera_mf.altera_mf_components.all; library altera; use altera.altera_syn_attributes.all;