Поиск

Показаны результаты для тегов 'refclk'.

-

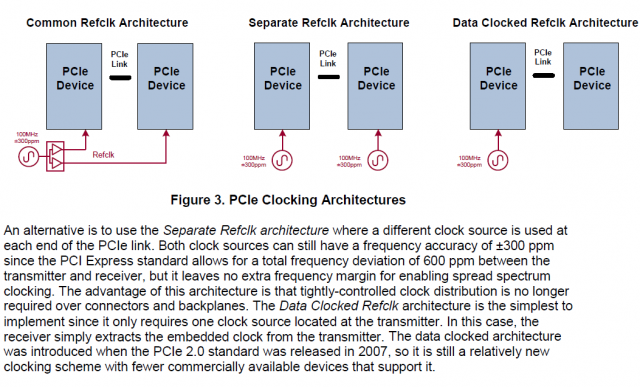

Вопрос не в том, можно ли так по правилам (читай - стандартам), а в том - можно ли от них и насколько отходить. Итак: дифференциальный RefClk частотой 100МГц надо заводить на каждый PCI-E target, основная цель, я так понимаю - чтобы у мультигигабитных трансиверов был исходный клок с одним и тем же дрейфом. Вопрос: а можно ли не заводить, а генерить локально? в сети разные мнения, от Note that the pcie bus ref clock needs to be common between all devices communicating on the pcie bus. До https://www.xilinx.com/support/answers/18329.html с техникой Asynchronous Clocking Также есть такая вот картинка: которая вроде бы говорит, что такое вроде как приемлемо, но хотелось бы ответа практиков. Зачем это всё? Есть девборда с Xilinx US/US+ c FMC но без PCI-E слота, сейчас появилась необходимость работать с PCI-E самая простая и материально незатратная идея реализовать это: изготовить райзер из FMC в PCI-E (через тот же USB3.0 кабель, которй используется китайцами повсеместно для выноса с материнки PCI-E 1х ). Но вот незадача - на FMC разведены мультигигабитные трансиверы, но задающий клок для них распаян локально на плате (номинал может программироваться во внешней фапч), резать дорожки, куда-то там подпаиваться - такой кейс совсем исключён. Поэтому для принятия решения о райзере хотелось бы заручиться уверенностью что заработает хотя бы в лабораторных условиях (в продакшене это использоваться не будет). (лабораторных условиях == температура 25С, что должно снизить разбос задающих частот на разных концах MGT)/ PCIe-Clock-Source-Selection.pdf