Поиск

Показаны результаты для тегов 'protel'.

-

Экспорт печатной платы в старую версию

repstosw опубликовал тема в Altium Designer, DXP, Protel

Здравствуйте! Столкнулся с таким фактом. Есть файл печатной платы, выполненный предположительно в DXP Protel старшей версии. Сконвертировал его в формат 5-й версии. Открыл Altium Designer'ом 6-й версии. Далее взял оттуда футпринт одной компоненты (состоит из одних падов TOP слое). Нарисовал УГО и отремапил его на этот футпринт. В итоге: связи между этим элементом есть, но они становятся видны только при перетаскивании элемента. Также при печати рисунка платы, принтер не распечатывает футпринт, но на чертеже он есть. Решил проблему удалением проблемного футпринта и его ручным перерисовыванием. Кто сталкивался, можете подсказать в чём может быть дело? Складывется впечатление, что футпринт оказался в "теневом бане" у САПР. -

Нештатная ситуация, Altium Designer

repstosw опубликовал тема в Altium Designer, DXP, Protel

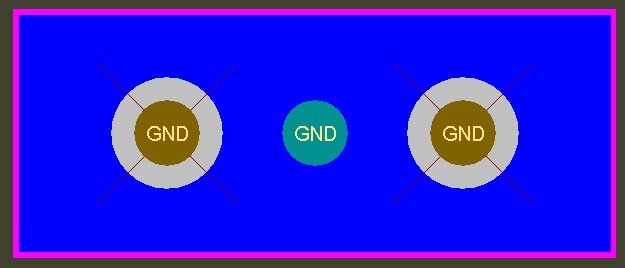

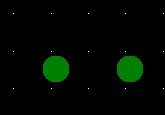

Добрый день. Столкнулся с нештатной ситуацией в Altium Designer. Создал прямоугольную контактную площадку с отверстием по центру на GND. И по бокам продублировал VIA на GND для уменьшения спопротивления контакта с плоскостью земли. Почему-то не произошло сцепление с плоскостью земли GND центрального отверстия (нет крестика). По краям всё нормально. Внутренние плоскости вышли такими: Как видно из рисунка - отверстие отсутствует по центру, что ненормально. И в заключение, гербер-файлы внутренних слоёв. Плоскость питания: Плоскость земли GND: В итоге получил платы с коротким замыканием между двумя внутренними плоскостями - как раз в этом центральном отверстии!!! Хорошо, что во-время заметил. Лечение: рассверливание центрального отверстия с целью разомкнуть плоскости GND и Vcc. Распилил ножёвкой пару плат для локализации ошибки - с целью поиска VIA с коротким замыканием :) Методом деления пополам и отсева исправной части с последующим распиливанием ошибочной части. и т.п. И всё-же, кто виноват - кто рисовал плату или Altium Designer? Проверка правил в PCBDoc успешна и без предупреждений. Ошибка возникает при экспорте в гербер - из-за инверсного представления информации на внутренних плоскостях (пятаки изоляции вместо проводящих участков).