Поиск

Показаны результаты для тегов 'phy'.

-

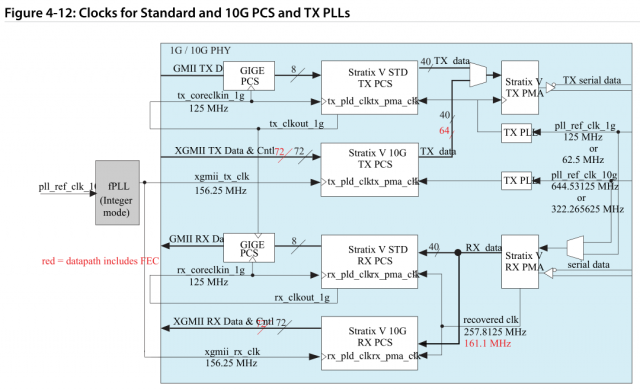

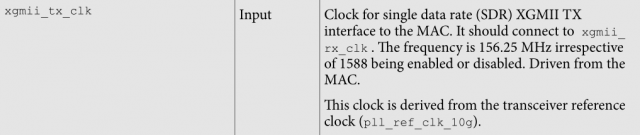

Всем привет. В очередной раз борюсь с настройкой PHY трансиверов фирмы Intel. На этот раз не могу разобраться с тактированием Backplane Ethernet 10GBASE-KR в конфигурации 10G с LinkTraining и включенным FEC. Мегафункция предлагает мне всего 4 порта с частотами: pll_ref_clk_10g - входной порт. Тут вроде все понятно, референсный клок для CMU/ATX PLL rx_recovered_clk - выходной порт. Восстановленный с помощью CDR клок из входного потока (согласно мануалу равен 257.8125 МГц вероятно потому что PMA уровень оперирует 40 битами, а не 66). И два входных порта: xgmii_tx_clk и xgmii_rx_clk. Собственно вопрос как раз про них, чем я должен запитать эти два порта? rx_recovered_clk не подходит поскольку xgmii_tx_dc принимает 64 бита данных, и соответственно частота должна быть 156,25 МГц. Пытался с помощью обычной PLL сгенерировать 156,25 МГц и запитать эти порты, результат – куча слаков между частотой PLL и внутренней частотой PHY clk33pcs. Мануалы предлагают схемы по которым сложно что-то понять: Описание порта xgmii_tx_clk и xgmii_rx_clk одинаковое и противоречивое: Архива с примером проекта на wiki Intel не нашел (страница есть - файлов нет). Может у кого-нибудь есть примеры с этой PHY или хотя бы какие-то мысли. Буду благодарен.

-

RGMII2 процессора MT7621

telecom21 опубликовал тема в Интерфейсы

Добрый день! Никто не сталкивался с процессором MT7621 Mediatek? Проблема в том, что в имеющейся скудной документации на процессор нет нормальной структрной схемы с внешним интерфейсом RGMII2, а так же полной таблицы регистров для управления RGMII2. Ни как не могу запустить данный интрефейс для связи с внешней PHY. -

AR8033 1000Base-X

telecom21 опубликовал тема в Интерфейсы

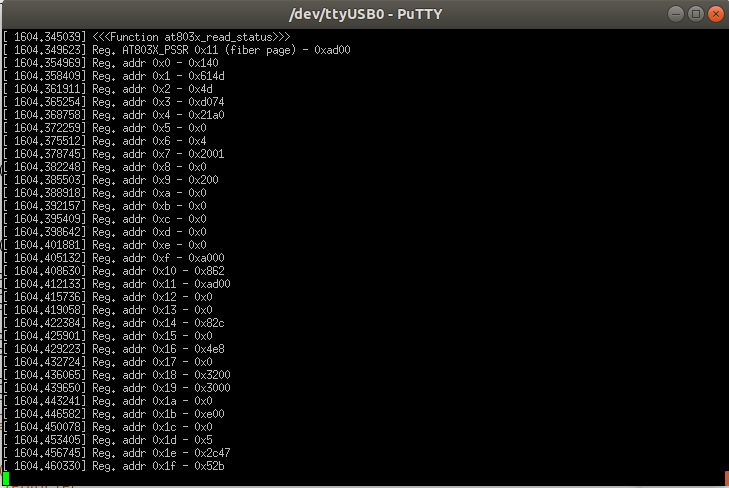

Добрый день! Нужна помощь, не могу запустить микросхему PHY AR8033 в режиме 1000BASE-X. Микросхема на плате включена в режиме 1011 "Copper/fiber auto-detection, RGMII". Соответсвенно на плате выведены два разъема: под медный провод и кроватка под SFP модуль. Когда к микросхеме не подключен ни медный провод, ни SFP модуль, регистр конфигурации (по адресу 0x1F) возвращает значение 0x81BB. При подключении медного провода, значение регистра конфигурации меняется на 0x810B и микросхема начинает работать в соответствующем режиме. Подключение SFP модуля не меняет значение регистра конфигурации - остается 0x81BB (а должно быть 0x812B), то есть микросхема не определяет подключение по оптике. Соответственно, нет и пинга в канале. В качестве SFP модуля используем GigaLight GP-3124-02C. После того как в драйвере отключил AUTO-NEGOTIATION бит 12 в регистре Control Register 0x00 (fiber page) микросхема начала определять подключение по SFP. Регистр Chip configure register по адресу 0x1F возвращает значение 0x52B. Так же загораются LED_ACT и LED_1000 при подключении канала. Но "пинги" не идут и подключенный к моей плате по оптике прибор не видит канала. Скриншот с дампом регистров: Судя по документации когда отключаешь AUTO-NEGOTIATION, микросхема переходит в режим 100BASE-FX. Видимо из за этого канал не запускается. Попробовал так же вручную в драйвере перевести чип в режим работы BX1000_RGMII_50 путем записи в регистр 0x1F. Оставил включенным AUTO-NEGOTIATION. В таком режиме и LED_ACT, и LED_1000 не горят. Канал так же не поднимается. Скриншот с дампом регистров: Кто то сталкивался уже с подобной проблемой? Очень жду помощи!!!