Поиск

Показаны результаты для тегов 'ip core'.

-

И снова кастомизация IPcore в Vivado

OparinVD опубликовал тема в Среды разработки - обсуждаем САПРы

Приветствую всех! Давно я кручусь вокруг этой темы, много раз возвращался к похожим веткам на форуме, перечитал мануалы от Xilinx, но не дается оно мне. Есть ощущение, что не хватает легкого волшебного пендаля, чтоб всё встало на свои места, и чтоб над головой лампочка, как в мультике, загорелась. Что я хочу получить: Хочу навести красоту, наподобие стандартных корок - чтоб жмешь разные галочки в GUI, и в зависимости от этого подключались разные HDL-ные или IPcore-ные внутренности, и менялось, например количество внешних портов. Что умею на данные момент: 1) Могу накидать форму для GUI в IP packager'е - тут всё интуитивно понятно. Могу играть с Enablement dependency, включая/выключая порт. Вижу сгенерированный tcl-скрипт для GUI с функциями proc update_PARAM_VALUE... и proc validate_PARAM_VALUE... 2) Независимо от этого могу на основе Export Block Design создать свой скриптик, который будет с учетом внешних условностей делать create_cell'ы и соединять их connect_net'ами. Не могу понять, как мне скрестить первый и второй пункты. Сейчас у меня GUI - просто пустышка, а скрипт могу запустить только вручную, например, для восстановления проекта из git. По всей вероятности всё должно работать автоматически: кинул Ipcore на канвас, изменил параметры - запустился скрипт, который подтянул нужные исходники, создал топ-левел и т.д. Запустил валидацию BD, пошла пропаганда параметров - опять запустился тот же скрипт. Как этого добиться?- 27 ответов

-

- customization parameters

- tcl

-

(и ещё 2 )

C тегом:

-

Gowin IP-Core RAM module

IgorMov опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всех приветствую. Может кто-нибудь подскажет, как корректно создать простой блок памяти 8 адресов, 8 бит данных в Gowin? GOWIN FPGA Designer Version 1.9.8.05 build(57076). _Tools > IP Core Generator > Memory > Block Memory > SP 1.0 Address Depth:8 Data Width: 8 Получается //--------Copy here to design-------- test_RAM_ad8b_d8b your_instance_name( .dout(dout_o), //output [7:0] dout .clk(clk_i), //input clk .oce(oce_i), //input oce .ce(ce_i), //input ce .reset(reset_i), //input reset .wre(wre_i), //input wre .ad(ad_i), //input [2:0] ad .din(din_i) //input [7:0] din ); //--------Copy end------------------- Почему " .ad(ad_i), //input [2:0] ad" , а не [7:0] ? Вроде, 1 блок памяти 18Kb... -

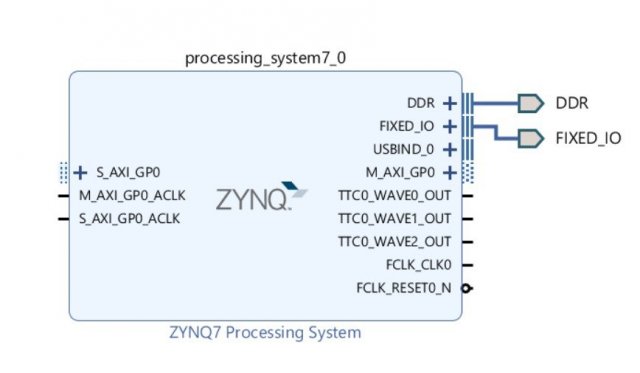

Я написал функцию "memcpy" для копирования блока данных с исходного адреса на адрес назначения. Хочу протестировать на плате (Zynq). Я новичок в MCU и изучаю эту тему самостоятельно, извините, если мой вопрос для вас глупый. Что я сделал: Я создал проект в vivado, начал block design с Zynq, изменил конфигурацию PS-PL (добавил GP Master и Slave AXI Interface) [Смотри приложение]. Я читал, что Zynq может быть Master, но Slave/ периферийнoe устройство я должен спроектировать как настраиваемое IP-ядро. Я уже нашел, как создать собственный AXI IP (slave или master). Vivado создает шаблон настраиваемого IP-ядра (slave). (1) Могу ли я использовать этот шаблон без каких-либо изменений? (2) Следует ли мне добавить дополнительную информацию (сигналы, которые я использую в функции memcpy: адреса и количество битов)? Я пропустил дизайн custom master . (3) Я сделал правильно или мастер должен быть частью настраиваемого IP ядра?

-

Расположение IP Core в проекте Vivado

dsmv опубликовал тема в Среды разработки - обсуждаем САПРы

Всем доброго времени суток. Есть такая проблема с расположением файлов для проекта Vivado. В моих проектах каталог src отделён от каталога где лежит проект Vivado. Это позволяет его легко подключить под систему контроля версий. Но при таком подходе есть проблема с IP Core. Файлы xci лежат каждый в своём каталоге, они подключены под систему контроля версий, но Vivado при своей работе начинает в этих каталогах работать. И там получается очень много файлов, что неудобно. Собственно вопрос - существует ли возможность указать Vivado что бы она использовала другой рабочий каталог для IP Core ?