Поиск

Показаны результаты для тегов 'html report'.

-

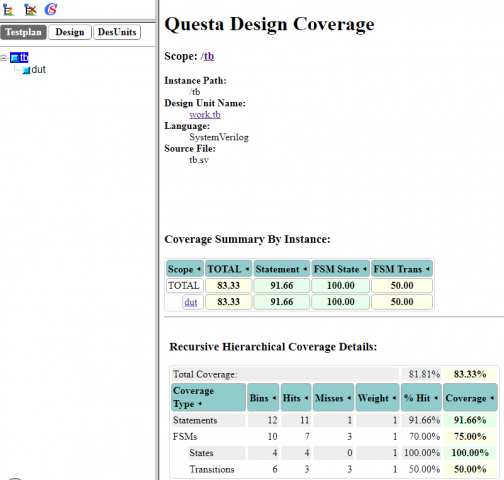

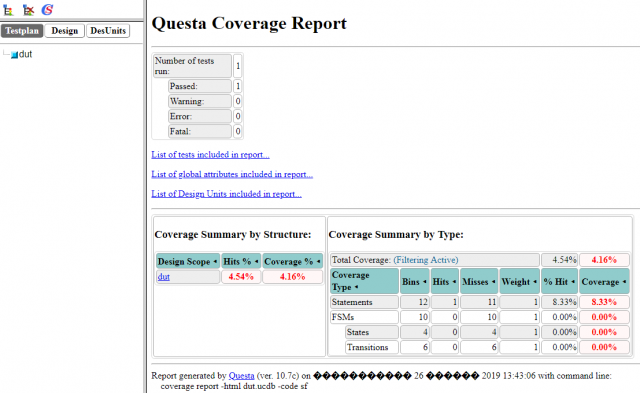

Всем добра! Столкнулся с такой проблемой: есть dut, например такого вида (dut.sv): module dut ( input logic clk, input logic res, input logic data, input logic ena, output logic q, output logic w ); always_ff @(posedge clk) if (res) q <= 1'b0; else if (ena) q <= data; else q <= q; enum {DUT_IDLE, DUT_START, DUT_PROC, DUT_END} dut_state; always_ff @(posedge clk) if (res) dut_state <= DUT_IDLE; else case (dut_state) DUT_IDLE : dut_state <= ena ? DUT_START : DUT_IDLE; DUT_START : dut_state <= DUT_PROC; DUT_PROC : dut_state <= DUT_END; DUT_END : dut_state <= DUT_END; default : dut_state <= DUT_IDLE; endcase assign w = dut_state == DUT_PROC; endmodule : dut и есть узурпирующий его test bench вида, например, такого (tb.sv): `timescale 1ns/100ps module tb; logic clk; logic res; logic data; logic ena_tb; logic ena; logic q; logic w; dut dut(.*); initial begin clk = 0; forever #10ns clk = !clk; end; initial begin res = 0; #20ns res = 1; #20ns res = 0; end initial begin data = 0; forever #30ns data = !data; end; initial begin ena_tb = 0; #70ns ena_tb = 1; #80ns ena_tb = 0; end enum {TB_IDLE, TB_START, TB_PROC, TB_END} tb_state; always_ff @(posedge clk) if (res) tb_state <= TB_IDLE; else case (tb_state) TB_IDLE : tb_state <= TB_START; TB_START : tb_state <= ena_tb ? TB_PROC : TB_START; TB_PROC : tb_state <= !ena_tb ? TB_END : TB_PROC; TB_END : tb_state <= TB_END; default : tb_state <= TB_IDLE; endcase assign ena = tb_state == TB_PROC; endmodule : tb есть tcl-скрипт (proc_tb.tcl), запускающийся в Mentore (ModesSim или QuestaSim) обрабатывающий упомянутые выше tb и dut вида # create library if [file exists work] { vdel -all } vlib work vlog -O0 +fcover +acc *.sv set top_module tb # set top_module dut set top_module_opt $top_module append top_module_opt "_opt" set coverage_letters_string "sf" # optimize design vopt +cover=$coverage_letters_string $top_module -o $top_module_opt vsim -cvgperinstance -c -coverage work.$top_module_opt # go run 200ns # make coverage report if {$top_module == "tb"} { coverage save $top_module.ucdb -instance /tb/dut coverage exclude -src tb.sv } else { coverage save $top_module.ucdb } coverage report -html $top_module.ucdb -code $coverage_letters_string # config instance window view instance source ColumnConfig_instance.tcl который, несмотря на наличии в нём строк вида coverage save $top_module.ucdb -instance /tb/dut coverage exclude -src tb.sv которые мы выполняем при моделировании с взятием в качестве модуля верхнего уровня test bench-а рисует на главной странице html отчёта картинку вида Картинка хорошая, но нам не нужен сам tb ни в дереве, ни в каких других таблицах! Нужен dut и всё, что ниже! Т.е. картина, которая нужна, получается при замене (в proc_tb.tcl) строки set top_module tb на set top_module dut что даёт Т.е. всё дерево слева и всё, относящееся к нему справа, стало, как доктор прописал, но покрытие теперь в нём стало минимальным! Test bench не сработал? ЧЯДНТ? Просьба ткнуть носом ) Как обычно, прикладываю проект. test_coverage_el.zip

-

- mentor graphics

- modelsim

- (и ещё 3 )