Поиск

Показаны результаты для тегов 'fpga'.

-

FPGA-разработчик, совмещение, Москва

Сергей СС опубликовал тема в Ищу работу

Здравствуйте В связи с наличием массы свободного времени и в то же время желанием пока не уходить совсем с основной работы, ищу дополнительную работу в Москве (хотя, если кто-то решится сотрудничать на полной удалёнке - буду рад, такой опыт тоже есть). Работаю с FPGA с 2011 года, образование МАИ; реализовал алгоритмы ЦОС в сфере радиолокации. Из самых больших ПЛИС, работал со Stratix V и Zynq 7000 и Zynq Ultrascale+ (систему на кристалле собирать умею). Контроллеры интерфейсов DDR, Ethrernet, RapidIO, SerialLite настраивал. Сборка проекта, оптимизация, задание constraint-ов, переходы между тактовыми доменами. Пишу на Verilog, хотелось бы связать основные обязанности с ним и работой с ПЛИС. Но если пригодится - программировал на чистом Си сигнальные процессоры TMS. Могу в Altium сделать относительно-простую плату (что бы изготовить и пользоваться, КД в совершенстве не оформлю). Математику моделирую в Matlab. На основной работе есть разные отладочные киты, хотелось бы находиться большую часть времени там. Могу один-два раза в неделю приезжать на неполный день поотлаживаться и пообщаться, я нахожусь в западной части (м. Кутузовская). Пишите предложения в эту тему или в ЛС. -

Образование Закончил Санк-Петербургский институт машиностроения(ЛМЗ-ВТУЗ) по специальности «Автоматизация технологических процессов и производств» в 2011 г. Опыт работы Занимаюсь разработкой системного ПО для IBM PC, MCU, FPGA. Опыт работы более 15 лет.Место работы с декабря 2012 по настоящее время: ООО Радиосистемы-СВЧ. Должность инженер 1 категории. Обязанности: разработка схем, плат, ПО для микроконтроллеров и ПЛИС в сфере цифрового радио.Навыки в области электроники и электротехники: 1. Знания цифровой и аналоговой схемотехники, электротехники. Умею разрабатывать схемы с микроконтроллерами, ПЛИС. Разрабатывать схемы питания, фильтры для АЦП, ЦАП. 2. Имею опыт работы со скоростными АЦП и ЦАП, в том числе и по стандарту JESD204C 3. Имею опыт работы с интерфейсами SPI, I2C, 1-wire, UART. 4. Имею опыт работы с интерфейсами для передачи данных на расстоянии RS-485, CAN, Ethernet. 5. Хорошо знаю Altium Designer, Cadence Allegro. 6. Умею разводить печатные платы, оформлять файлы GERBER для передачи в производство 7. Умею составлять конструкторскую документацию по ГОСТ ЕСКД, оформление схем по в соответствии с требованиями ЕСКД, перечни ПЭ3, спецификации, ПЗ и др. Для Altium Designer я написал скрипт, который автоматически экспортировал в Excel перечень нужных элементов схемы и генерировал спецификацию и ПЭ3 в формате PDF. 8. Умею моделировать схемы в PSPICE. 9. Умею загрузить и рассчитывать параметры платы в HyperLynx. (DC, рассчет cross-talk e.t.c) 10. Знаком со стандартами ПУЭ 11. Знаю устройство электромоторов и систем управления ими.(Это мое основное образование)Навыки в разработке ПО для PC 1. Знаю языки C/C++/C#, среды разработки Visual Studio, Qt, Eclipse, GNU Make. 2. Умею разрабатывать GUI приложения на Qt и .NET 3. Знаком с библиотекой C++ Boost 4. Умею разрабатывать системные приложения c Windows API(работа с устройствами, USB, TCP/IP sockets) 5. Уверенный пользователь OS Linux. Использую дистрибутив ArchLinux 6. Умею разрабатывать приложения для Linux. Хорошо знаком с разработкой системных приложений в интерфейсе POSIX и разработке GUI с применением Qt. 7. Есть опыт разработки драйверов для Linux, знаю основные особенности Linux ядра, умею собирать ядро из исходников, проводить отладку ядра с помощью KGDB 8. Знаю криптографические протоколы SSL, Ipsec.Навыки разработки для микроконтроллеров 1. Большой опыт разработки приложений для МК архитектуры ARM(Cortex-M, Cortex-A), PIC, AVR, C166, TMS320, XMOS. 2. Работал со всеми осиновым интерфейсами и блоками используемыми в МК: UART, SPI, I2C, USB, CAN, RS-485. А также с интерфейсами аудио I2S, SPDIF, видео HDMI. 3. Работа с TCP/IP используя стек lwIP или стек Keil 4. Опыт работы с протоколом MODBUS. Написал свою(не полную) кросс-платформенную реализацию MODBUS SLAVE для микроконтроллеров. https://github.com/reffum/modbus_slave.git5. Работал с DSP MCU TMS320. Писал программу для системы управления синхронным двигателем. 6. Работал с процессорами аудио-обработки XMOS.Навыки работы со встраиваемыми системами 1. Работал с процессорами линейки Cortex-A. 2. Умею собирать cross-tools gcc. Компилировать Linux-ядро, busybox, glibc. Собирать и устанавливать простую систему. Писать драйверы устройств. Также собирал библиотеку Qt и запускал ее в режиме работы через fb. Навыки работы с ПЛИС 1. Опыт работы с микросхемами XILINX и ALTERA(Spartan-3, Sparnat-6, Virtex-6, Virtex-7, Zynq-7000, Cyclone-IV, Cyclone-V, MAX 10) 2. Пишу HDL на языках Verilog, SystemVerilog, VHDL. 3. Знаю среды разработки Quartus, ISE, VIVADO, Vitis. 4. Небольшой опыт работы с XILINX HLS, VITIS. Пока на уровне изучения. Но с интересом поучаствую в проекте, где это используется. 5. Отладка HDL кода в Modelsim. Использую интеграцию с MATLAB. 6. Опыт использования скоростных интерфейсов(Ethernet, JESD204), использования DDR памяти. Контакты Олег Сергеевич Санкт-Петербург, Красное-село. e-mail: [email protected] тел. +7-950-026-73-16

-

Разработка ПЛИС в Санкт-Петербурге (Altera, Verilog)

Spb FPGA опубликовал тема в Предлагаю работу

Компания ищет для реализации части проекта программиста ПЛИС. Основной проект представляет собой разработку чипа приемника для обработки сигналов (каких сигналов и для чего, расскажем на интервью, разработка мирная, не военное применение). В этом проекте необходимо добавление нового блока обработки сигналов. Есть спецификация блока, описание интерфейсов блока к другим частям чипа, доступны для обсуждения и объяснения дизайнеры и разработчики как железа, так и софта. Задачи представляют собой полный цикл разработки – прочитать спецификацию, обсудить, реализовать, просимулировать с моделью, оттестировать блок, принять участие в тестировании всего проекта. Авторы документации хотя и русскоговрящие, вся документация на английском. Начинать можно уже сейчас. Территориально Санкт-Петербург (удаленная работа будет возможна только в случае если не найдется разработчик в Спб), гибкий график. Если предложение и задачи Вас заинтересовали, отправьте свое резюме на адрес [email protected] Бюджет не ограничен в пределах разумного, резюме с указанием пределов разумного будут рассмотрены с особым вниманием :) -

Инженер-программист ПЛИС (FPGA) г. Москва

epcmsu опубликовал тема в Предлагаю работу

Компания ООО "ЦИФ МГУ имени М.В.Ломоносова" (https://physlab.ru/) ищет на проектную работу (в течение нескольких месяцев) Инженера-программиста ПЛИС. В основном предполагается очная работа в офисе (рядом с м. Ленинский проспект/Университет), занятость от 1/2 ставки до полной, график работы гибкий. Оплата зависит от квалификации и обсуждается с заинтересованными кандидатами (варьируется от выбранной ставки). В перспективе при взаимном согласии сторон возможно постоянное трудоустройство в штат в другое наше подразделение. Имеется задача для разработки на ПЛИС, состоящая из двух частей: 1. Нужно взять из оперативной памяти массив данных и, используя протокол передачи GigE Vision (возможно, будет его урезанная версия или другой более простой, но не сжимающий данные протокол), через ПЛИС передавать данный массив на принимающий ПК. Софт со стороны ПК - задача наша. В приоритете (при возможности) не писать прошивку с самого нуля, а "накликать" большую часть из готовых блоков. Если потребуется лицензия для работы с протоколом, то это не проблема. 2. С матрицы камеры по шине LVDS необходимо получить массив данных, провести первичную обработку, далее перенести массив в оперативную память и уже после, используя ранее подготовленную часть, передать данные на верхний ПК. Также по шине SPI управлять параметрами и настройками самой матрицы. На данный момент первый этап планируется делать на zynq, отладочная плата - zedboard, вторая часть может быть выполнена на том же самом чипе, если он устроит нас по параметрам и возможностям, ну или на большем чипе от того же производителя. Если Вы заинтересованы в решении данной задачи, высылайте, пожалуйста, свое резюме на адрес электронной почты [email protected], обсудим детали. -

На вебинаре вы познакомитесь с новой средой разработки Vitis, в которой реализована парадигма высокоуровневого проектирования, и с двумя новыми аппаратными платформами от Xilinx – Versal и Alveo, для которых разработка в среде Vitis наиболее эффективна. Вебинар предназначен как для разработчиков для ПЛИС и СнК, желающих повысить свою продуктивность с помощью средств высокоуровневого проектирования, так и для программистов, ищущих возможности повышения производительности своих компьютерных систем с помощью адаптируемых аппаратных ускорителей Xilinx Alveo. Вебинар состоится 31 марта в 14:00 (мск). Повтор вебинара 2 апреля в 10:00 (мск). Участие в вебинаре бесплатное, после предварительной регистрации. Регистрация на вебинар

-

Отладочные платы на Spartan-6 и Virtex-6 (СПб)

tvShushtov опубликовал тема в Продам

Nexys 3 Spartan-6 Производитель: DIGILENT Микросхема: Xilinx Spartan-6 XC6LX16-CS324 Ссылка на подробную информацию: https://store.digilentinc.com/nexys-3-spartan-6-fpga-trainer-board-limited-time-see-nexys4-ddr/ В наличии есть 5 штук. Все платы находятся в штатных пластиковых коробках. Цена: 8000 руб ------------------------------------------------------------------------------------------- Spartan-6 FPGA SP605 Evaluation Kit Производитель: Xilinx Микросхема: Spartan-6 XC6SLX45T-FGG484-3C Ссылка на подробную информацию: https://www.xilinx.com/products/boards-and-kits/ek-s6-sp605-g.html В наличии есть 1 штука в штатной коробке. Цена: 18000 руб ------------------------------------------------------------------------------------------- Virtex-6 FPGA ML605 evaluation kit Производитель: Xilinx Микросхема: Virtex-6 XC6VLX240T-1FFG1156 Ссылка: https://www.xilinx.com/products/boards-and-kits/ek-v6-ml605-g.html В наличии есть 1 штука в штатной коробке. Цена: 22000 руб ------------------------------------------------------------------------------------------- Платы почти не использовались - лежат без дела. Пересылать почтой России их не хотелось бы, но в Москву и другие близлежащие города можно будет передать. Доп. фото: -

Всем привет. У меня имеется плата, на борту которой находится Arria 10 и флешка MT25Q. Мне необходимо спомощью System Console выполнять запись и чтение данных во флеш память. Для правильного написания скрипта, я решил пронаблюдать, каким образом NIOS обращается к флеш контроллеру, чтобы определить порядок дейтсвий. В результате, функции по чтению и стиранию сектора работают, а по записи - нет. Проверял с помощью SignalTap. Последовательность действий простая (в первом приближении) : 1. Чтение контрольного регистра флешки. 2 Если она не занята - запись в регистр FLASH_MEM_OP адресса сектора и команды write_enable. 3. Запись в тот же регистр команды на очистку сектора. 4. Ожидание, пока флешка выполнит предыдущие операции. 5. Запись данных в секутор с указанным адресом. Что самое интересное, я заполнял необходимый для чтения сектор через програматор (jic) и чтение с указанного адреса выполняется правильно. Почему контроллер не хочет писать во флешку?

-

1. Санкт-Петербург (помощь при релокации из других городов); 2. Метро Площадь Мужества; 3. Зарплатная вилка: 100-150 000р. Net. Наш клиент, компания, более 15 лет занимающаяся производством средств и комплексов радиоконтроля, находится в поиске Разработчика систем цифровой обработки сигналов на ПЛИС. Выпускаемая организацией продукция эксплуатируется во всех регионах Российской Федерации и ближнем зарубежье. Предприятие сотрудничает со многими научными и промышленными предприятиями северной столицы. Чем нужно будет заниматься: - Цифровая обработка сигналов на базе ПЛИС (FPGA); - Разработка новых и перенос существующих алгоритмов из Matlab/С/С++ на архитектуру ПЛИС; - Участие в разработке аппаратно-программных комплексов для систем радио мониторинга, радиолокации, имитации сигналов; - Разработка дизайна для ПЛИС Xilinx Kintex 7, Ultrascale, SOC Zynq Ultrascale+ с использованием System Verilog, Verilog и VHDL; - Работа с высокоскоростными микросхемами АЦП и ЦАП, интерфейсами SRIO, PCIe, JESD204, DDR4, Ethernet и др.; - Разработка с использованием современных методологий разработки: трекер задач, билд-сервер, автоматический прогон тестов, гит.; - Написание тестбенчей и документации к своим разработкам; - Развитие и рефакторинг уже написанных модулей. Требования к профессиональным знаниям кандидата: - Опыт разработки под ПЛИС Xilinx в среде Vivado; - Знание языков описания аппаратуры: SystemVerilog, VHDL; - Опыт работы с высокоскоростными АЦП и ЦАП; - Опыт оптимизации по таймингам; - Опыт верификации (псевдослучайные тестовые воздействия, написание эталонных моделей алгоритмов на языке Matlab, симуляция в QuestaSim). Дополнительным плюсом будет: - Знание C/C++, опыт работы в Linux и SOC Zynq, написание скриптов на TCL; - Знание алгоритмов цифровой обработки сигналов (фильтрация (дециматоры, интерполяторы, дробные ресамплеры), бпф, гребёнки фильтров, корреляторы, обнаружители сигналов (CFAR и др), смесители, параллельная обработка сигналов (частота дискретизации выше клока обработки), обработка в плавающей точке и др.). Условия работы: - Оформление по ТК РФ с первого дня работы; - Зарплата "белая" - обсуждается по итогам собеседования; - Комфортный офис недалеко от ст. метро Пл. Мужества; - Возможность гибкого графика (с 9..11 до 18..20); - Поощрения после успешных сдач работ; - 13-я заработная плата по итогам года; - Испытательный срок 1-3 месяца; - Интересные задачи и быстрое внедрение и воплощение Ваших идей; - Дружный и надежный коллектив; - Кандидатам из других городов РФ можем помочь с переездом.

-

Совместная работа нескольких FPGA

cudnn опубликовал тема в В помощь начинающему

Я не имею никакого опыта и теор подготовки по этому вопросу. По профессии программист. Интересуюсь нейросетями. На сколько я знаю, предпринимаются попытки организовать параллельные вычисления с помощью FPGA. С другой стороны, в одном из роликов на youtube автор создает эмулятор Spectrum. Он впаивает Cyclone IV на макетную плату и дальше собирает схему. Мой вопрос состоит из двух частей. 1. Cyclone IV реально распаивать без спец. оборудования. А Cyclone 10? Т.е. можно ли работать с современными производительными FPGA как с элементной базой, или там возможен только вариант с dev board? 2. Как можно организовать совместную работу нескольких FPGA типа Cyclone 10 c массивом (потоком) данных? Есть ли практический способ соединить их через общую память. Или единственный вариант это большой круг типа Cyclone 10 -> dev board -> Ethernet -> dev board -> Cyclone 10 -

Вышел Quartus Prome Pro Edition v19.1

StewartLittle опубликовал тема в Среды разработки - обсуждаем САПРы

Вышел Quartus Prime Pro Edition v19.1. Можно скачивать с исторической родины. Релиз ноутсов пока нет. Но требования к объему памяти для работы со Stratix 10 впечатляют (80 - 128 GB). Номер версии v19.0 этом лихо пропущен:) Для Quartus Prime Standard Edition и Quartus Prime Lite Edition новой версии не предлагается, для них по-прежнему остается крайней v18.1. Что-то это навевает грустные мысли... -

Требуется инженер-программист ПЛИС

bugway опубликовал тема в Предлагаю работу

Требуется инженер-программист ПЛИС для написания прошивок для нескольких проектов. Требования к кандидату: - Опыт работы с различными типами ПЛИС не менее 3 лет - Опыт работы с микроконтроллерами STM32 и другими не менее 3 лет - Опыт работы с Altium Designer, Quartus и другими средами. - Опыт видеообработки с помощью ПЛИС - Опыт работы в команде - Умение разбираться в чужих проектах - Проживание в Москве, желательно поближе к Люберецкому району Немного общей информации по проектам: 1. Видеообработка (2 проекта) - ключевые моменты: сглаживание изображений, работа с видеобуфером, работа с MIPI, PAL/SECAM видеовыходом, работа ПЛИС в паре с микроконтроллером 2. Обработка сигналов (1 проект) - ключевые моменты: работа ПЛИС в паре с микроконтроллером, работа с таймером, точные временные измерения, детектирование аналоговых и цифровых сигналов, работа с оптическими датчиками Оплата договорная Есть перспектива трудоустройства на штатную должность. Контакты: E-mail: vbug2 (собака) yandex.ru Вконтакте: vk.com/bugway -

Six Automated Steps to Design Partitioning for Multi-FPGA Prototyping Boards Presenter: Krzysztof Szczur, Verification Products Manager Thursday, October 10, 2019 Abstract: Presently, emulation and FPGA-based prototyping are essential verification and validation techniques for a SoC, ASIC designs and become irreplaceable in pre-silicon verification of Deep Learning Accelerator designs. Challenges of the multi-FPGA design setup like partitioning, multiplexing limited I/O interconnections and mapping multiple clock domains across multiple devices may cause significant delays in prototype bring-up and verification schedule. Design partitioning tool that can be used with either off-the-shelf or custom made FPGA boards will automate the most tedious tasks and so significantly reduce the risk. Aldec provides HES-DVM Proto toolbox with automatic design partitioning for multiple FPGAs including Xilinx Virtex-7 and UltraScale XCVU440. In this webinar we will demonstrate how to compile and partition an open source design of Deep Learning Accelerator into 6 FPGAs in 6 steps which are fully automated. Agenda: Multi-FPGA Design Prototyping Challenges HES-DVM Proto Overview Live demo – 6 steps / 30 minutes to partition DLA design Conclusion Q&A Event Info EU Session 3:00 PM – 4:00 PM CEST Thursday, October 10, 2019 Register for EU Session US Session 11:00 AM – 12:00 PM PDT Thursday, October 10, 2019 Register for US Session Presenter Bio: (Chris) Krzysztof Szczur is a Hardware Verification Products Manager at Aldec. Chris joined Aldec in 2001 and was a key member of the team that developed HES-DVM™, Aldec's FPGA-based emulation and prototyping technology. In his engineering career he has also worked in the fields of HDL design verification, testbench automation and DO-254 compliance. Krzysztof has practical experience and a deep understanding of hardware assisted verification methodologies. Krzysztof graduated as M.Eng. in Electronic Engineering (EE) at the AGH University of Science and Technology in Krakow, Poland. View On Demand Webinar View Upcoming Webinars Aldec is a global industry leader in Electronic Design Verification and offers a patented technology suite including: RTL Design, RTL Simulators, Hardware-Assisted Verification, Embedded, SoC and ASIC Prototyping, Design Rule Checking, CDC Verification, IP Cores, DO-254 Functional Verification and Military/Aerospace solutions.

-

- fpga

- asic prototyping

-

(и ещё 1 )

C тегом:

-

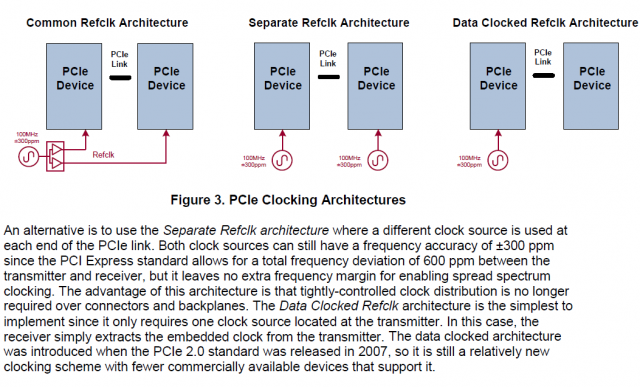

Вопрос не в том, можно ли так по правилам (читай - стандартам), а в том - можно ли от них и насколько отходить. Итак: дифференциальный RefClk частотой 100МГц надо заводить на каждый PCI-E target, основная цель, я так понимаю - чтобы у мультигигабитных трансиверов был исходный клок с одним и тем же дрейфом. Вопрос: а можно ли не заводить, а генерить локально? в сети разные мнения, от Note that the pcie bus ref clock needs to be common between all devices communicating on the pcie bus. До https://www.xilinx.com/support/answers/18329.html с техникой Asynchronous Clocking Также есть такая вот картинка: которая вроде бы говорит, что такое вроде как приемлемо, но хотелось бы ответа практиков. Зачем это всё? Есть девборда с Xilinx US/US+ c FMC но без PCI-E слота, сейчас появилась необходимость работать с PCI-E самая простая и материально незатратная идея реализовать это: изготовить райзер из FMC в PCI-E (через тот же USB3.0 кабель, которй используется китайцами повсеместно для выноса с материнки PCI-E 1х ). Но вот незадача - на FMC разведены мультигигабитные трансиверы, но задающий клок для них распаян локально на плате (номинал может программироваться во внешней фапч), резать дорожки, куда-то там подпаиваться - такой кейс совсем исключён. Поэтому для принятия решения о райзере хотелось бы заручиться уверенностью что заработает хотя бы в лабораторных условиях (в продакшене это использоваться не будет). (лабораторных условиях == температура 25С, что должно снизить разбос задающих частот на разных концах MGT)/ PCIe-Clock-Source-Selection.pdf

-

FPGA начального уровня

KeisN13 опубликовал тема в Обучающие видео-материалы и обмен опытом

Небольшая серия видеоуроков, в которой на несложном Hello PUF проекте демонстрируется минимум, который необходим современному разработчику на плис, пускай даже и начального уровня. В курсе есть: Работа в Vivado Разработка кода на VHDL и Verilog Использование атрибутов синтеза Сборка софт-процессорной системы на базе MicroBlaze Создание проектных ограничений Работа с Tcl консолью и создание скрипта на Tcl Работа в SDK и разработка C кода для софт-процессорной системы Подключение и отладка проекта с использованием ILA Поскольку курс закончился и проект был завершён, выкладываю его здесь. Надеюсь начинающим пригодится. https://www.youtube.com/playlist?list=PLWMg96mLREOeHuNGxkIUo-iCHPxdReQAX -

Требования к lvds сигналам

Skryppy опубликовал тема в Работаем с трассировкой

Здравствуйте. Подскажите какие требования к допустимым отклонениям длины lvds сигналов мне заложить для прибора с ПЛИС. Конструкторы требуют от меня данные. Нашел в интернете формулу, получились такие данные: Шина данных Data1_p, data1_n ... data 9 - частота 420 МГц. 1) Погрешность длины для _p или _n одного сигнала не больше 0,635 мм. 2) длины дорожек для группы сигналов (10 пар сигналов с АЦП, 420 МГц) должны различаться не более 6.35 мм. (Режим работы DDR) Правильно ли я задал данные, или ошибся? Какие примерно должны быть требования к сигналам с такими частотами? -

Принцип работы FPGA (ПЛИС) отличается от работы обычных процессоров и микроконтроллеров. Если микроконтроллер выполняет программу, то в ПЛИС обработка данных и управление производится на аппаратном уровне. Это обеспечивает многопоточность и высокую производительность. Тем не менее, из-за дороговизны и ограниченного набора средств разработки популярность ПЛИС среди пользователей и любителей электроники оказывается не такой высокой. Впрочем, появление недорогих и простых в использовании отладочных плат, например, TinyFPGA или iCEBreaker, может сделать FPGA более доступными для широкого круга разработчиков. Читать далее >>

-

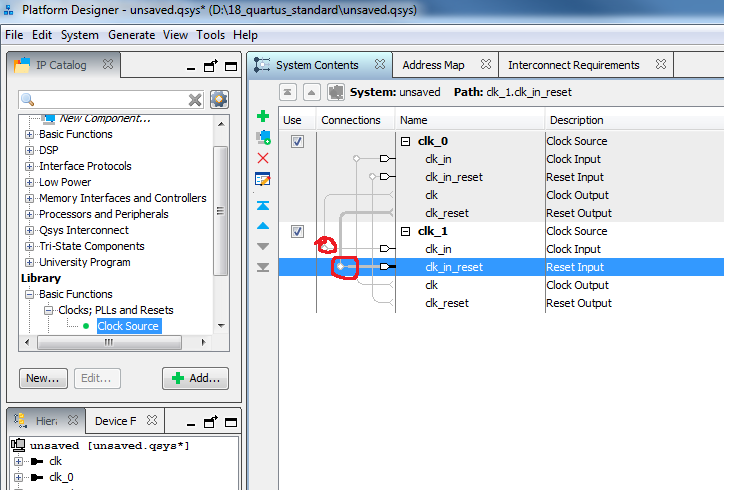

Добрый день! При использовании Qsys'a В Quartus возникает следующая проблема: Не соединяются сигналы разных компонентов. Просто не могу поставить точку на соединении. Коллега по работе использует тот же самый квартус - у него все работает. Подскажите пожалуйста, в чем может быть дело? Использую Quartus 18 Standard. Скрин прилагаю

-

Ищем программиста ПЛИС. Релокация

Yuri_v опубликовал тема в Предлагаю работу

В догонку к Ищем программиста ПЛИС на постоянную работу в Швецию. - официальное трудоустройство - полный соцпакет, согласно шведского законодательства - интересные R&D проекты в сфере радиоэлектроники: 5G, SDR, SDN, AIML - профессиональная команда с многолетним опытом в R&D проектах (Ericsson, ABB, Saab) - командировки по ЕС и Скандинавии - рабочий язык - английский - з/п по результатам собеседования и тарифам профильного профсоюза (от 500,000 SEK / год) Детали в личку или на почту из анонса выше -

Ищем программиста ПЛИС/FPGA в Германию

syoma опубликовал тема в Предлагаю работу

Мы ищем программиста ПЛИС/FPGA в немецкий филиал одной очень серьезной компании с мировым именем. Город Konstanz, земля Baden-Württemberg Требования и описание вакансии можно прочитать здесь: https://jobs.gecareers.com/global/en/job/3257034/FPGA-Software-Engineer-m-f-d Там же, после регистрации, можно отправить резюме (сорри, я не имею никакого влияния на процесс). Трудоустройство по тарифному договору - Urlaubsgeld, Weihnachtsgeld, отпуск и т.д. Зарплата хорошая для Германии в общем и Baden-Württemberg в частности. Для тех, кто заинтересован, привожу FAQ по работе в Германии из других вакансий: Мне дополнить нечего и большинство из указанного относится также к данной вакансии . -

Вакансия Разработчик FPGA Санкт-Петербург

Ekaterina Sergeeva опубликовал тема в Предлагаю работу

Всем доброго времени суток! Компания НПП «Цифровые радиотехнические системы» ищет разработчика FPGA. Мы занимаемся разработкой и производством систем управления воздушным движением. Наш флагманский продукт – многопозиционные системы наблюдения, позволяющие следить за местоположением самолётов, отслеживать воздушную обстановку. Также мы работаем над проектами по разработке бортового оборудования, развиваем направление по обеспечению полётов беспилотников. Обязанности: · разработка кода для FPGA/SoC ф.Altera и Xilinx, его отладка и поддержка; · поддержка и доработка существующего кода; · разработка специализированных IP-модулей и регистровых моделей к ним, интеграция их в систему; · разработка и реализация алгоритмов ЦОС в области формирования и приема радиолокационных сигналов; · разработка и реализация алгоритмов автоматического управления; · активное взаимодействие с программистами и схемотехниками при настройке и отладке опытных образцов. Требования: · высшее образование (Вычислительные машины, комплексы, системы и сети); · знания и опыт разработки на Verilog; · владение пакетом Quartus или Vivado; · умение осуществлять моделирование в пакете ModelSim (QuestaSim); · базовые знания в области ЦОС (фильтрация, алгоритмы автоматического регулирования); · опыт работы в среде Matlab; · умение читать электрические схемы, базовые знания по схемотехнике; · умение работать с измерительным оборудованием; Мы предлагаем: · Полностью «белая» заработная плата (уровень заработной платы обсуждается индивидуально, в зависимости от опыта кандидата); · Гибкий график работы. -

Как соединить ВЧ сигналы между платами

Skryppy опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Здравствуйте. У меня возникла проблема, прибор с ПЛИСами + куча ЦАП + ВЧ микросхем не умещается на одну плату, надо разбить его на две платы. Думаю оставить на одной плате цифровые микросхемы и ЦАПы, а на другую перенести ВЧ часть. Вопрос можно ли для передачи с платы на плату 75 Омного дифференциального сигнала с выхода ЦАП (AD9739) использовать мезонинные разъемы типа QFS–026–04.25–L–D–A (или подобные) или же нужно использовать коаксиальные ВЧ разъемы(как тогда выравнивать длину диф пар с кабелями?) ? Сами ЦАПы перенести на другую плату не получится, так как места для сотен диф-пар и разъемов для них тоже нет. Может быть есть какое-нибудь более простое решение? -

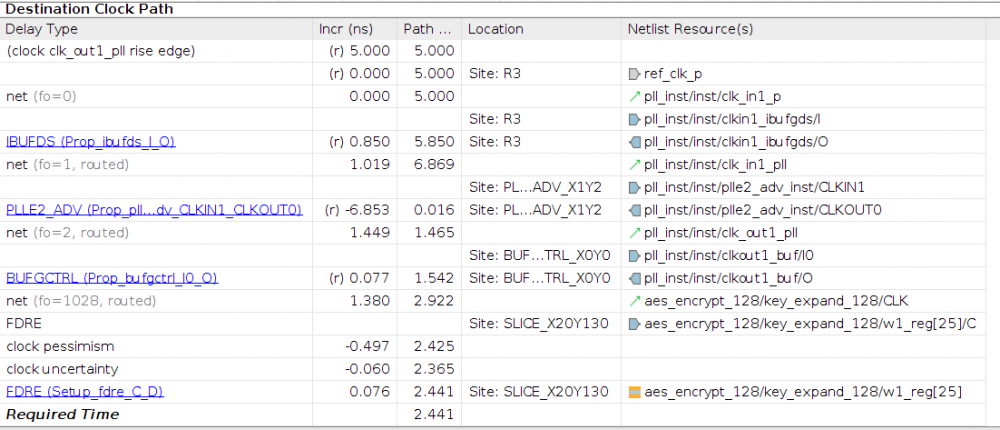

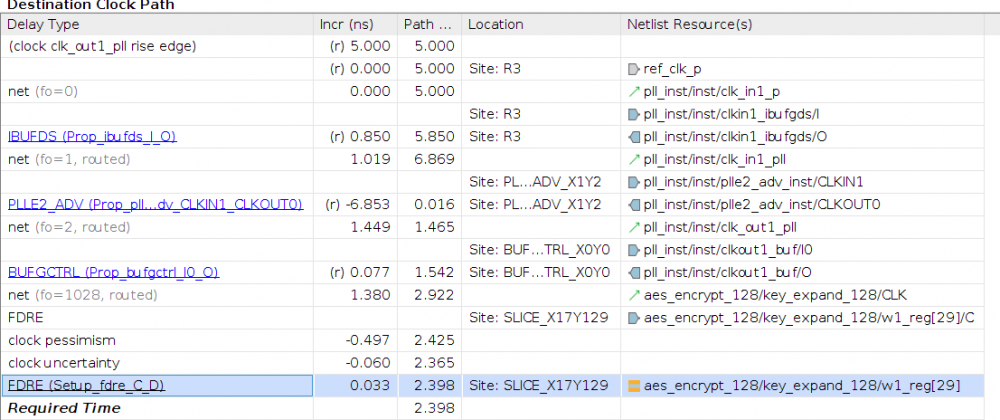

Имеются две практически идентичные реализации одного и того же проекта. Ниже приведены две таблицы с характеристиками Destination Clock Path (для обоих вариантов). Видно, что различие имеется только для параметра Setup_fdre_C_D: в одном случае он равен 0.076 ns, а в другом 0.033 ns. Отличия в реализации по сути только в одном: в первом случае триггер размещен в SLICEM, во втором в SLICEL. На данный момент мне неясны следующие моменты: что означает параметр Setup_fdre_C_D – это “настоящий” Tsetup для триггера или это какая-то “приведенная” величина (используемая в Xilinx Timimg Analysis) почему при практически идентичной структуре эти параметры имеют различные значения – это отличие обусловлено тем, что используются SLICEM/SLICEL или чем-то другим?

-

Ищем сотрудника

PLISovik опубликовал тема в Предлагаю работу

Санкт-Петербург Полная занятость Ищем в штат программиста для ПЛИС. Компания небольшая, поэтому задач много и они разные: Требования: • Высшее профессиональное (техническое) образование; • Опыт работы с ПЛИС фирм XILINX, Altera (Intel); • Знание принципов цифровой схемотехники; • Знание САПР: Quartus; Vivado Design Suite; • Знание System Verilog/Verilog или VHDL; • опыт работы с высокоскоростными интерфейсами: • Опыт моделирования, верификации и отладки проекта; • Опыт написания testbench; • Практические навыки использования Git / SVN; • знание английского языка в объеме, необходимом для чтения и понимания технической литературы по направлению деятельности; Плюсом является: • Опыт разработки на ПЛИС семейства Altera: Arria10, Cyclone10 и ПЛИС Xilinx: Zynq-7000, Virtex-7, Kintex-7; • Знание современных сетевых технологий Ethernet, STM, SDH, OTN, DWDM; • Опыт работы с интерфейсами DDR2/DDR3/DDR4, PCI Express, 1G/10G/100G Ethernet • Знание криптографических алгоритмов и протоколов. • Опыт программирования на C По деньгам у нас все честно, чётко и стабильно. Нам нужно понять кто вы и что можете, пишите на [email protected] Обязательно указывайте телефон для связи. Присылайте портфолио. -

Разработчики ABB Russia (Москва, м. Авиамоторная)

LessNik опубликовал тема в Предлагаю работу

АББ в России - крупная международная компания, лидер в области продуктов и технологий для электроэнергетики и автоматизации - объявляет об открытии двух вакансий: - Инженер-программист ПЛИС и микроконтроллеров https://hh.ru/vacancy/29343857 - Инженер-программист Embedded Linux и Qt https://hh.ru/vacancy/29441566 Резюме просьба высылать через hh.ru.- 2 ответа

-

- fpga

- микроконтроллеры

-

(и ещё 2 )

C тегом:

-

fpga Разработка прошивки для ПЛИС и Zynq; тестового ПО на Linux

von.gostev опубликовал тема в Предлагаю работу

Город Москва Оплата 250000 за проект Работа по договору с физлицом. Срок на изготовление три месяца. Дальнейшая платная поддержка при необходимости. ТЗ прилагается. Решается задача кодирования и декодирования цифровой информации по заданному алгоритму. Необходимо разработать прошивки для кодера (Digilent Cmod A7-35T) и декодера (Zynq 7020 + Digilent Pmod DA3 + Analog Devices EVAL-AD9467), а также тестовое ПО для Linux, совместимое с Raspberry Pi 2, или же API для доступа к устройствам из-под Linux. Техническое_задание_на_программный_комплекс_кодирования_и_декодирования_цифровой_информации.pdf