Поиск

Показаны результаты для тегов 'fpga'.

-

ПЛИС PangoMicro

Gas Wilson опубликовал тема в Работаем с ПЛИС, области применения, выбор

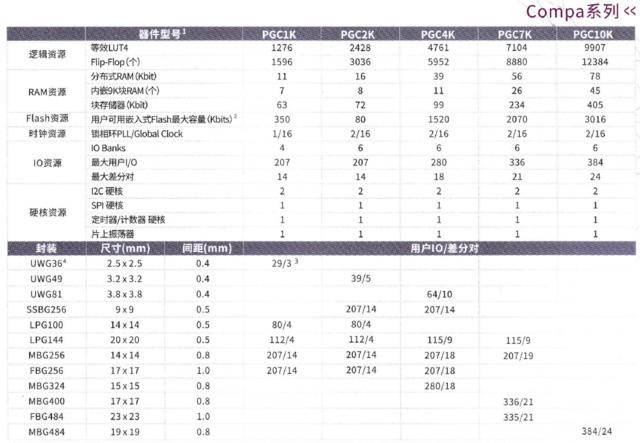

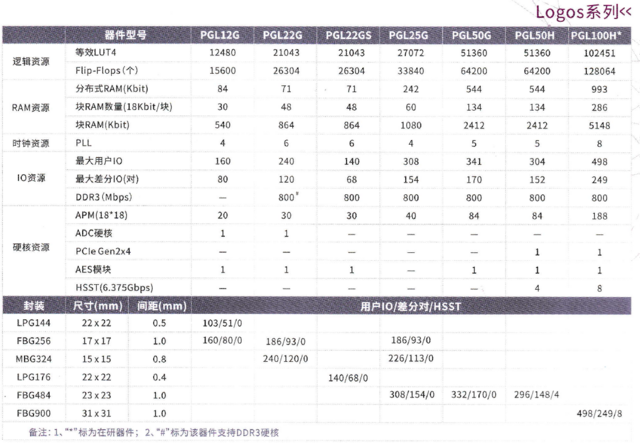

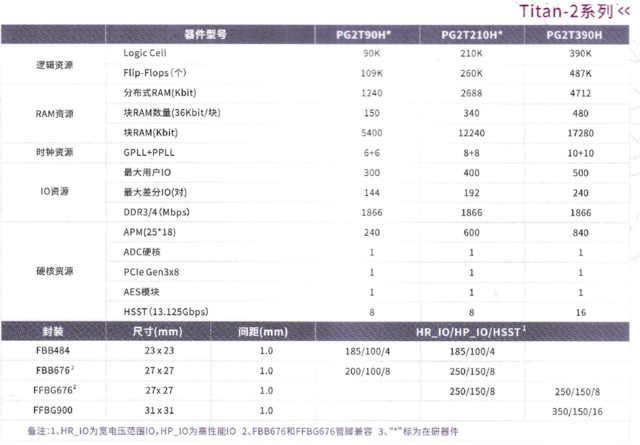

Даташиты на английском на семейства Compact, Logos 2 и Titan от Pango Micro. Перевод не супер, но легче ориентироваться, чем в китайском даташите. Logos - уровень Spartan 6 Titan - уровень Kintex 7 XC6SLX25 FTG256 -> PGL25G FBG256 XC7A50T FGG484 -> PG2L50H FBG484 XC7A100T FGG484 -> PG2L100H FBG484 XC7K325T FBG676 -> PG2T390H FFBG676 DS03001 Compact Family CPLD Device Data Sheet 1.5.pdf DS04001_Logos2 Family FPGA Device Data Sheet .pdf DS05001 Titan2 Series FPGA Device Data Sheet 1.pdf -

1. Главной проблемой была некорректная работа Hierarchy Updater’а: пока он не может корректно построить дерево проекта в тех местах, где в VHDL используются внешние модули (Verilog / IP-Core), но об этом я уже писал. 2. Для некоторых может быть непривычно и неочевидно, что (в строгом соответствии с VHDL’93) при использовании entity из библиотеки Work, необходимо указывать: library work; use work.all; 3. Несколько напрягает, что все справочные материалы на китайском. 4. Немного изменилась работа с атрибутами: для VHDL необходимо использовать Syn_* атрибуты (на 2023.1 достаточно было использовать PAP_* атрибуты – тогда было меньше warning/info о преобразовании Syn_* атрибутов в PAP_*). С другой стороны в ADS_Synthesis_User_Guide.pdf добавлено очень подробное описание правил применения Syn_* атрибутов с примерами на каждый случай. Но главной проблемой был п.1, т.к. приводил к падению Compile с «internal error» без объяснения причин падения. Отмечу, что Pango Micro старается сделать PDS/ADS лучше, с каждым шагом (2022.2-SP4->2023.1->2023.2-SP1) я отмечаю существенные сдвиги в лучшую сторону.

-

Сейчас активно изучаю тему декодирования DVB-S2 сигналов и столкнулся с задачей перестановки бит в проверочной части поступаемого фрейма. Известно, что это делается до декодера и известно, что это необходимо из-за особенностей кодера DVB-S2. Информации по этому нашел не много, лишь мнения разных людей, которые с этой темой связаны. Можете ли "тыкнуть" где и что на эту тему можно почитать? Какие варианты реализаций известны или популярны. Интересно как реализуется подобный "перестановщик" + не хочется изобретать велосипед. Заранее спасибо!

-

Моделирование проектов ПЛИС PangoMicro

Xagen опубликовал тема в Методы и средства верификации ПЛИС/ASIC

а как этот проект моделировать? У меня вообще серьезные проблемы с моделированием. Ни одно IP ядро не моделируется. Все падают с ошибками на этапе компилирования в modelsim или questasim. Судя по логам какая-то проблема с зашифрованными исходниками. Ругается на синтаксис в зашифрованном регионе. При этом в самом PDS синтезируется. -

Добрый день! Может кому пригодится. Разбираюсь с платой AXP100 (с PG2L100H). На моей плате вместо указанного в документации PHY KSZ9031RNX оказался установлен PHY jl2121 с последовательными сопротивлениями (33 Ом) в цепях RGMII со стороны драйверов PHY. Пробовал запустить демо проект ethernet_test не заработал, искажались полученные FPGA полубайты. Проверил на другой плате AXP100 с KSZ9031RNX демо проект работал отлично. Начал разбираться с RGMII, предположил, что у по умолчанию jl2121 нет задержки rx_clk как у KSZ9031RNX (datasheet на jl2121 мне найти не удалось), но прицепившись логическим анализатором увидел задержку, плюс к этому пробовал задерживать rx_clk на разное время уже в FPGA, не помогало, так что причина была в другом. Сами искажения полубайтов выглядели так, как будто duty cycle у rx_clk на входе FPGA не 50%, повторялись старшие полубайты. Попробовал убрать последовательные резисторы соединив выходы PHY jl2121 напрямую с FPGA как в схеме подключения PHY KSZ9031RNX, это также не дало положительного результата. Правда, после того как восстановил резисторы тип искажений изменился, появлялись все полубайты но они были перепутаны, так как будто rx_clk был задержан больше требуемого на входе FPGA. Но это уже легко вылечилось инвертированием в FPGA rx_clk. Теперь ethernet_test работает с PHY jl2121.

-

Собираю систему из нескольких АЦП на плате с интерфейсом передачи данных JESD204B. ПЛИС SoC Zynq UltraScale+. После тщательного анализа и подбора компонентов, было принято решение использовать клоковый дистрибьютор LMK04610 для формирования опорных частот и сигналов Sysref. Эта микросхема подходит по всем требуемым параметрам и она одна из немногих, которая свободно покупается сейчас в РФ. Когда я работал с похожими микрухами от Analog Devices, я всегда использовал их базовое ПО для оценочных плат, которое позволяет моментально разобраться в регистрах микросхемы, её режимах, в считанные минуты указать все необходимые для работы режимы и получить полную карту регистров, которые необходимо прописать в микросхему. У Texas Instruments есть точно такое же ПО (TICSPRO-SW), которое я очень хочу скачать для быстрого освоения микросхемы, но перепробовал уже все возможные способы и не выходит. Сайт "ti com" Просто не позволяет скачивать ПО без регистрации, но зарегистрироваться на почту созданную в России нельзя (даже на почту домена GOOGLE). При регистрации просто не приходит письмо подтверждения почты. Мой вопрос, может ли кто то помочь скачать на сайте "ti com" программу TICSPRO-SW"? Или может быть подскажете как это можно сделать. Пробовал уже и под VPN создавать почту.. не работает, просто не приходит письмо подтверждения.

- 6 ответов

-

- ticspro-sw

- lmk04010

-

(и ещё 2 )

C тегом:

-

Инженер-разработчик электронной техники (г. Москва)

Элина опубликовал тема в Предлагаю работу

АО "Национальный Инновационный Центр" В сплоченной команде, реализующей проекты в области разработки программно-аппаратных средств защиты информации открыта вакансия инженера-разработчика электронной техники Предстоит заниматься: разработкой аппаратных платформ, предназначенных для защиты информации; разработкой принципиальных схем, трассировкой, отладкой разработанных изделий; разработкой конструкторской документации по создаваемым изделиям; конструкторским сопровождением созданных изделий (участие в постановке на производство, внесение изменений, ликвидация недочётов, дальнейшая доработка). Мы ожидаем: умение работать с CAD-CAM системами, применяемыми для разработки электронной техники (Cadence, Altium и т.п.); опыт работы с Altium рассматривается как преимущество; готовность освоить работу с Altium Designer в том случае, если такого опыта ещё не имеется; умение работать с Embedded Linux рассматривается как существенное преимущество; желателен опыт работы с FPGA, предпочтительно Altera-Intel. Уважаемы соискатели, мы предлагаем преимущественно дистанционный формат работы (1 день в неделю нужно посещать офис у м. Калужская). Заработная плата зависит от компетенций, которыми обладает соискатель и обсуждается индивидуально с каждым соискателем. Готова ответить на вопросы @e_tand_r +7 963 978 34 77- 2 ответа

-

- altium designer

- fpga

-

(и ещё 1 )

C тегом:

-

Приветствую, господа. Может, есть какие-то апноты по созданию приёмника на основе IODELAY + IEM + IDES? Вроде бы чувствую, что с помощью IEM можно отказаться от битовой тренировочной последовательности, но дальше своих чувств и предположений продвинуться не могу. Кто-нибудь работал с модулем IEM? Где можно найти хоть какое-нибудь описание, кроме состава портов?

-

В настоящий момент под заказ доступны отладочные наборы AXP390, AXP100B и AXPGL50H. В каждый набор входит отладочная плата, внешний источник питания, JTAG-кабель и набор кабелей. Подробнее

-

- fpga

- pangomicro

-

(и ещё 4 )

C тегом:

-

ПЛИС PangoMicro Compact

Abo опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую, коллеги. Пришлось осваивать Панго серии компакт. Сделал простенький тестовый проект с использованием встроенного в микросхему генератора (в приложении весь проект). сделал констрейны на клоки и выходы. Однако при сборке получаю критическое предупреждение: "Place-2028: CASCADED_GLOBAL_CLOCK: the driver GTP_OSC_E2_inst/gateop fixed at OSC_11_174 is unreasonable. Sub-optimal placement for a clock source and a clock buffer." Не понятно, как от этого предупреждения избавиться. Чтение доступной документации и поиск не привели даже к догадке, где искать ответ. Может конечно не все прочитал. Прошу совета, куда рыть? Ну не могу я себе позволить оставлять в проектах даже предупреждения. pangotest.zip -

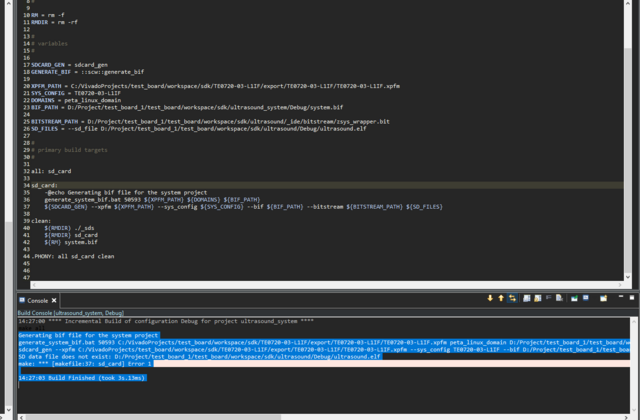

Ошибка при сборке проекта в Vitis 2019.2

Иван21 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

При сборке проекта возникает ошибка SD data file does not exist. Подскажите пожалуйста в чем может быть дело? -

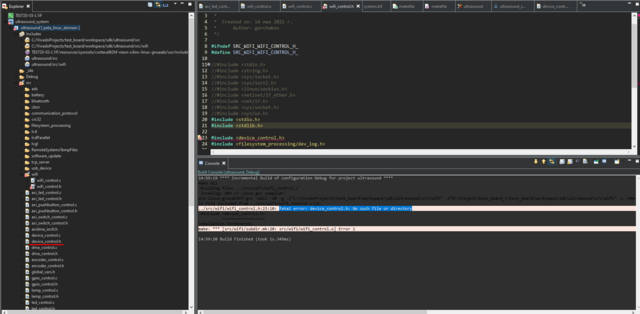

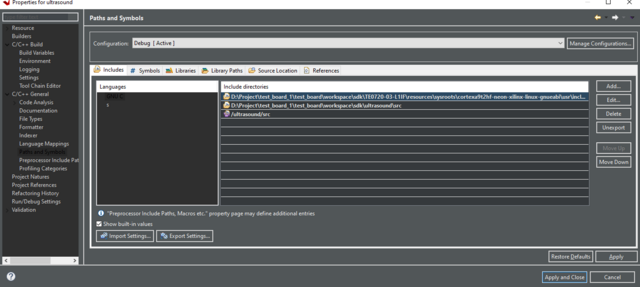

При сборке проекта возникает ошибка "fatal error: device_control.h: No such file or directory". В Includes указал путь к device_control.h, но почему то Includes не обновляется, остаются старые пути. Подскажите пожалуйста в чем может быть дело?

- 2 ответа

-

- fpga xilinx

- fpga

-

(и ещё 1 )

C тегом:

-

Макро групп начинает сотрудничество с ALINX Electronic Technology (Shanghai) – производителем встроенных интеллектуальных продуктов и технологических решений на базе программируемых логических интегральных схем, а также сопутствующих плат расширения. Подробнее

-

Вебинар: ПЛИС и отладочные платы PangoMicro

МакроГрупп опубликовал тема в Объявления пользователей

Приглашаем на информационно-технический вебинар, посвящённый продукции китайских компаний PangoMicro и Alinx. В связи с усиливающимися санкциями все настойчивее встает вопрос замены компонентов производства западных компаний. Компания Макро Групп, являясь ведущим центром компетенций по применению продукции Xilinx, так же занимается поставками аналогов от китайских производителей. Подробнее -

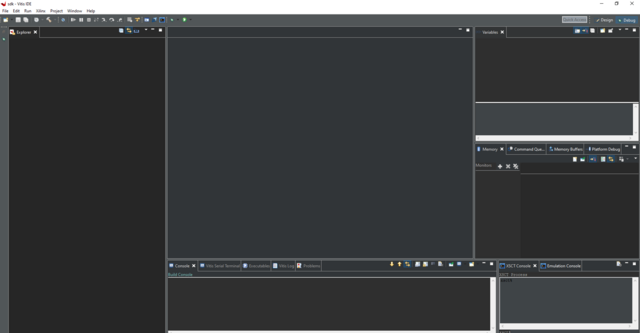

Xilinx Vitis 2019.2

Иван21 опубликовал тема в Программирование

Помогите чайнику. Открываю проект,он пустой, до этого все нормально было, не могу понять в чем дело, ничего не менял, не нажимал где не надо. Заранее спасибо.- 3 ответа

-

- fpga xilinx

- fpga

-

(и ещё 1 )

C тегом:

-

Вакансия FPGA/SoC Engineer

dmi_iii опубликовал тема в Предлагаю работу

Крупная радиоэлектронная компания ищет разработчика устройств на базе ПЛИС и СнК. Форма занятости: 5-дневная рабочая неделя Локация: Санкт-Петербург, м. Политехническая Требования к кандидату: • Высшее техническое образование по профилю радиофизика/радиотехника/микропроцессорная техника; • Опыт работы в данном направлении от 3 лет; • Наличие завершенных проектов; • Владение английским языком; Ключевые обязанности: • Оценка вычислительной сложности и необходимых ресурсов FPGA/SoC для разрабатываемых алгоритмов; • Перенос алгоритмов цифровой обработки сигнала (децимация, фильтрация, модуляция, демодуляция, преобразование Фурье, корреляционный анализ) с CPU на FPGA и SoC серии UltraScale и выше; • Документирование алгоритмов; • Работа с электрической схемой; • Взаимодействие с разработчиками аппаратной части; Требуемые навыки: • Разработка прошивок для FPGA, SoC фирмы Xilinx; • Моделирование RTL-модулей; • Владение средами Vivado / Vitis; • VHDL/Verilog, TCL Преимуществом будет: • Владение С/C++ • Опыт программирование CUDA; • Владение системами контроля версий; -

Приглашаем принять участие в вебинаре, посвященном ПЛИС и отладочным платам для аналогов Xilinx Kintex-7 от китайских производителей. В процессе вебинара будут рассмотрены аналоги Kintex-7 китайского производства и продемонстрирована работа с соответствующей отладочной платой. Будут рассмотрены проблемы и сложности, которые могут возникнуть в процессе применения китайских ПЛИС, и возможные пути решения этих проблем. Подробнее

-

Прошивка ПЛИС с помощью МК

mysol опубликовал тема в Работаем с ПЛИС, области применения, выбор

Друзья, здравствуйте! Подскажите, пожалуйста, можно ли заливать прошивку в ПЛИС из флеш памяти контроллера? Какие используются механизмы? Нет ли примеров/туториалов? В частности в Cyclone 10 LP. Спасибо! -

Компания AMD Xilinx официально объявила о продлении поддержки всех ПЛИС 7 серии и адаптивных СнК до 2035 года. Это включает все классы скорости и температуры для ассортимента СнК Zynq ®-7000 , а также ПЛИС Kintex®-7 и Virtex®-7. Подробнее

-

- zynq-7000

- kintex ultrascale

- (и ещё 4 )

-

Здравствуйте, уважаемые форумчане! Синтезирую простейший модулятор DPSK в Quartus Prime 16.1 SE. Возникла проблема при симуляции кода посредством ПО Modelsim - IP ядро NCO Modelsim отказывается симулировать. Вот код и текст ошибки: "Warning: (vsim-3722) <protected>(<protected>): [TFMPC] - Missing connection for port '<protected>'." "Warning: (vsim-3017) <protected>(<protected>): [TFMPC] - Too few port connection. Expected <protected>, found <protected>." Предварительно в проект квартуса потянул файлы NCO.sip и NCO.qip, т.к. без них симуляция вообще не запускалась. Возможно ли решить проблему или на пресловутый косинус я никак не посмотрю?

-

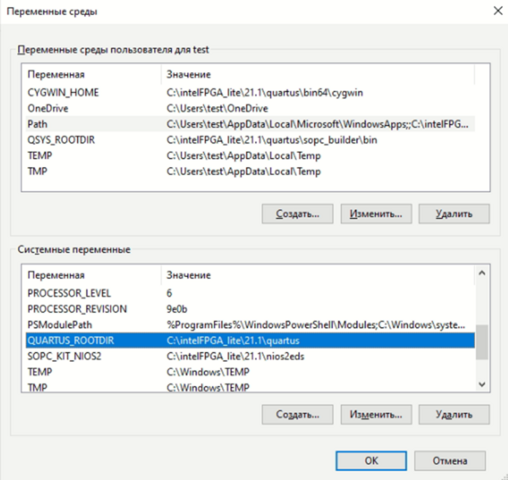

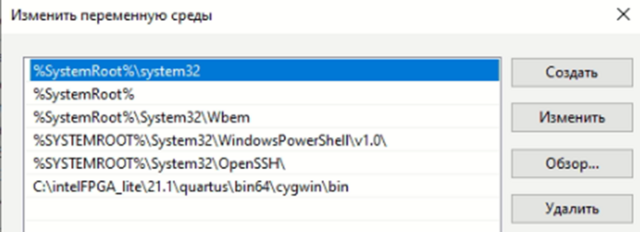

Добрый день! Уважаемые господа, очень прошу Вас проявить снисхождение к моему невежеству в вопросах ПЛИС. Ранее с ПЛИС не работал, о командной строке знаю только то, что она есть как таковая. Так случилось, что мне необходимо провести диагностику карточки, но получаю постоянно ошибки. Часть из них решил гуглением, дальше мои полномочия всё. Имеем: -DE5a-Net-DDR4 -Материнская плата Terasic Arria 10 GX FPGA При попытке запуска test.bat с тестами трансиверов в терминале cygwin получаю ошибку следующего содержания: Содержимое тестового test.bat файла: Содержимое файла test.sh: Переменные среды. Инфу записывал исходя из найденной в интернетах. Path: Папка установки Cygwin нестандартная, т.к. в test.bat прописаны пути именно в эту папку C:\intelFPGA_lite\21.1\quartus\bin64\cygwin Иначе не находил Cygwin. И собственно файл nios2-download во вложении. Ошибка в строке 531. Буду рад любой помощи! Спасибо Вам огромное! test.bat test.sh nios2-download

-

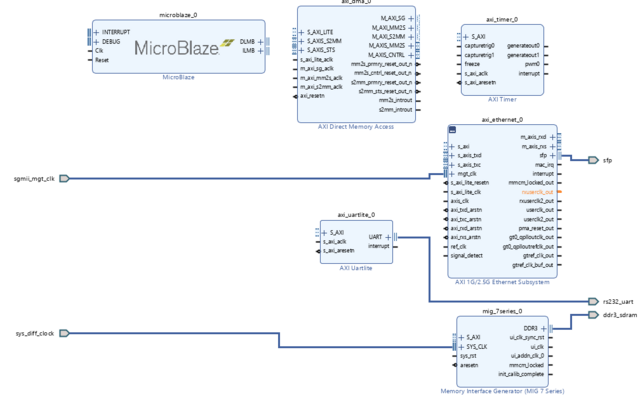

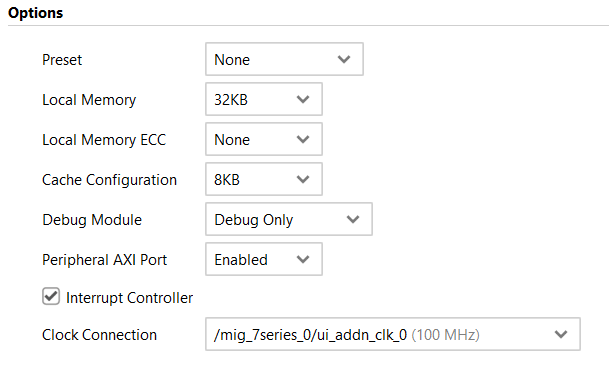

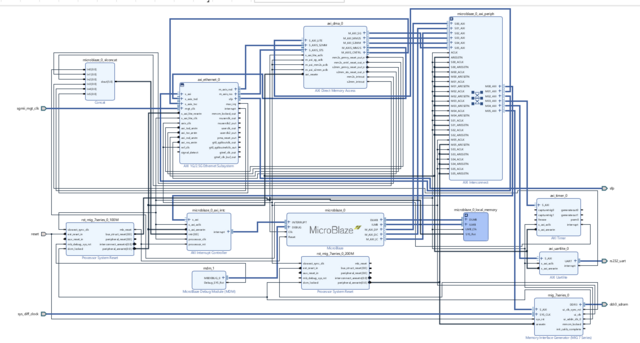

SFP проект в vivado

mixa7109 опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

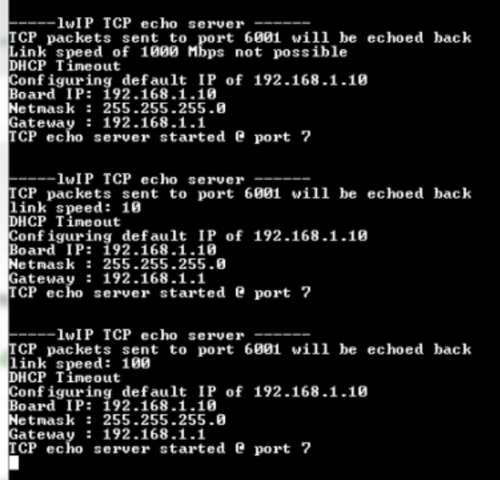

Всем добрый день, пытаюсь создать простой проект для работы с SFP и microblaze. Для microblaze используется прошивка: lwIP Echo Server. Проект учебный на отладочной плате Xilinx Kintex-7 FPGA KC705 Проектик делаю по этому гайду: https://numato.com/kb/gigabit-ethernet-example-design-using-vivado-for-mimas-a7-fpga-development-board/ Используются следующие модули: 1. MicroBlaze 2. AXI DMA 3. AXI 1G/2.5G Ethernet Subsystem 4. MIG 5. UART 6. Timer Все между собой соединяется, но на фото и не разберешь, слишком много соединений Все в сборке выглядит так: Все собирается, но сама прошивка не заводится. Даже в консоль ничего не выдается, я делал на другой платке обычный ethernet и там все работало. А ожидалось что-то типо такого: Но на выходе тишина. Причем, если запустить этот же проект, но с прошивкой на тест памяти, то все работает. Даже и не пойму, где может быть ошибка и что не так..... Проверял сами порты SFP через IBERT и тест был пройден. -

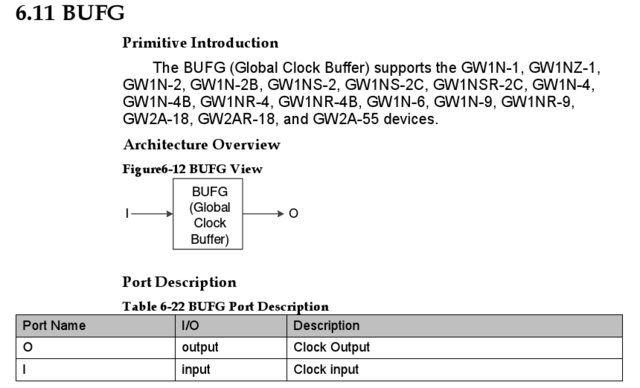

Всем привет! Имеется ПЛИС GW1NR-LV9QN88PC6/I5 (Tang Nano 9K). В документации от Gowin (SUG283-1.5E, 11/15/2018) указано наличие примитива BUFG: Я инстанцирую его в модуле верхнего уровня и в нетлисте после синтеза он ожидаемо присутствует. Однако в сгенерированном после pnr файле vo его нет. Нет его и в путях прохождения тактового сигнала Timing Analyzer. Т.е. складывается впечатление, что этот примитив BUFG на самом деле не существует на кристалле ПЛИС. Или я что-то делаю не так? Если использовать в качестве входов тактовых сигналов пины GCLKT, то проблем нет и ругани в PNR на эту тему тоже нет. Но мне интересен вариант использования глобального буфера, на вход которого сигнал подаётся не с выделенного пина, а с любого другого. Я понимаю, что это даёт дополнительную задержку, но в ряде случае это допустимо и может быть даже вполне оправдано. Получается, что такой вариант с Gowin невозможен?

-

Всем привет. Много работал ранее с проектами в среде QUARTUS, очень часто приходилось отлаживать проекты в железе при помощи встроенного логического анализатора Signal Tap II. Очень удобный инструмент, ни один раз помогал мне найти и выявить ошибки, пропущенные на стадии моделирования и некоторые моменты, которые моделирование в принципе не способно обнаружить. В данный момент создаю проект в Xilinx Vivado, где на ПЛИС принимаю по JESD отчёты из АЦП, провожу некоторую обработку данных и кладу в память. Столкнулся с ситуацией, что на модели всё идеально, никаких проблем нет, но в железе не работает должным образом моя внутренняя логика (при этом приём сигнала с АЦП по JESD в норме). Стал разбираться, с помощью ядер ILA выводить интересующие меня сигналы JESD, флаги и статусы для анализа. Первая проблема, с которой я столкнулся, не могу завести ядра на частоте, которой изначально нет в ПЛИС (в момент подачи питания). Частота появляется с программируемого генератора позже и САПР Vivado говорит мне, что не может запустить ядро ILA и показать результаты... Пришлось перебрасывать все нужные мне сигналы через три регистра на стабильный клок (от DDR у меня есть 300МГц, которые всегда поступают в ПЛИС). ILA запускается, но тут начинается танец с бубном. У меня либо совсем умрёт JESD, что перестают корректно приниматься данные, либо работает но данные бьются. Причём бьются не те данные, которые я вывел на ILA, а реальные отчёты АЦП, поступающие в память. Лечится эта штука путём полного сброса проекта (команда "reset_project" TCL) и 1-2 перекомпиляции, не меняя исходников или настроек. В итоге этот процесс очень сильно стопорит процесс отладки. После каждых изменений в проекте, приходится танцевать с бубном и надеяться, что после 2-3 перекомпиляций проект получится рабочий, JESD запустится и ILA ему мешать не будет. Прошу помощи у более опытных пользователей. Как вы работаете с ILA? Как тестируете работоспособность проекта в железе на xilinx?

-

Переход с Altera на Gowin

GDS опубликовал тема в Предлагаю работу

Добрый день. Ищем программиста ПЛИС. Территориально находимся в г. Лобня. Необходимо осуществить переход с Altera 10M08SAE144 на Gowin. На альтере код полностью отлажен, есть все исходники, вся документация. Заинтересовавшихся прошу писать на [email protected] или на [email protected]