Поиск

Показаны результаты для тегов 'fft'.

-

Simulink complex fft

Lavash опубликовал тема в Вопросы системного уровня проектирования

Добрый вечер, нужно смоделировать бпф комплеканого сигнала, используя симулинк. Какой тулбокс лучше использовать? Какой-то из встроенных, или есть что-то получше? -

Xilinx FFt Core v7.1 ISE 12.4

Lavash опубликовал тема в Работаем с ПЛИС, области применения, выбор

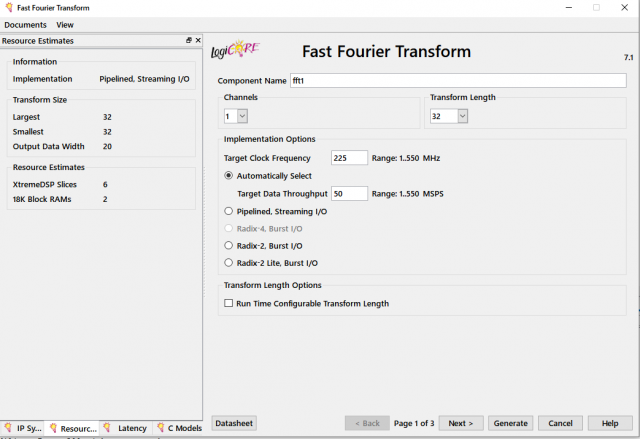

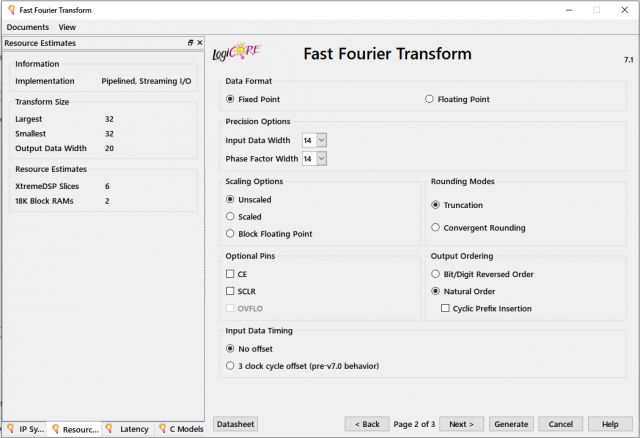

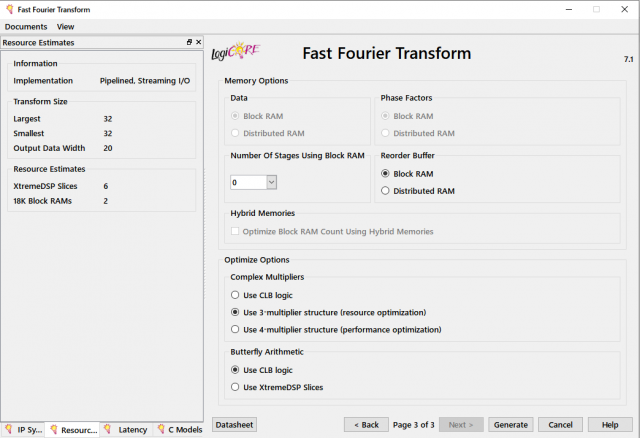

Помогите разобраться! Сгенерировал в проекте ядро со следующими параметрами: Сделал тестбенч, используя счетчик clk с периодом импульсов 4.444 нс(225 МГц). Насколько я понимаю, на вход нужно подавать 14ти битные числа, но не совсем понимаю, какие биты отвечают за целую/дробную часть. Возникает несколько вопросов: как должен выглядеть пример входного числа? Как интерпретировать полученные значения? -

Zynq-7000 или Shark+ FFT

Ozone опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте! Помогите определиться в какую сторону смотреть. Задача: Оцифровка сигнала частотой до 20МГц, затем фильтрация, FFT 1024 точки, анализ спектра, повторение операции. Реалтайм не требуется, то есть между окнами выборки FFT могут быть пропуски, но в общем, чем чаще, тем лучше. До этого опыта работы с DSP, Schark, FPGA, Linux не было, только STM32H7. Для этой задачи отлично подходят Shark+ со встроенными аппаратными ускорителями FFT, FIR. Также Zynq-7000 отличный кандидат. FIR / FFT на FPGA, последующая обработка на ARM. Как вижу, Schark очень хорошо подходит по железу и стоимость его низкая. Но смущают следующие моменты: нет дешевых отладочных плат, комюнити практически нулевое, никаких видео, форумов, обсуждений. Zynq-7000 на порядок хайповее, как я понимаю ответы на вопросы намного легче будет найти, полно дешевых отладочных плат. Но потребуется согласование FPGA и ARM части, работа в линуксе. Еще преимущество в том, что решение более гибкое,так как в следующих проектах FPGA будет нужна. Подскажите, какой вариант должен занять меньше человеко-часов на разработку с нуля и на чем бы реализовали данную задачу вы? -

Доброго времени суток, уважаемые форумчане. Балуюсь с ядром ПФ в Vivado. Ядро сконфигурировано следующим образом: - размер - 8192 точки. - Тактовая - 100 МГц. - Сэмплинг - 100 Msps. - Без масштабирования (Unscaled). - convergent rounding. - натуральный порядок вывода. В качестве тестового сигнала использую сумму двух комплексных экспонент, однак на выходе модуля получаю паразитные гармоники (см. рис.). Причем, мнимая часть более ли менее похожа на правда, а шум появляется именно в реальной части. Чем это может быть вызвано и как с таким бороться? На сколько правильно вообще у меня сконфигурировано ядро? Заранее благодарен за ответы. Код модуля: module tb_xfft(); reg CLK = 0; always #5 CLK = ~CLK; wire [31:0] signal1, signal2, signal; wire signal1_valid, signal2_valid, signal_valid; assign signal_valid = signal1_valid & signal2_valid; dds_out16 inst_dds_out16( .aclk(CLK), .m_axis_data_tdata(signal1), .m_axis_data_tvalid(signal1_valid) ); dds_out16_3M inst_dds_out16_3M( .aclk(CLK), .m_axis_data_tdata(signal2), .m_axis_data_tvalid(signal2_valid) ); wire signed [15:0] sin1, cos1, sin2, cos2, sin, cos; wire signed [16:0] ssin, scos; assign sin1 = signal1[31:16]; assign cos1 = signal1[15:0]; assign sin2 = signal2[31:16]; assign cos2 = signal2[15:0]; assign ssin = sin1 + sin2; assign scos = cos1 + cos2; assign sin = ssin[16:1]; assign cos = scos[16:1]; assign signal = {sin, cos}; wire fft_valid; wire [31:0] fft; wire new_fft; wire config_valid; reg [7:0] config_data = {7'b0, 1'b1}; xfft inst_xfft( .aclk(CLK),//aclk : IN STD_LOGIC; .s_axis_config_tdata(config_data),//s_axis_config_tdata : IN STD_LOGIC_VECTOR(31 DOWNTO 0); .s_axis_config_tvalid(config_valid),//s_axis_config_tvalid : IN STD_LOGIC; .s_axis_config_tready(config_valid),//s_axis_config_tready : OUT STD_LOGIC; .s_axis_data_tdata(signal),//s_axis_data_tdata : IN STD_LOGIC_VECTOR(31 DOWNTO 0); .s_axis_data_tvalid(signal_valid),//s_axis_data_tvalid : IN STD_LOGIC; //.s_axis_data_tready(),//s_axis_data_tready : OUT STD_LOGIC; //.s_axis_data_tlast(),//s_axis_data_tlast : IN STD_LOGIC; .m_axis_data_tdata(fft),//m_axis_data_tdata : OUT STD_LOGIC_VECTOR(31 DOWNTO 0); .m_axis_data_tvalid(fft_valid),//m_axis_data_tvalid : OUT STD_LOGIC; .m_axis_data_tready(1),//m_axis_data_tready : IN STD_LOGIC; //m_axis_data_tlast : OUT STD_LOGIC; .event_frame_started(new_fft) ); wire [15:0] fft_re, fft_im; assign fft_re = fft[15:0]; assign fft_im = fft[31:16]; wire [31:0] Re, Im; mult_16x16 inst_mult_re( .CLK(CLK), .A(fft_re), .B(fft_re), .P(Re) ); mult_16x16 inst_mult_im( .CLK(CLK), .A(fft_im), .B(fft_im), .P(Im) ); reg [32:0] Abs = 0; always @(posedge CLK) begin if (fft_valid) begin Abs <= Re + Im; end else begin Abs <= 0; end end endmodule

-

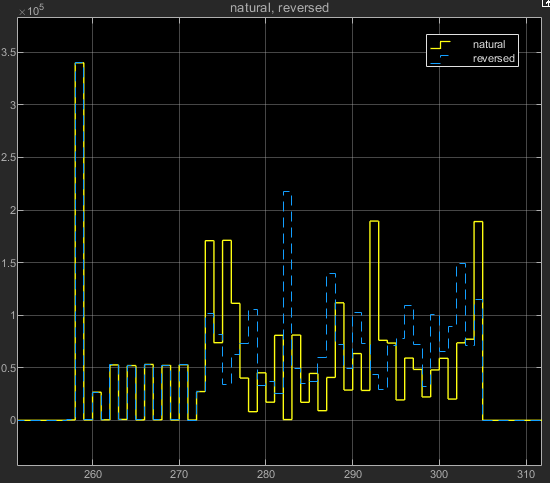

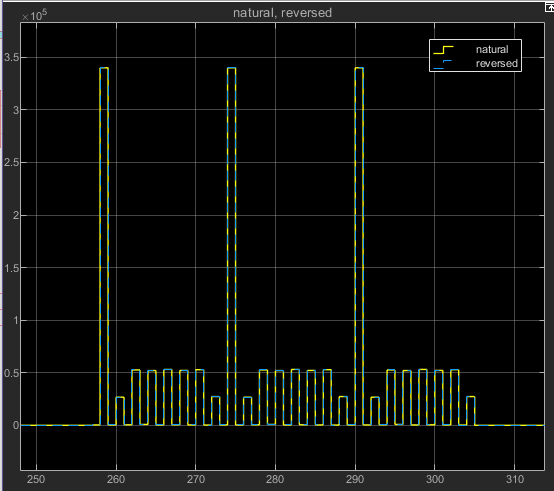

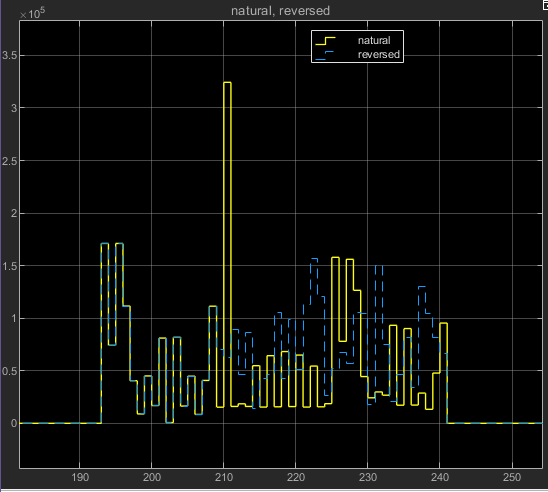

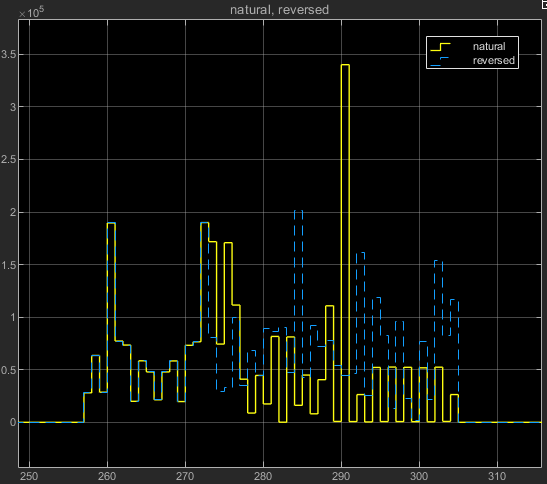

Привет! Вопрос по bit-reversed order для FFT, IFFT. Работает только в одном частном случае - при нулевом carrier offset. Не могу понять почему. Пытаюсь свернуть код Баркера в присутствии остаточной несущей. DSSS, вот это всё. Играюсь с моделькой, примерно такой: Всё нормально работает в Linear order (Natural order). Отклик проявляется на одном из бинов IFFT в зависимости от частоты биений остаточной несущей. Но, как только пробую bit-reversed order, работает только при нулевой остаточной несущей. При остальных нет отклика. Кроме того, отклики идентичны, если не делать циклический сдвиг перед умножением. Модельку прилагаю. fft_ifft_bit_reversed_order_a1.slx article_1.pdf