Поиск

Показаны результаты для тегов 'dac'.

-

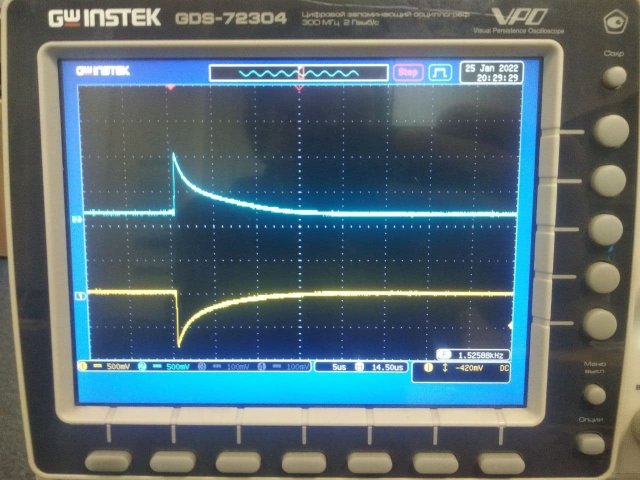

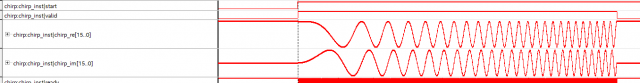

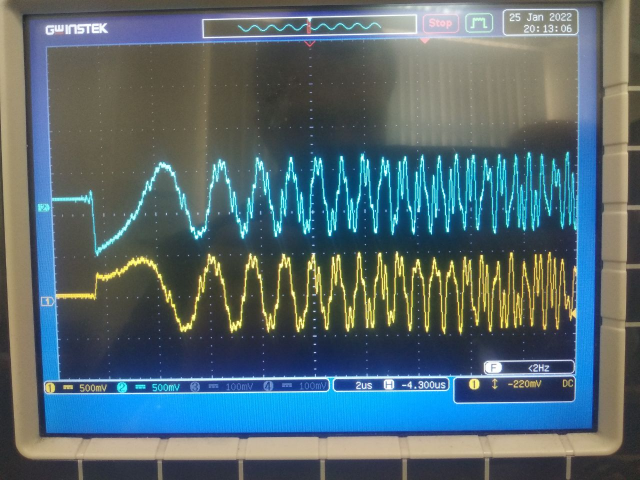

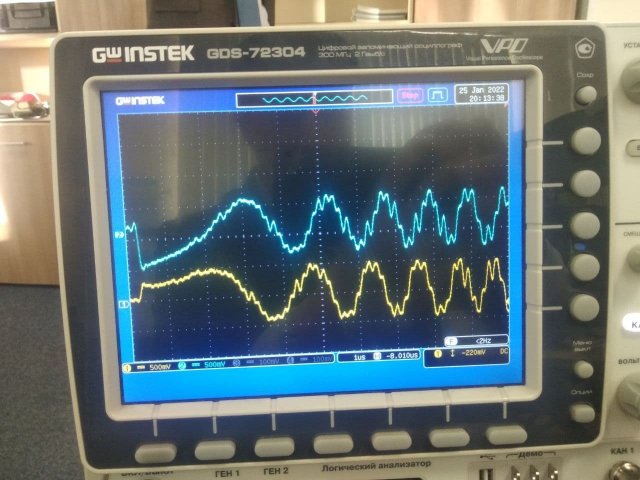

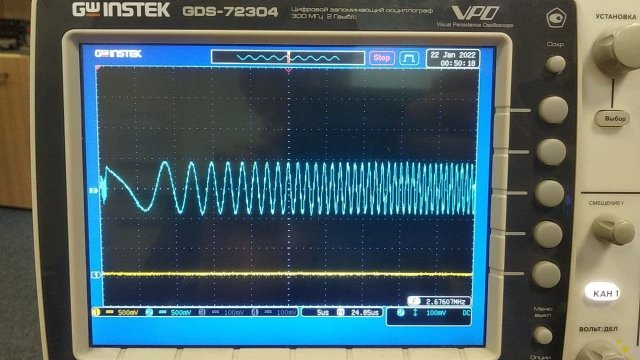

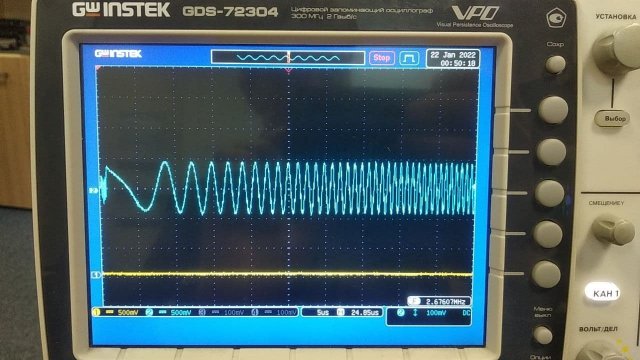

Здравствуйте, уважаемые форумчане необходимо генить синусоиду через ЦАП AD9122 на данный момент написан тестовый модуль, который генерирует ее вот в таком виде: Сделал IP модуль ЦАПа AD9122, который принимает 32х разрядные данные и затем в байтовом режиме выдает данные на ЦАП, причем реализацию сделал 2х модулей : 1. ALTDIO_OUT стоит только на данных, а DCLK и FCLK генятся через логику и выдаются на пинdac_ddr_phy_only_data_ddr.sv 2. ALTDIO_OUT стоит на данных, DCLK и FCLK, все тактируются от одного клокаdac_ddr_phy_all_ddr.sv написал констрейны: #************************************************************** # DAC_DDR #************************************************************** post_message -type info "READ dac_ddr.sdc" set dac_ddr_phy_clk { main_pll_inst|main_pll_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk } set Tco_max 0.65 set Tco_min -0.05 post_message -type info "CLOCK_FREQ_DCLK_HZ = $dac_ddr_phy_clk" post_message -type info "Output Max Delay = $Tco_max" post_message -type info "Output Min Delay = $Tco_min" # Create the external virtual PHY clock create_generated_clock \ -name dac_ddr_dclk \ -source [get_pins "$dac_ddr_phy_clk"] \ [get_ports {DAC_DIC}] #*********************** OUTPUT ************************* set_output_delay -clock [get_clocks {dac_ddr_dclk}] -max $Tco_max [get_ports {DAC_D*}] set_output_delay -clock [get_clocks {dac_ddr_dclk}] -min $Tco_min [get_ports {DAC_D*}] #*********************** GROUP ************************* set_clock_groups -exclusive -group [get_clocks {dac_ddr_dclk}] все пины определены, как LVDS_E_3R в Quartus на Си реализовал HAL уровень dac_ad9122.rar функция инициализации: - spi_dac_ad9122_setup_nav - без фильтров - spi_dac_ad9122_setup - с фильтрами, пример от AnalogDevices проблема в том, что генится с ЦАП вот такой сигнал: При это я использовал код инициализации ЦАП, который рекомендован AnalogDevices с включенными фильтрами, если просто настроить на байтовый режим с выключенными фильтрами, то картинка вот такая: неясно откуда берется эта пила, скорее всего искажение данных, но в каких битах или порядке байтов не могу понять.... При этом в самой схемотехнике перепутаны диaпары данных и FCLK при подключении к ПЛИС, я это решаю для: - 1го варианта модуля инвертированием данных до ALTDDIO_OUT, FCLK просто инвертирую на выходе - 2го варианта модуля инвертированием данных и FCLK до ALTDDIO_OUT пробовал запускать тест, чтобы проверить принимаемые данные ЦАПом 1. если генить DCLK постоянно, а данные и FCLK подставлять, когда данные валидны, то выдаются ошибки постоянно во всех битах 2. если генить DCLK только в сопровождении валидных данных, то ошибок нет, даже когда посылаю 0x0 в ЦАП и в Im и Qre, а в COMPARE REG записаны допустим 0xaa55aa55, если подать верные данные, то таже тема Пробовал кидать одиночные данные и смотреть их прямо на выходе ЦАПа, то видно что выдаются 2а импульса, хотя данные посылаю 1 раз, при этом со времянкой все верно сделано Пробовал выдавать счетчик, который считает от 0 до 0хFFFF, потом сбрасывается и опять считает, на каждый канал Im и Qre, при этом вижу следующее на осциле: Без фильтров: c фильтрами: синий луч Im, желтый луч Qre Не понятно, почему вообще выдает не нарастание линейное, а резкий всплеск по амплитуде и угасание по экспоненте Бьюсь уже 2ю неделю, пока мыслей нет, в каком направлении двигаться Может есть у кого пример реализации.... Буду рад любой помощи, спасибо

-

Разработка ПО (STM32, TMS320F28xxx, PIC, LPC)

C2000 опубликовал тема в Ищу работу

На время карантина ищу удаленную работу, дабы скомпенсировать денежные потери. Большой опыт в разработке как аппаратной части так и ПО. НО в данный момент приоритеты на стороне программного обеспечения, хотя если будет интересная (в смысле оплачиваемая) работа, то есть возможность разработки схем и трассировки PCB. Есть опыт работы с IDE: Eclipse, Keil, MPLAB, CodeComposer. Сейчас работаю в Eclipse + GCC, это среда разработки по умолчанию. Опять же если у заказчика есть жесткие требования, то можно будет использовать и другую среду разработки. Ради интереса не работаю, проекты на 2 часа (как бы) где 95% уже сделано, осталось всего 5% доделать тоже не интересны. Адрес для связи: [email protected] -

В двух словах. Во-первых, это мой первый опыт с Zynq, во-вторых, не могу уловить суть работы с потоковой шиной AXI-Stream. Или не понимаю сообщений от тайминг-аналайзера. Теперь подробней... Перед собственно запуском АЦП, наслушавшись как в Zynq все быстро и удобно, посмотрев несколько видео, и почитав несколько статей, создал простой проект, где Microblaze для конфигурирования в будущем АЦП и ЦАП, а ARM уже для работы с данными. Есть общая память между Zynq и Microblaze, есть общая периферия. Частота работа с периферией 50 Мгц. Раньше делал со стороны ARM 100 МГц, сейчас сделал поменьше. Не уверен, что выходную частоту процессорного ядра можно использовать в FPGA безболезненно, поэтому пропустил на всякий случай клок через Clock-wizard. Создал пару кастомных компонентов куда в дальнейшем перекочует работа с АЦП и ЦАП соответственно. И для проверки "скелета" все соединил и собрал. Сообщения про времянки уверяют меня, что ничего не работает. Пробовал вставлять регистры, вставил двухклоковую FIFO, опустил частоту работы с портом HP до смешных значений. Увеличил разрядность с 32 до 64 разрядов, завел два выхода в компоненте и использовал сразу два порта HP, помня рекомендацию Xilinx, что подключать нужно к портам через один, т.е. к 0 и 2 или к 1 и 3. Можно услышать от опытных людей критику по структуре проекта в целом и рекомендации по констрейнам? Я так понял, что как и для спартан-6 констрейны нужно прописывать только ко входной частоте, а производные клоки просчитываются автоматически. Тут также? Проект размещу по ссылке, т.к. его размер превышает ограничение в 5 Мб: EK-Z7-ZC702-G_Zynq_MB

- 19 ответов

-

- zynq

- microblaze

- (и ещё 4 )

-

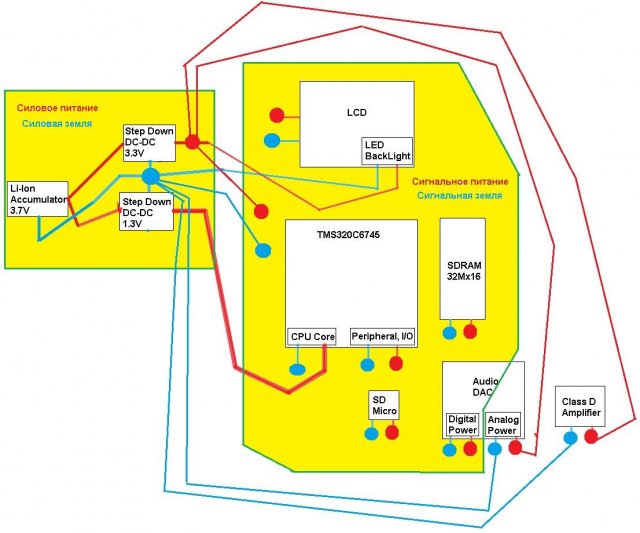

Добрый день. Думаю над правильной разводкой устройства, в состав которого входят: 1) ЦСП TMS320C6745, работающий на частоте 456 МГц, ток потребления ядра до 350 мА, напряжение питания ядра 1,3 V 2) SDRAM 32Mx16, работающая на частоте 152 МГц, напряжение питания 3,3V 3) Карта памяти SD micro, питание 3,3V, подключена по SPI 4) LCD со светодиодной подсветкой. Питание контроллера дисплея и светодиодов подсветки: 3,3V. Ток подсветки 60 мА. 5) Аудио-ЦАП, дельта-сигма. Питание 3,3V. 6) Усилитель звука, класс D, мощность в нагрузку 0,4 Вт (< 1 Вт), питание 3,3V. 7) Система питания: a) Понижающий DC-DC на 1,3V 800 мА - для питания ядра ЦСП б) Понижающий DC-DC на 3,3V 600 мА - для питания всего остального в) Первичный источник питания - аккумулятор Li-Ion 3,7V. Ток потребления всего устройства: от 180 мА до 320 мА. При поблочном макетировании устройства были замечены следующие вещи: 1) Питание для подсветки LCD надо брать с клемм DC-DC, иначе будут перепады яркости подсветки LCD из-за громкого звука 2) Питание на УНЧ надо брать с клемм DC-DC, иначе будут перепады яркости подсветки LCD из-за громкого звука и шумы в аудио-тракте. 3) Питание на аналоговую часть ЦАП надо брать с клемм DC-DC, иначе будут шумы в аудио-тракте и помехи от работы DC-DC. 4) Питание и земля от DC-DC конвертеров не должны проходить через сигнальные питание и землю, иначе ЦСП может уходить в Reset. Топологию в схематичном виде выкладываю - она выполнена с учетом всех пунктов выше. При таком исполнении подключения все узлы функционируют исправно, при длительном тестировании (более 2 ч.) сбоев замечено не было, аудиотракт без шумов, подсветка без видимых на глаз перепадов яркости. Прошу обсудить: укажите на ошибки; дополнения, исправления и улучшения приветствуются! Располагаю макетом - могу проверить на практике любое предложение!

- 50 ответов

-

- правильная разводка

- c6745

-

(и ещё 6 )

C тегом:

-

Есть необходимость создания проекта под Artix в Vivado: АЦП -> ФНЧ -> ЦАП Цель - на простом проекте отработать навыки работы с констрейнами в Vivado. Вводные: АЦП - выходы LVDS, тактовая данных (64МГц) - тактируют плис ФНЧ - КИХ на частоте 384 МГц ЦАП - КМОП 32 МГц Пока пытаюсь сделать упрощённый вариант - генерировать синус на ЦАП по 16 точкам. Вопрос 1 У меня есть ноги CLK64_P и CLK64_N, из них я создаю клок CLK64 методом: Удивлён, что констрейн на клок приходится задавать для CLK64_P а не для CLK64, это правильно? #create_clock -add -name sys_clk_pin -period 15.625 -waveform {0 7.8125} [get_ports { CLK64_P }]; сколько цифр после точки можно вводить? Vivado понимает 7.8125 или округлит до 7.81? Вопрос 2 Мне нужны частоты 384МГц и 32МГц, 384МГц получаю так: Мне надо прописывать констрейн на клок CLK384 или Vivado сам поймёт что он и всё что от него тактируется работает на частоте 384МГц? Вопрос 3 Как лучше получить частоту 32 МГц - своим счётчиком или с PLL? Вопрос 4 Счётчики в Vivado оптимизируются? В ISE я брал 32 разрядный регистр, делел на нём 3 разрядный счётчик и при синтезе у меня старшие разряды отбрасывались и получался 3 разрядный счётчик в Vivado я что-то этого не замечаю, он что пытается развести 32 разряда? Вопрос 5 Как передавать данные между блоками работающими на частотах 64, 384, 32 МГц - напрямую или ставить регистры типа FIFO для надёжности? Вопрос 6 Хочется сделать выходные и входные триггеры и разместить их рядом с ножками - как это описать в констрейнах и как задать время запаздывания/распространения? Вопрос 7 Файл .xdc - один на проект или можно создать некую иерархию из .xdc файлов? констрейны только в .xdc? В верилоге сразу указать нельзя?

-

Как соединить ВЧ сигналы между платами

Skryppy опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Здравствуйте. У меня возникла проблема, прибор с ПЛИСами + куча ЦАП + ВЧ микросхем не умещается на одну плату, надо разбить его на две платы. Думаю оставить на одной плате цифровые микросхемы и ЦАПы, а на другую перенести ВЧ часть. Вопрос можно ли для передачи с платы на плату 75 Омного дифференциального сигнала с выхода ЦАП (AD9739) использовать мезонинные разъемы типа QFS–026–04.25–L–D–A (или подобные) или же нужно использовать коаксиальные ВЧ разъемы(как тогда выравнивать длину диф пар с кабелями?) ? Сами ЦАПы перенести на другую плату не получится, так как места для сотен диф-пар и разъемов для них тоже нет. Может быть есть какое-нибудь более простое решение? -

Драйвер RGB панели

Aldec опубликовал тема в Работаем с ПЛИС, области применения, выбор

Посоветуйте какие плис возможно использовать драйвером панели

.thumb.jpg.d0ede0a2f08d2628b97a8335de59a919.jpg)