Поиск

Показаны результаты для тегов 'cyclone v'.

-

Куплю terasic de10-nano

BeetRootRage опубликовал тема в Куплю

Куплю отладочную плату terasic de10-nano (б/у или новую) -

Куплю terasic de10-standard

BeetRootRage опубликовал тема в Куплю

Куплю отладочную плату terasic de10-standard (новую или б/у)- 1 ответ

-

- fpga

- de10-standard

-

(и ещё 3 )

C тегом:

-

Всем привет. Вопрос по поводу состояния выводов после включения питания на Cyclone V. В даташите по этому поводу нашел только то, что можно включить подтяжку к питанию (weak pull-up resistor), pull-down можно включить только для JTAG TCK. Так же приведены значения внутренних подтягивающих резисторов до и во время конфигурации (25 кОм). Значит ли это, что после первого конфигурирования ПЛИС соответствующей прошивкой подтягивающие резисторы будут работать при подаче питания до окончания конфигурирования? На всякий случай текст из даташита: А вообще должны ли выводы до завершения конфигурирования находится в Z-состоянии? А то что-то больше походе на то, что идет подтягивание к VCCIO

-

Здравствуйте! Возникла проблема с прошивкой Cyclone V (платы DE0-Nano-SoC и DE1-SoC), включающей Nios II. Заливка на пустую ПЛИС производится спокойно, но если на ней уже работает Nios II (с залитой прошивкой), то программатор в Квартусе выдаёт ошибку. В итоге всё решается только отключением и включением питания. Причём, даже зажатая кнопка reset (для Nios) не помогает. Причём, если Nios есть, но не залита его прошивка, то ПЛИС нормально перепрошивается. Подскажите, пожалуйста, в чём может быть проблема?

-

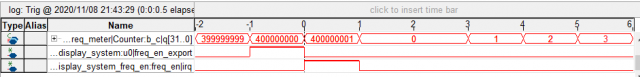

Здравствуйте! Делаю частотомер на ПЛИС (Cyclone V на DE0-Nano-SoC) с выводом на дисплей значения частоты. Рассчитанное значение частоты выдаётся (обновляется) каждую секунду, вместе с ним поднимается сигнал переполнения счётчика (на один такт). Поскольку вывод осуществляется через Nios, использую прерывание по уровню (ядро PIO) для регистрации сигнала переполнения и в обработчике вывожу значение частоты на экран. Код инициализации прерывания: static void init_freq_en_IRQ() { alt_putstr("irq_init start\n"); void* edge_capture_ptr = (void*) &edge_capture; IOWR_ALTERA_AVALON_PIO_IRQ_MASK(FREQ_EN_BASE, 0xf); alt_ic_isr_register(FREQ_EN_IRQ_INTERRUPT_CONTROLLER_ID, FREQ_EN_IRQ, handler_freq_en, edge_capture_ptr, 0x0); alt_putstr("irq_init finish\n"); } Код обработчика: static void handler_freq_en (void * context) { IOWR_ALTERA_AVALON_PIO_IRQ_MASK(FREQ_EN_BASE, 0x0); IOWR_ALTERA_AVALON_PIO_IRQ_MASK(FREQ_EN_BASE, 0xf); freq_to_lcd(); alt_putstr("handler\n"); } Но почему-то при запуске прерывания генерируются, но процессор в них не уходит. Скрин SignalTap'a. Верхний сигнал - это счётчик, отмеряющий секунду, средний - сигнал переполнения, нижний - вроде как генерируемый сигнал IRQ из контроллера PIO (по крайней мере он исчезает, когда я отключаю инициализацию прерывания) При этом в один момент он зависает и прекращает выполнение основной программы (Это выяснилось после того, как я сделал отправку на дисплей в бесконечном цикле в функции main). Есть подозрение, что он уходит в прерывание, но не доходит до обработчика (он не выполняется), или же это какое-то другое исключение, из которого он не возвращается. Что это может быть? Может, я неправильно настраиваю прерывания (с прерываниями по фронту всё работало, но там была другая проблема)? Или, если проблема в другом исключении, как это отследить? Ссылка на гитхаб (в папке DE0_Nano_SoC_project) UPD: Посмотрел на сигнал IRQ при прерывании по фронту. Там он находится в положении 1 до момента сброса прерывания. Здесь же почему-то всего один такт

-

- de0-nano-soc

- cyclone v

-

(и ещё 2 )

C тегом:

-

Настройка LVDS на Cyclone V

Петр Юркевич опубликовал тема в Программирование

Здравствуйте! Стоит задача генерировать внутри ПЛИС Altera Cyclone V (кит Terasic DE1-SoC) при помощи PLL некоторую частоту, передавать её на выход LVDS и принимать на другой вход этой же ПЛИС (необходимо для отладки частотомера). По поводу LVDS долго пытался вчитываться в Cyclone V Handbook, но понял только то, что надо использовать функции Квартуса для приёма и передачи сигнала LVDS. Насколько я понял, при назначении в Pin Planner стандарта LVDS Квартус сам назначает пару выбранному пину. Информацию по поводу пар дифференциальных пинов нигде не смог найти. Я выбрал GPIO[12] и GPIO[14] (парные 15 и 13). Дальше создал входной и выходной буферы (ALTIOBUF), которые должны преобразовывать сигнал из моно в дифференциальный и обратно. LVDS_BUF_IN lvds_in ( .datain(GPIO[15]), .datain_b(GPIO[12]), .dataout(clk_in) ); LVDS_BUF_OUT lvds_out ( .datain(clk_0_2), .dataout_b(GPIO[13]), .dataout(GPIO[14]) ); По поводу выходной пары у Квартуса вопросов не возникло, а на входные пины вылезла ошибка: Error (169008): Can't turn on open-drain option for differential I/O pin GPIO[12]. И аналогичная на 15-й пин. Если не создавать буфер, на выходную пару вылезает такая же ошибка, я читал, что Квартус не пропускает неправильно настроенные пины LVDS. Я знаю, что в LVDS должен быть на входе резистор между линиями. Может быть, ошибка из-за его отсутствия в программе? И его как-то настроить надо в самой ПЛИС? -

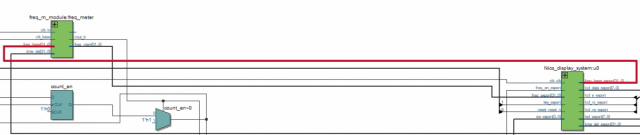

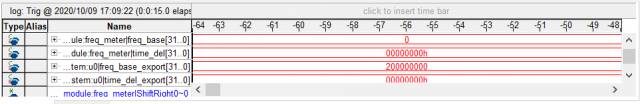

Здравствуйте! Делаю частотомер на ПЛИС (DE0-Nano-SoC, Cyclone V). Мне необходимо выводить значение измеренной частоты на внешний дисплей, поэтому было удобно подключить Nios, чтобы он этим занимался. Т.к. частотомер измеряет отрезок времени по некоторой опорной частоте, ему необходимо значение этой частоты, которое передаётся в модуль частотомера извне. Была идея реализовать поддержку изменения опорной частоты и интервала, на котором производится измерение, а также впоследствии возможность простого ввода этих значений (пока ввод реализован посредством переключения свитчей). Решил сделать это через Nios. Если с делителем интервала (деление посредством сдвига, поэтому по-умолчанию ставится 0) проблем не возникло, то с передачей значения опорной частоты (точно такого же формата, что и делитель) из Nios в частотомер возникла непонятная мне проблема: Выход Nios соединяется с соответствующим входом частотомера прямым проводом, который (судя по схеме Квартуса) ничем не делится. Но когда я всё запускаю и прошиваю Nios, он выставляет на выходе значение 200_000_000 (Гц). Но если посмотреть по SignalTap'у, то оказывается, что на выходе Nios правильное число (3я строка), а на входе частотомера 0 (1я строка), причём делитель передаётся нормально (здесь не видно, но если изменить на другое число, то на 2й и 4й строчках числа будут одинаковыми). В чём здесь может быть проблема? Проект находится на ГитХабе: https://github.com/FlexlabCompany/frequency_meter_Nios_display Проект ещё содержит часть для DE1-SoC, но здесь он используется только как сторонний генератор измеряемой частоты.

- 4 ответа

-

- nios ii

- de0-nano-soc

-

(и ещё 1 )

C тегом: