Поиск

Показаны результаты для тегов 'altera'.

-

Привет всем! У меня накопилось много редких микросхем. Сам электроникой не занимаюсь, только продаю её. Это излишки, которые накопились за какое-то время. Все детали новые, не распечатанные. Продаю как частное лицо, готов отдать каждое наименование ниже рынка, все цены по согласованию. Во вложении перечень. Если кому-то что-то интересно, пишите в личку. Излишки.docx

-

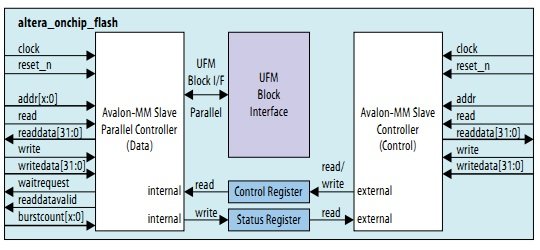

Всем привет, ковыряюсь с ПЛИС Max10 от Интела. Копаю корку Altera On-Chip Flash, которая позволяет в менять файл конфигурации находу, не используя JTAG. Грубо говоря самостоятельно себя перешивать. Структурная схема доступа к корке - на картинке. Если читать или записывать 32-х битное слово на шине writedata[31:0] блока Data и сравнивать данные с RPD-файлом, то оказывается что если брать данные по 4 байта из RPD-файла и записывать их на writedata[31:0] блока Data, то это 32-х битное слово нужно переворачивать - младший бит нужно записывать самым старшим в writedata и т д... Причем если читать и записывать writedata[31:0] блока Control - то там все впорядке. И вот вопрос: - это особенности шины данных Avalon или это такой хитрый формат RPD-данных, что врядли...

-

Макро Групп – официальный дистрибьютор HiTech Global, производителя плат на ПЛИС Xilinx и Intel FPGA (Altera) Подробнее

-

- плис

- fpga xilinx

-

(и ещё 4 )

C тегом:

-

9 500 р. Starter Kit DK-START-3C25N https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/kit-cyc3-starter.html Кит в состоянии нового. На борту Altera Cyclone III емкостью 25K LUT 32 МБайт DDR SDRAM 1 МБайт SRAM 16 МБайт FLASH высокоскоростной разъем для внешних устройств Отличный набор для начала освоения ПЛИС c NIOS, либо ЦОС, т.к. можно подключить внешние быстрые АЦП/ЦАП.

-

constraints Вопрос по set_output_delay

CloneCD опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день. Столкнулся с отрицательным значением для Tsetup в документации на ЦАП AD9117. (Tsetup = -0.2 нс, Thold = 1.5 нс) В связи с чем возник вопрос, как всё-таки правильно задавать constrain'ы для внешних сигналов. Для выходных интерфейсов временные ограничения я задаю следующим образом (если принять разницу во времени распространения клока и данных по плате = 0): set_output_delay -clock {clock_name} -man Tsetup {port_name} -add_delay. set_output_delay -clock {clock_name} -min -Thold {port_name} -add_delay. Соответственно для AD9117: set_output_delay -clock {clock_name} -man -0.2 {port_name} -add_delay. set_output_delay -clock {clock_name} -min -1.5 {port_name} -add_delay. Смущает отрицательное Tsetup, что говорит о том, что данные на входе микросхемы должны быть установлены после прихода фронта, до 0,2нс (но можно и раньше). Тем самым минимальное время на которое должны установиться данные = Tsetup + Thold = 1.3 нс. Или я неправильно понимаю трактовку этого значения, и производитель указывает время Tsetup относительно фронта клока (т.е. если оно отрицательное, это значит что данные должны установиться за 0.2 нс до прихода фронта клока.), и тогда минимальное время удержания данных на шине должно быть = 1.7 нс. Сталкивался кто-нибудь с отрицательным Tsetup, и как правильно в таком случае задавать set_output_delay? -

Доработка прошивки MAX10 (Москва)

Conv опубликовал тема в Предлагаю работу

Имеется выполненный проект на MAX10 (трансивер), в котором требуется заменить полосовые фильтры на фильтры меньшего порядка. Всего 2 таких фильтра. Исходники и прочая необходимая информация предоставляются. Подробности - через личку. -

Передача данных по USB

Flip опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Подскажите пожалуйста! Обучаюсь на отладочной плате Altera. Задача следующая: нужно передавать постоянно данные по USB-порту, вроде написал программу, но передача данных не происходит. module bufer_forusb (Clk,f_data); input Clk; output [7:0] f_data; reg [7:0] bufs [0:15]; integer i; reg [7:0] f_data; initial begin i = 0; bufs[0] = 0; bufs[1] = 16; bufs[2] = 31; bufs[3] = 45; bufs[4] = 58; bufs[5] = 67; bufs[6] = 74; bufs[7] = 77; bufs[8] = 74; bufs[9] = 68; bufs[10] = 67; bufs[11] = 45; bufs[12] = 31; bufs[13] = 25; bufs[14] = 15; bufs[15] = 0; end always@ (posedge(Clk)) begin f_data = bufs[i]; i = i + 1; if(i == 16) i = 0; end endmodule -

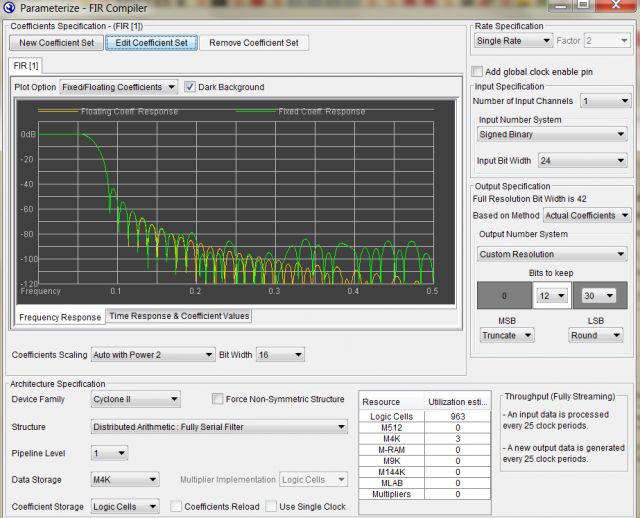

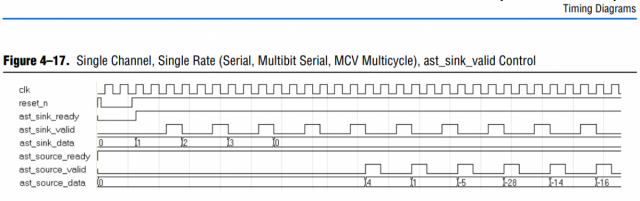

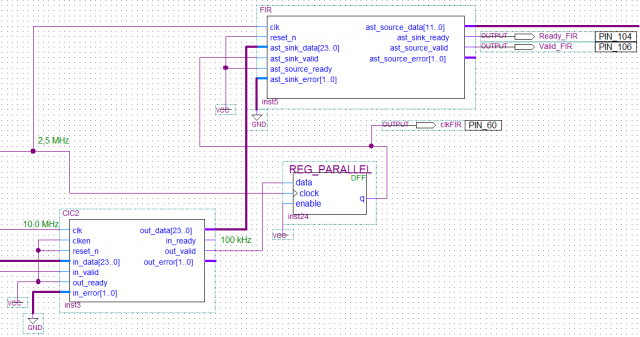

Добрый день уважаемые коллеги. В процессе разработки устройства (цифровой приёмник средневолнового диапазона) возникла проблема в конфигурации тайминга цифрового фильтра, при использовании соответствующей Мегафункции в Quartus 9.1. ПЛИС EP2C8Q208 (Cyclone II), КИХ фильтр 80 порядка, архитектура - Fully serial filter, single rate, входные данные - 24 бита (signed) с частотой 100 кГц. В FIR Compiler получаю 25 циклов CLK на один отсчёт. Согласно документа Fir Compiler User Guide устанавливаю CLK - 2,5 МГц, сигналы Reset и ast sink ready - лог."1", шина ast sink error - на земле, и ast sink valid сформировал через триггер - каждый 25-й отсчет CLK c длительностью в 1 период CLK (скважность 1/25 = 0,04) по сигналу valid от источника (CIC фильтр). Однако эти меры никак "не заводят" фильтр. При single cycle (вычисление отсчета за 1 CLK - c бешенным расходом LE) ast sink valid достаточно подтянуть к "1" и все работает... Может я что то неправильно понимаю в User Guide..? Заранее благодарен за любую помощь/пинок.

-

address_span_extender

Drakonof опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет, пожалуйста, уточните как работать с address_span_extender? Скажу сразу, я новичок. Есть DDR 1ГБ, у которой адресная шина 15 бит. Я полагаю что 2^15 = 32Кб = 8КБ. Окей, есть еще три бита выбора банка => 2^18 = 262Кб = 32КБ. Как мне адресовать весь гиг байт? Беру адрес_спан пишу что со стороны мастера мы можем адресовать 32б (это ширина авалона), а со стороны слэйва 15 + 3 = 18б (ширина шины адреса DDR + три бита выбора банков). Теперь вопрос, как мне двигаться по окнам памяти с помощью данного адрес_спан что бы адресовать всё пространство? PS. Читал даташит, смотрел видос, но как управлять этим ip я так и не понял. Может кто объяснит по человечески. Заранее спасибо! -

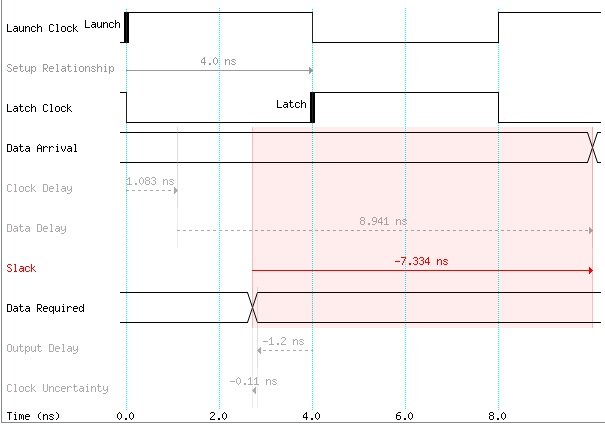

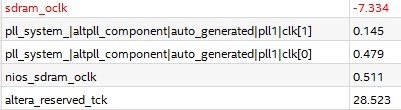

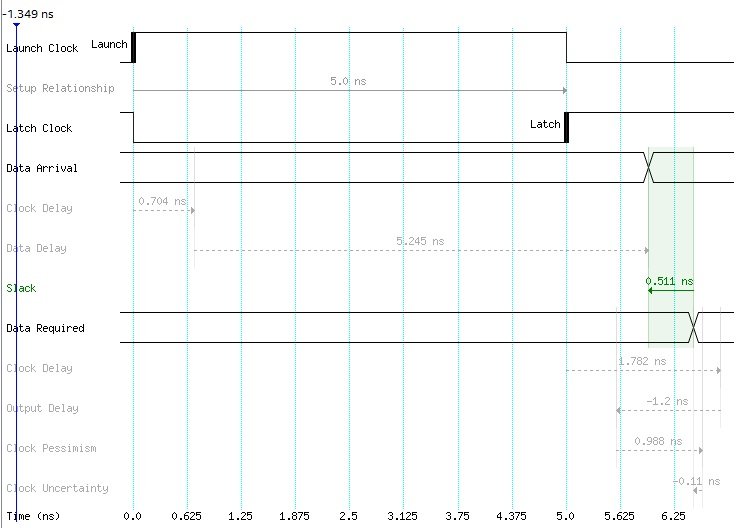

Здравствуйте, пишу свой первый проект на ПЛИС (verilog, max10), проект создаю в учебных целях. Создал систему в Qsys: nios, память(sdram), Jtag, и самописный компонент. Внутри самописного компонента, с просторов интернета контроллер памяти sdram(отдельно от памяти nios), счетчик и DCFIFO для передачи из счетчика на sdram. Nios запускает счетчик, тот в считает до оперделенного числа, и записывает в FIFO, оттуда контроллер sdram забирает данные и пишет в память. Nios и счетчик работают на 100Мгц, sdram и память на 125Мгц, FIFO двухклоковое на запись 100 Мгц на чтение 125 Мгц. На симуляции все работает отлично но в железе появляются проблемы констрейнов. В assigment поставил sdram выводам fast IO, клоки сделал Global Clock. Sdram для Nios работет timequest не ругается, а в моем компоненте постоянно ошибки памяти и я не могу понять почему такие большие слаки. Память микрон MT48LC16M16A2. На nios память микрон MT48LC4M32B2. Констрейны nios sdram Констрейны контроллера Общая картина: Клок Nios sdram Sdram внутри компонента. Не могу понять причину почему sdram внутри моего компонента так отличается от sdram используемого nios. Уже 2 недели бьюсь, может кто-то подскажет? Исходник компонента прилагаю. src.sv

-

Здравствуйте, пытаюсь соединить мастера с шиной 32 бита и слейв с шириной 128, мастер только читает. Подключены через pipeline bridge, скажите можно ли так настроить bridge чтобы на 4 чтения мастера приходилось 1 чтение из слейва, в симуляции по 4 чтения в слэйве пока мастер всю шину пройдёт,неужели в width adapter нет никакого fifo который решает эту проблему?

-

Эквивалентность РОМ мегафункции и кода

diwil опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте, уважаемве. Я в квартусе 18 создаю мегафункцию ROM - однопортовую, простую с инициализированой памятью. Квартус не хочет автоматически создавать ром в on-chip memory, за сим приходится использовать мегу. Потом я достаю данные из нее как: wire signed [32-1 : 0] coefsC; rom470 rom(caddr, clk,coefsC); always @(posedge clk) if (reset_n == 0) cc <= 0; else cc <= coefsC; и мне оч хочется это в модельсиме просимулировать. Я не знаю как квартуса мегу впихнуть в модельсим, за сим я пишу так: reg signed [32-1 : 0] coefsC [0:479]; initial $readmemh("coefs470.txt", coefsC); always @(posedge clk) if (reset_n == 0) cc <= 0; else cc <= coefsC[caddr]; Будет ли второй, "ручной" вариант, эквивалентен мегафункции в железе. Заранее благодарен- 12 ответов