Поиск

Показаны результаты для тегов 'adc 9208'.

-

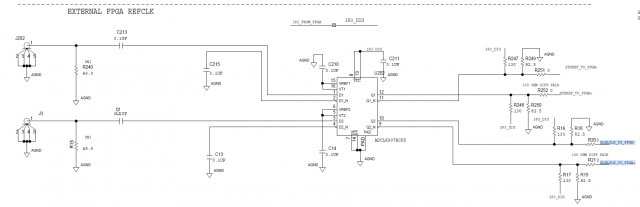

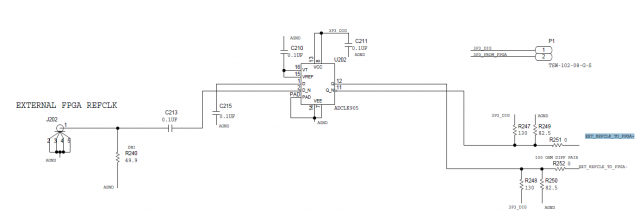

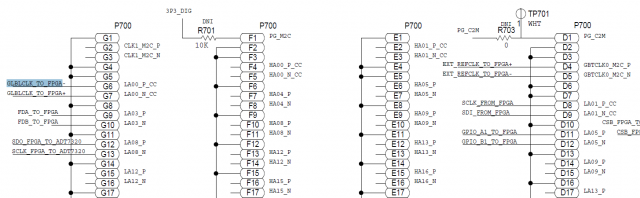

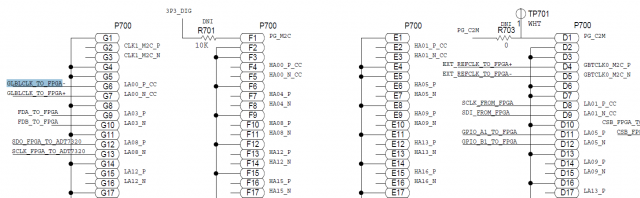

Всем привет. Успешно использовал для приёма в ПЛИС сигналов от мезонина AD9695 EVAL. Были свои минусы модели (не было возможности пропустить через FMC в ПЛИС сигнал sysref). Назрела необходимость использовать другой замечательный КИТ от Analog DEVICES - AD9208 3000EBZ EVAL. Посмотрел все необходимые характеристики, всё устраивает, даже появилась возможность сигнал sysref прогнать через мезонин и пустить в ПЛИС. Начал копаться более глубоко, нашёл схематик и там столкнулся с очень странным моментом. На моём старом ките, для работы трансиверов JESD можно было подать на входной коннектор SMA на мезонине сигнал "EXT_REFCLK_TO_FPGA" и пропустить его через FMC на ножку "GBTCLK0_M2C_P", после чего благополучно в ядре назначить его как PHY CLK для трансиверов (Рис.1). Рис.1 На новый КИТ AD9208 EVAl на сайте Analog DEVICES я скачал архив файлов, там был схематик для AD9689 EVAL, как я понял это совместимый пин в пин с моим АЦП и плата носитель у них одна. Так вот в скаченном схематике немного изменилась схема. Входной клок для ПЛИС с коннектора на мезонине теперь называется "GLBLCLK_TO_FPGA" (Рис.2) Рис.2 Подключается же данный сигнал на ножку "LA00_P_CC" на разъёме FMC (Рис.3), который не является высокоскоростным входом для тактирования трансиверов JESD ... Подключить его к JESD, я думаю, мне компилятор не позволит.. Интересно то, что старый сигнал "EXT_REFCLK_TO_FPGA" остался на старом "правильном" месте, но при этом он обрублен и больше никуда по схеме не идёт... Рис.3 Так вот мой вопрос. Это какая то опечатка, ошибка на схеме? Или реально так перелопатили КИТ, что теперь брать клок через мезонин невозможно? Приложу обе схемы: старого кита AD9695 и нового AD9208 (AD9689 так как это одно и тоже). SCH_9695ce01a.pdf SCH_9689ce02c.pdf