Поиск

Показаны результаты для тегов 'active-hdl'.

-

Подскажите, как запустить на симуляцию несколько модулей verilog в одном waveform в active-hdl?

-

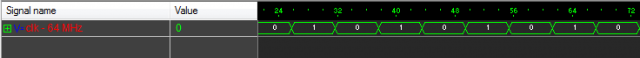

Всем добра. Продолжаю сражаться с Active-HDL-ем поминая добрыми словами ModelSim: Хочу отобразить меандр (тактовую частоту), имеющую в модуле имя, скажем, clk, но так, чтобы название сигнала шло с gояснением, например clk - 64MHz В ModelSime было просто: add wave -label "clk - 64MHz" dut_tb/clk А в Active-HDL-е самое близкое, что нашёл для "раскрашивания" имени - это add wave -virtual "clk - 64 MHz" /dut_tb/clk При применении которого waveform становится неудобоваримого вида: а я же хочу, чтобы он оставался меандром. Как всегда, просьба ткнуть носом в нужном направлении (сегодня копался полдня: не нашёл ни в интернете, ни в хелпе) Проект в скрепке. Active-HDL wave signal.zip

-

Tcl's if: ModelSim vs Active-HDL

MaratZuev опубликовал тема в Среды разработки - обсуждаем САПРы

Всем добра! Исполняю в командной строке ModelSim-а ModelSim> if {1} {puts "111"} Получаю, как и ожидал # 111 Исполняю тоже самое в командной строке Active-HDL-а: if {1} {puts "111"} Получаю # Error: missing endif for if in line 1 Причём всякие добавления endif в виде if {1} {puts "111"} endif Дают ту же самую ошибку. ЧЯДНТ?!- 3 ответа

-

- modelsim

- active-hdl

-

(и ещё 1 )

C тегом:

-

Active-HDL vs ModelSim batch mode

MaratZuev опубликовал тема в Среды разработки - обсуждаем САПРы

Всем добра! Всю свою сознательную жизнь сидел на Mentor-e, но пришла пора квалификации инструмента, для чего требуется сравнение результатов оного (ModelSim-a) с альтернативным ПО. Разумным решением представляется Aldec с его Active-HDL. Работая с ModelSim использовал его в основном в пакетном режиме, т.е. по запуску единственного командного файла, инициирующего обработку проекта, на выходе получал готовую временную диаграмму, которую потом успешно копировал в отчёт. Избаловавшись подобным подходом, захотелось применить оный и на новом инструменте, однако столкнулся с непреодолимыми (пока) для меня сложностями. Вопрос в следующем: возможно ли средствами Active-HDL проделать то же, что я проделывал с ModelSim? Есть ли у кого готовый пример этого (довольно подробный поиск в сети ничего, что дало хоть какие-то результаты, не принёс)? Для примера прилагаю свои изыскания, где я попробовал максимально подробно изложить своё видение маршрутов проектирования для упомянутых выше инструментов (для Active-HDL существует два маршрута, но ни на одном из них мне не улыбнулась удача): ЧЯДНТ? CompareDesignRoute.zip- 2 ответа

-

- active-hdl

- modelsim

-

(и ещё 1 )

C тегом: