Поиск

Показаны результаты для тегов 'плата'.

-

Выравнивание дифференциальных линий

Fillya опубликовал тема в Altium Designer, DXP, Protel

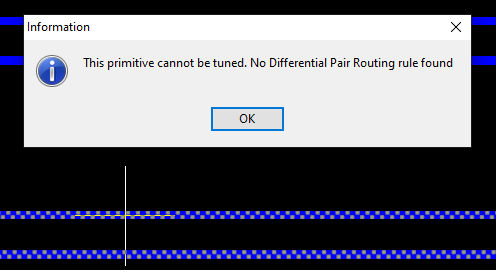

Доброго времени суток! При разводке дифференциальных линий возникла ошибка, которая не позволяет использовать опцию Interactive Differential Pair Length tuning. При попытке выделить дифф. пару такой опцией возникает поясняющее окно "This primitive cannot be tuned, No Differential Pair Routing rule found" хотя правила для разводки есть, более того их два для параметров дифф. линий на внешних и внутренних слоях, созданных для соответствующего класса. Также есть правило по максимальному разбегу длин этих линий, которое прекрасно отображается в окне PCB жёлтым цветом. Кроме того наблюдал такое явление - строго задан зазор, но в некоторых местах проводники могут сойтись на более близкое расстояние, по сути, нарушив правила, присвоенного для данного класса. В HyperLynx линии после экспорта считаются одиночными даже после присвоения им параметра DP в меню Setup и назначения моделей для дифференциальных интерфейсов (от имеющейся по умолчанию Virtex4.ibs). Кто нибудь встречался с такой проблемой? З.Ы. Был старый проект, эскизный. В нём вся плата работает (версия AD 15.0). Правила в нём были не все заданы, также не было отдельной сетки для одного из компонентов, из которого выходят линии. Других различий нет.- 6 ответов

-

- плата

- дифференциальная линия

- (и ещё 2 )

-

Сборка, детали, регулятор

Poison опубликовал тема в В помощь начинающему

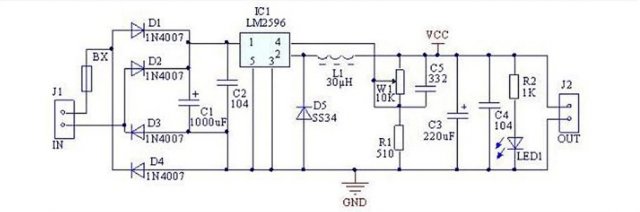

Приветствую всех! Решил познакомиться с миром сборки электроприборов. Заказал регулятор мощности напряжения постоянного тока. Однако понять что и куда нужно паять и что там за часть деталей понять не получается. Буду благодарен, всем, кто объяснит, что это за детали и куда их нужно паять. Фото прилагаются.- 7 ответов

-

- сборка приборов

- элементы питания

-

(и ещё 3 )

C тегом:

-

Куплю рабочую отладку BFK3.1, может у кого завалялась ненужная готов взять даже по цене чуть дороже официальной если будет подтверждение работы периферии.

-

- отладка

- отладочная плата

- (и ещё 3 )

-

Ниже описана текущая задача. Мы заинтересованы не только в решении текущей задачи, но и в последующем сотрудничестве по разработке новой платформы на базе покупной платы ZCU104/102, а также в последующем сотрудничестве по проектированию системы обработки сигналов (Verilog, Zynq). Текущая задача Есть ранее выпускавшиеся плата BemicroCV A9 (CycloneV), соединенная совместимым разъемом с платой Cypress FX3. Есть проект ПЛИС и прошивка FX3 для пересылки данных через USB в обе стороны (запись и проигрывание семплов на внешних пинах). Есть готовое приложение под Windows. Проблема Весь проект ПЛИС (CPU Nios для буферизации потока в DDR3 и интерфейс GPIF II с FX3) работает правильно на тактовой частоте 25 МГц. Начиная с 27МГц, возникает дублирование данных, начиная с 500МБ в разных местах. Хотя по оценке Квартуса этот проект может работать до 83Мгц. Задача При наличии всех исходников разобраться и локализовать при отладке, в какой точке происходит дублирование данных при передаче. Сделали ли бы сами, но не хватает времени и сил. Только Петербург, гибкий график. Если предложение и задачи вас заинтересовали, отправьте свое резюме на адрес [email protected] Бюджет не ограничен в пределах разумного, резюме с указанием пределов разумного будут рассмотрены с особым вниманием :)

-

Есть платы, после длительного хранения (примерно 0,5-1 год) они плохо паяются. Покрытие HAL (горячее лужение). Поиском искал, но нашёл только рекомендацию обработать лимонкой или аспирином, но это активные флюсы и после них нужно очень тщательное отмывание, может есть народный метод попроще.

-

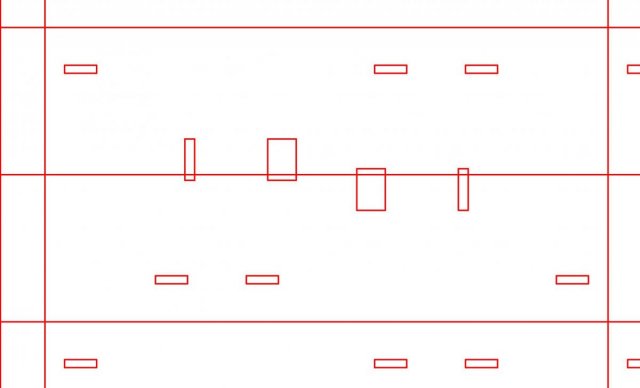

Здравствуйте, уважаемы Коллеги.Понадобилось разработать групповую заготовку плат, на которых есть краевые разъёмы. Разделение плат - скрайбированием.Для разъёма требуется сделать вырезы в плате (фрезерованием), вырезы должны заходить на соседнюю плату, чтобы получить прямые углы. При этом получается что контуры платы для разделения скрайбированием пересекаются с контуром выреза. Заход на соседнюю плату не имеет значения - печатные проводники далеко. Как показать правильно? Прикрепил фрагмент контура платы, 4 пересекающиеся вырезы на рисунке посередине.Спасибо.

-

Имеется не большая плата устройства - автомобильный компонент. Имеется схема оригинала. Скопировать плату, внести указанные изменения, разработать необходимую документацию. Подробности в ТЗ после обсуждения.

- 5 ответов

-

- плата

- разработка

-

(и ещё 1 )

C тегом: