Поиск

Показаны результаты для тегов 'верилог'.

-

очередь на верилоге

nopak опубликовал тема в Языки проектирования на ПЛИС (FPGA)

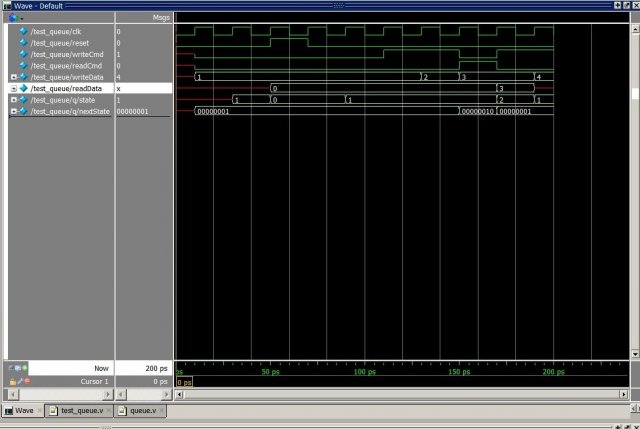

Написал очередь на верилоге. Ни как не могу понять почему она так себя ведёт. Почему были пропущены начальные данные. Результаты в присоединённой картинке. Помогите разобраться очередь module queue #( parameter N = 8, // разрядность данных count =16 ) ( input rst, input clk, input nextRead, input writeCMD, input reg [N-1:0] dataIn, output reg [N-1:0] dataOut ); reg [N-1:0] posRead; reg [N-1:0] posWrite; reg [N-1:0] state; reg [N-1:0] nextState; localparam RESET =0; localparam IDLE = 1; localparam WORK = 2; reg [N-1:0] data[count-1 : 0] ; //always @(posedge clk) always @* begin case (state) RESET: begin nextState = IDLE; posWrite = 0; posRead = 0; dataOut = 0; end IDLE: begin if (writeCMD) begin posRead = posWrite; nextState = WORK; data[posWrite] = dataIn; posWrite = posWrite + 1; end else begin end end WORK: begin if (writeCMD) begin nextState = WORK; data[posWrite] = dataIn; posWrite = posWrite + 1; end if (nextRead) begin dataOut = data[posRead]; posRead = posRead + 1; if (posRead == posWrite) nextState = IDLE; end end default: nextState = IDLE; endcase end always @(posedge rst or posedge clk) begin if (rst) state <= RESET; else state <= nextState; end endmodule тест module test_queue; localparam N = 8; localparam count =16; localparam cmdCount = 24; reg clk; reg reset; wire res; reg [3:0]rst_delay = 0; reg [8:0] cnt =0; reg writeCmd; reg readCmd; reg [N-1:0] data [count -1:0]; reg [N-1:0] writeData; wire [N-1:0] readData; reg [cmdCount -1 : 0] doWrite; reg [cmdCount -1 : 0] doRead; initial begin clk = 0; reset =0; data[0] = 1; data[1] = 2; data[2] = 3; data[3] = 4; data[4] = 5; data[5] = 6; data[6] = 7; data[7] = 8; data[8] = 101; data[9] = 3; data[10] = 6; data[11] = 55; data[12] = 3; data[13] = 2; data[14] = 0; data[15] = 1; doWrite = 24'b1101100111010011100; doRead = 24'b0010001101100111011; end always begin #10 clk = ~clk; end always @(posedge clk) begin rst_delay <= { rst_delay[2:0], 1'b1 }; doWrite[cmdCount -1 : 1] <= doWrite[cmdCount -2 : 0]; doRead[cmdCount -1 : 1] <= doRead[cmdCount -2 : 0]; writeCmd = doWrite[cmdCount -1]; readCmd = doRead[cmdCount -1]; writeData = data[cnt]; if (writeCmd) cnt = cnt + 1; end always @* reset = rst_delay[2]^rst_delay[3]; queue q(reset, clk, writeCmd, readCmd, writeData, readData); endmodule